Abstract

Electro-optic modulation at frequencies of 100 GHz and beyond is important for photonic-electronic signal processing at the highest speeds. To date, however, only a small number of devices exist that can operate up to this frequency. In this study, we demonstrate that this frequency range can be addressed by nanophotonic, silicon-based modulators. We exploit the ultrafast Pockels effect by using the silicon–organic hybrid (SOH) platform, which combines highly nonlinear organic molecules with silicon waveguides. Until now, the bandwidth of these devices was limited by the losses of the radiofrequency (RF) signal and the RC (resistor-capacitor) time constant of the silicon structure. The RF losses are overcome by using a device as short as 500 µm, and the RC time constant is decreased by using a highly conductive electron accumulation layer and an improved gate insulator. Using this method, we demonstrate for the first time an integrated silicon modulator with a 3dB bandwidth at an operating frequency beyond 100 GHz. Our results clearly indicate that the RC time constant is not a fundamental speed limitation of SOH devices at these frequencies. Our device has a voltage–length product of only VπL=11 V mm, which compares favorably with the best silicon-photonic modulators available today. Using cladding materials with stronger nonlinearities, the voltage–length product is expected to improve by more than an order of magnitude.

Similar content being viewed by others

Introduction

High-bandwidth electro-optic modulators are key components for a variety of applications such as photonic transceivers for long-haul and on-chip communications,1 radio-over-fiber links, low-noise microwave oscillators2 and optical frequency comb generation.3 However, achieving a small footprint, low power consumption, low modulation voltage and high-speed operation4,5 remains a challenge. Because unstrained silicon does not possess a χ(2)-nonlinearity,6 state-of-the art silicon photonic modulators mainly rely on free-carrier dispersion (a plasma effect) in pin or pn junctions.7,8,9 Reversed-biased pn junctions are intrinsically faster than forward-biased pin diodes7 and already enable 50 Gbit s−1 on–off keying with a voltage–length product of VπL=28 V mm.10 Unfortunately, such plasma-effect phase modulators produce undesired intensity modulation as well, and they respond nonlinearly to the applied voltage.

An alternative approach uses hybrid integration of III–V epitaxy stacks grown on InP substrates, which are subsequently transferred to silicon-on-insulator waveguides to create high-speed electro-absorption modulators.11 Recently, such a device demonstrated a 3dB bandwidth greater than 67 GHz, representing the fastest modulator realized on a silicon chip to date. Advanced modulation formats such as quadrature amplitude modulation, however, require phase modulators with a linear response and a pure phase modulation, rendering the electro-optic effect (Pockels effect12) particularly attractive. For low power consumption, devices with small capacitances are required, and leakage currents as well as driving voltages are to be minimized.13

In this study, we demonstrate for the first time an integrated, silicon electro-optic modulator with a 3-dB bandwidth larger than 100 GHz. The device has a voltage–length product of VπL=11 V mm, which is the smallest reported value to date for a high-speed silicon-based modulator. Our modulator exploits the linear Pockels effect, offers capacitances per device length as small as 100 fF mm−1, 13 and has a parasitic resistance of several GΩ.

Materials and methods

Silicon–organic hybrid (SOH) modulator

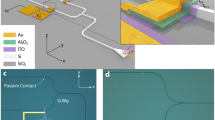

Our device is based on SOH technology. In an SOH modulator, the optical quasi-TE (transverse electric) field (dominant electric field parallel to the substrate plane) is guided by a silicon waveguide, while the electro-optic effect is provided by an organic cladding with a high χ(2)-nonlinearity (Pockels effect) as seen in Figure 1a. The optical nonlinear interaction occurs inside a nanoscale slot, taking advantage of the field enhancement caused by the lateral discontinuity of the refractive index as seen in Figure 1b. The external modulation voltage drops across the nanoscale slot because of the strip-load silicon electrodes, which must be both optically transparent and electrically highly conductive as seen in Figure 1a.

Schematic of an SOH modulator. (a) The silicon slot waveguide is connected to the metal electrodes by thin silicon strip-loads. The EO polymer cladding covers the waveguide and fills the slot. The shallowly doped silicon substrate is used as a gate. (b) The cross-section of the waveguide and the electric field distribution of the optical quasi-TE mode, where the light is concentrated in the slot. The figure also shows the equivalent RC circuit for the modulation voltage (slot capacitance C and strip-load resistance R). (c) When a positive gate voltage is applied across the 2-µm thick SiO2 substrate, a highly conductive electron accumulation layer forms in the strip-loads.17 The thickness of the strip-loads is 60 nm (not drawn to scale). The gate voltage Vgate bends the energy bands in the strip-loads.17 EF,C,V are the Fermi energy, conduction and valence band energy, respectively, and q is the elementary charge. EO, electro-optic; RC, resistor-capacitor; SOH, silicon–organic hybrid; TE, transverse electric.

To reduce the resistance of the silicon strip-loads, we exploit a highly conductive electron accumulation layer that is induced by an external direct current (DC) ‘gate’ voltage14 as seen in Figure 1c. In contrast to doping, the electron mobility is not impaired by impurity scattering; therefore, sheet resistances as low as 3 kΩ sq−1 can be obtained along with small optical losses.15 This is an important technique for achieving large modulation bandwidths and helps overcome the RC (resistor-capacitor) speed limitation so that the device’s speed is limited only by the frequency-dependent radiofrequency (RF) propagation losses.16

Device fabrication

The optical waveguides were fabricated by CEA-Leti based on standard processes used in the microelectronics industry.18 Silicon-on-insulator wafers were used, with 220-nm crystalline silicon on top of 2-µm silicon dioxide. The wafers were first n-doped (using arsenic) to reach a uniform ion concentration of 1017 cm−3 and the optical waveguide was defined using 193 nm and 248 nm deep ultraviolet lithography followed by etching with HBr gases.15 The width of the slot is 120 nm and the rail width is 240 nm. Although smaller slot widths would allow for smaller modulation voltages,13 we chose a width of 120 nm as a compromise between the yield and the modulation efficiency. To avoid any damage to the buried oxide (BOX), thereby enabling the use of high gate fields, we fabricated the electrode using a lift-off process. To this end, after defining the resist mask using contact lithography, the chips were submerged for 15 s in buffered hydrofluoric acid to remove the remaining oxide. Then, a Cr/Ag metal stack was deposited using an e-beam physical vapor deposition at a pressure of 10−6 mbar (5 nm of chromium, 400 nm of silver) and subsequently processed by lift-off after a 1-day acetone bath. We used electrodes with a length of only 500 µm to overcome the speed limitations caused by the frequency-dependent RF propagation losses, which were predicted to be as high as 6 dB mm−1 at 100 GHz.13

Because the RF propagation losses are mainly determined by the losses in the silicon strip-loads,13 the use of standard complementary metal–oxide–semiconductor (CMOS) metal stacks instead of silver (which is easy to process in a research lab) is not expected to impair the device's performance. The signal electrode width is 15 µm, the ground electrode width is 80 µm and the gap between the signal and the ground is 4 µm. The optically nonlinear polymer M3 (commercialized by Gigoptix, see Ref. 19) was spin-coated at 3000 r.p.m. for 30 s and poled at 167 °C for 3 s in a high vacuum (10−4 mbar), thereby obtaining an electro-optic coefficient of r33=18 pm V−1, which corresponds to a π-voltage of Vπ=22 V. The material M3 has been successfully tested by Telcordia.20 The fiber-to-fiber insertion loss of the device was (21±2) dB, 10 dB of which are attributed to the couplers21 and 11 dB to the remaining 2.6-mm-long waveguide, which is comprised of tapers, strip-to-slot converters22 and the strip-load slot waveguide. By comparing the loss of the waveguides on the same chip having different device lengths (cut-back method), we estimate the insertion loss of of the 500-µm-long device to be less than 2 dB. Activating the gate field increases the fiber-to-fiber insertion loss by (3±1) dB. This corresponds to an additional ∼0.5 dB for the 500-µm-long device (assuming that the excess loss is constant along the optical waveguide).

Frequency response measurement

To determine the frequency response of the device, we applied sinusoidal signals with frequencies fmod between 0.4 GHz and 100 GHz. We used three independent RF sources and calibrated electrical power meters (the RF sources/power sensors were a vector network analyzer Anritsu 37397C/Anritsu ML2438A in the 40 MHz–65 GHz range, HP 83557A/Agilent V8486A in the 50–75 GHz range and a HP 83558A/Agilent V8486A in the 75–100 GHz range). The chip was contacted with two Picoprobes (Models 67A GS/SG 50 P; GGB Industries Inc., Naples, USA) with a 50-µm pitch. For frequencies above 65 GHz, hollow-waveguide to 1-mm adapters, 1-mm cables and 1-mm connector to 1.85-mm connector (V-connector) adapters were used to connect the RF sources/power meters to the Picoprobes. Any multimode behavior of the Picoprobes beyond the specified range of 67 GHz could be excluded because we did not observe any oscillatory behavior in the electrical transmission. The chip was terminated with an external 50-Ω load. The losses of the RF cables and the Picoprobes were subtracted using a ceramic calibration substrate (CS-8; GGB Industries Inc., Naples, USA). The modulation index η (i.e., the amplitude of the sinusoidally varying phase shift) was extracted from the relative height of the sidebands recorded using an optical spectrum analyzer15 (Apex AP2050; APEX Technologies, Marcoussis, France). After verifying the linearity of the modulation index with respect to the applied modulation voltage, the modulation indices were rescaled to a reference 10 dBm RF power (1 V amplitude at an impedance of 50 Ω).

Results and discussion

The measured frequency response of the modulator is shown in Figure 2a and varies by less than 30% in the 100 GHz frequency range; in other words, if the device was mounted on one arm of a Mach–Zehnder interferometer, the 3-dB bandwidth of the modulator would be at least 100 GHz.

Modulation index η vs. frequency and gate field. The data are normalized to a 10 dBm launched power (1 V amplitude at a characteristic impedance of 50 Ω). (a) Phase modulation index η vs. frequency for a gate field of 0.2 V nm−1. The measured modulation frequency range is 0.4 GHz to 100 GHz. The horizontal dotted black lines represent the maximum value and 70.7% of the maximum value corresponds to a 3-dB bandwidth of at least 100 GHz. (b) Modulation index vs. gate field for selected modulation frequencies. Each curve reaches a plateau at high gate fields indicating that in this region, the charging of the slot capacitance is not limited by the strip-load resistance. RF, radiofrequency.

As we shall show, the RC time constant does not limit the device bandwidth. To this end, we monitored the modulation index as a function of the gate field εgate=Vgate/dBOX for three different modulation frequencies as seen in Figure 2b. As the gate field increases, the resistance of the strip-loads decreases because of the formation of the highly conductive accumulation layer. The modulation index reaches a plateau even at 90 GHz, indicating that the charging of the slot capacitance is not impeded by the strip-load resistance as seen in Figure 2b.

Next, we investigated the performance of the 500-µm-long silver electrodes using a vector network analyzer (Anritsu 37397C; Anritsu Corporation, Kanagawa, Japan) that operates in the range from 40 MHz to 65 GHz as seen in Figure 3. The system was calibrated such that the reference planes are located on the tips of the Picoprobes. The scattering matrix element S21 is defined to be the ratio of the voltages of the outgoing wave on the 50 Ω Picoprobe and the incoming wave; the reflection factor S11 is defined as the voltage ratio of the incoming and the outgoing wave at the same port. As the gate field is increased, the strip-loads become sufficiently conductive to quickly charge the slot capacitance, which leads to higher RF losses13 (decreasing transmission |S21|). After traveling along the 500-µm-long electrodes, the forward propagating wave at 65 GHz remains at 80% of the initial voltage amplitude. The spatially averaged modulation voltage is therefore approximately 90%, which is consistent with the measured optical response. The characteristic impedance increases slightly with frequency.13 Based on our vector network analyzer measurements, we extract a characteristic impedance of 40 Ω at 10 GHz and 50 Ω at 60 GHz for the maximum gate field. The slight oscillation visible both in the electrical (Figure 3) and in the optical response (Figure 2a) near the modulation frequency of 40 GHz is attributed to the slight impedance mismatch. With an earlier device generation,15 which had a similar π-voltage but a smaller bandwidth, we previously demonstrated a 42.7 Gbit s−1 data transmission rate with a bit error ratio of less than 3×10−10. The current device is expected to support on–off-keying data rates of up to 140 Gbit s−1. Furthermore, the half-wave voltage of Vπ=22 V can be reduced by a factor of 10 in future device generations as we recently demonstrated.23,24

Electrical S-parameters of the modulator. (a) Electrical transmission factor |S21| (voltage ratio). As the gate field increases from 0 V nm−1 to 0.1 V nm−1, the electrical loss increases at frequencies >10 GHz because of the increasing influence of the strip-loads.13 For even higher gate fields, the transmission is nearly independent of the gate voltage and is approximately |S21|=0.8 at 65 GHz, indicating that the RF is not unduly attenuated. (b) Electrical reflection factor |S11| (voltage ratio) for different gate fields. RF, radiofrequency.

Conclusions

We have demonstrated the first silicon hybrid phase modulator with a 3-dB bandwidth of at least 100 GHz. Using a gate voltage, we created an accumulation layer to reduce the resistance of the connecting silicon region between the electrodes and the optically active region. This reduces the RC time constant to a value where it does not limit the device’s bandwidth. Our device is very short (500 µm) and has a voltage–length product as low as VπL=11 V mm, a value which strongly competes with state-of-the-art, high-speed silicon modulators. The use of materials with a stronger nonlinearity can further improve this value by an order of magnitude.23,24

References

Shi ZW, Luo JD, Huang S, Polishak BM, Zhou XH et al. Achieving excellent electro-optic activity and thermal stability in poled polymers through an expeditious crosslinking process. J Mater Chem 2012; 22: 951–959.

Yao XS, Maleki L . Optoelectronic microwave oscillator. J Opt Soc Am B 1996; 13: 1725–1735.

Gheorma IL, Gopalakrishnan GK . Flat frequency comb generation with an integrated dual-parallel modulator. IEEE Photon Technol Lett 2007; 19: 1011–1013.

Chen DT, Fetterman HR, Chen AT, Steier WH, Dalton LR et al. Demonstration of 110 GHz electro-optic polymer modulators. Appl Phys Lett 1997; 70: 3335–3337.

Lee M, Katz HE, Erben C, Gill DM, Gopalan P et al. Broadband modulation of light by using an electro-optic polymer. Science 2002; 298: 1401–1403.

Jacobsen RS, Andersen KN, Borel PI, Fage-Pedersen J, Frandsen LH et al. Strained silicon as a new electro-optic material. Nature 2006; 441: 199–202.

Green WM, Rooks MJ, Sekaric L, Vlasov YA . Ultra-compact, low RF power, 10 Gb/s silicon Mach–Zehnder modulator. Opt Express 2007; 15: 17106–17113.

Liao L, Liu A, Rubin D, Basak J, Chetrit Y et al. 40 Gbit/s silicon optical modulator for high-speed applications. Electron Lett 2007; 43: 1196–1197.

Baehr-Jones T, Ding R, Liu Y, Ayazi A, Pinguet T et al. Ultralow drive voltage silicon traveling-wave modulator. Opt Express 2012; 20: 12014–12020.

Thomson DJ, Gardes FY, Fedeli JM, Zlatanovic S, Hu YF et al. 50-Gb/s silicon optical modulator. IEEE Photon Technol Lett 2012; 24: 234–236.

Tang YB, Peters JD, Bowers JE . Over 67 GHz bandwidth hybrid silicon electroabsorption modulator with asymmetric segmented electrode for 1.3 μm transmission. Opt Express 2012; 20: 11529–11535.

Boyd RW . Nonlinear Optics. Amsterdam: Academic Press; 2008.

Witzens J, Baehr-Jones T, Hochberg M . Design of transmission line driven slot waveguide Mach–Zehnder interferometers and application to analog optical links. Opt Express 2010; 18: 16902–16928.

Alloatti L, Lauermann M, Suergers C, Koos C, Freude W et al. Optical absorption in silicon layers in the presence of charge inversion/accumulation or ion implantation. Appl Phys Lett 2013; 103: 051104.

Alloatti L, Korn D, Palmer R, Hillerkuss D, Li J et al. 42.7 Gbit/s electro-optic modulator in silicon technology. Opt Express 2011; 19: 11841–11851.

Leuthold J, Freude W, Brosi JM, Baets R, Dumon P et al. Silicon organic hybrid technology—a platform for practical nonlinear optics. Proc IEEE 2009; 97: 1304–1316.

Sze SM, Ng KK . Physics of Semiconductor Devices. 3rd ed. New York: Wiley; 2006.

ePIXfab. http://www.epixfab.eu/ (accessed by CEA-Letion on 25 February 2014).

GigOptix. Bothell (WA). http://www.gigoptix.com (accessed by Bothell on 25 February 2014).

Dinu R, Jin D, Yu GM, Chen BQ, Huang DY et al. Environmental stress testing of electro-optic polymer modulators. J Lightwave Technol 2009; 27: 1527–1532.

ePIXfab. Vertical fiber couplers. http://www.epixfab.eu/technologies/imec-siphotonics/design-kit (accessed by CEA-Leti on 25 February 2014).

Palmer R, Alloatti L, Korn D, Heni W, Schindler PC et al. Low-loss silicon strip-to-slot mode converters. IEEE Photon J 2013; 5: 2200409.

Palmer R, Koeber S, Heni W, Elder DL, Korn D et al. High-speed silicon-organic hybrid (SOH) modulator with 1.6 fJ/bit and 180 pm/V in-device nonlinearity. In: Proceedings of the 39th European Conference on Optical Communication (ECOC) 2013; 22–26 September 2013; London, UK. ICC: London, We.3.B.3.

Dalton LR, Benight SJ, Johnson LE, Knorr DB, Kosilkin I et al. Systematic nanoengineering of soft matter organic electro-optic materials. Chem Mater 2011; 23: 430–445.

Acknowledgements

We acknowledge support by the DFG Center for Functional Nanostructures; the Helmholtz International Research School of Teratronics; the Karlsruhe School of Optics and Photonics; the EU-FP7 projects SOFI (grant 248609) and EURO-FOS (grant 224402); the BMBF joint project MISTRAL, which is funded by the German Ministry of Education and Research under grant 01BL0804; and the European Research Council (ERC Starting Grant ‘EnTeraPIC’, number 280145). We are grateful for technological support from the Karlsruhe Nano-Micro Facility, the Light Technology Institute (KIT-LTI), CEA-Leti fab within ePIXfab (grant 224232) and the ePIXfab (silicon photonics platform). We further acknowledge support from the EU FP7 project PHOXTROT, the Alfried Krupp von Bohlen und Halbach Foundation, Deutsche Forschungsgemeinschaft and the Open Access Publishing Fund of Karlsruhe Institute of Technology.

Author information

Authors and Affiliations

Corresponding authors

Rights and permissions

This work is licensed under a Creative Commons Attribution 3.0 Unported License. The images or other third party material in this article are included in the article's Creative Commons license, unless indicated otherwise in the credit line; if the material is not included under the Creative Commons license, users will need to obtain permission from the license holder to reproduce the material. To view a copy of this license, visit http://creativecommons.org/licenses/by/3.0/

About this article

Cite this article

Alloatti, L., Palmer, R., Diebold, S. et al. 100 GHz silicon–organic hybrid modulator. Light Sci Appl 3, e173 (2014). https://doi.org/10.1038/lsa.2014.54

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1038/lsa.2014.54

Keywords

This article is cited by

-

Dynamic light manipulation via silicon-organic slot metasurfaces

Nature Communications (2024)

-

Modelling, characterization, and applications of silicon on insulator loop terminated asymmetric Mach Zehnder interferometer

Scientific Reports (2022)

-

High Modulation Efficient Silicon MZM with Core-based Split PN Junction Phase Shifter

Silicon (2022)

-

Optical modulator using ultra-thin silicon waveguide in SOI hybrid technology

Optical and Quantum Electronics (2022)

-

Modelling and Analysis of a Corrugated PN Junction Phase Shifter in Silicon MZM

Silicon (2022)