# SCIENTIFIC **Reports**

Received: 19 February 2016 Accepted: 02 June 2016 Published: 21 June 2016

## **OPEN** Approaching Defect-free **Amorphous Silicon Nitride by Plasma-assisted Atomic Beam Deposition for High Performance Gate Dielectric**

Shu-Ju Tsai<sup>1</sup>, Chiang-Lun Wang<sup>2</sup>, Hung-Chun Lee<sup>2</sup>, Chun-Yeh Lin<sup>2</sup>, Jhih-Wei Chen<sup>2</sup>, Hong-Wei Shiu<sup>3</sup>, Lo-Yueh Chang<sup>3</sup>, Han-Ting Hsueh<sup>4</sup>, Hung-Ying Chen<sup>5</sup>, Jyun-Yu Tsai<sup>6</sup>, Ying-Hsin Lu<sup>6</sup>, Ting-Chang Chang<sup>6</sup>, Li-Wei Tu<sup>6</sup>, Hsisheng Teng<sup>7</sup>, Yi-Chun Chen<sup>2</sup>, Chia-Hao Chen<sup>3</sup> & Chung-Lin Wu<sup>2</sup>

In the past few decades, gate insulators with a high dielectric constant (high-k dielectric) enabling a physically thick but dielectrically thin insulating layer, have been used to replace traditional SiO, insulator and to ensure continuous downscaling of Si-based transistor technology. However, due to the non-silicon derivative natures of the high-k metal oxides, transport properties in these dielectrics are still limited by various structural defects on the hetero-interfaces and inside the dielectrics. Here, we show that another insulating silicon compound, amorphous silicon nitride ( $\alpha$ -Si<sub>3</sub>N<sub>4</sub>), is a promising candidate of effective electrical insulator for use as a high-k dielectric. We have examined  $\alpha$ -Si<sub>3</sub>N<sub>4</sub> deposited using the plasma-assisted atomic beam deposition (PA-ABD) technique in an ultra-high vacuum (UHV) environment and demonstrated the absence of defect-related luminescence; it was also found that the electronic structure across the  $\alpha$ -Si<sub>3</sub>N<sub>4</sub>/Si heterojunction approaches the intrinsic limit, which exhibits large band gap energy and valence band offset. We demonstrate that charge transport properties in the metal/ $\alpha$ -Si<sub>3</sub>N<sub>x</sub>/Si (MNS) structures approach defect-free limits with a large breakdown field and a low leakage current. Using PA-ABD, our results suggest a general strategy to markedly improve the performance of gate dielectric using a nearly defect-free insulator.

The challenge of finding a high quality gate dielectric on silicon and prospective 2D materials that exhibits ultrathin equivalent oxide thickness (EOT) and low interface defect density has been a fundamental problem that must be solved in order to continue to meet Moore's law in the present semiconductor and post-silicon electronics. Insulators with high dielectric constants allow a high capacitance with a thicker film that reduces the direct tunneling leakage current. Recently, a wide variety of metals oxides (for example, HfO<sub>2</sub>, TiO<sub>2</sub>, Al<sub>2</sub>O<sub>3</sub>, La<sub>2</sub>O<sub>3</sub>, Ta<sub>2</sub>O<sub>5</sub>, and SrTiO<sub>3</sub>) have been considered as possible replacements of SiO<sub>2</sub><sup>1-5</sup>. However, these non-Si-based dielectrics generally exhibit poor interfaces with silicon that can markedly degrade the gate dielectric performance, thus need to consist a very thin SiO<sub>2</sub> to reduce the interfacial defect density near the substrate<sup>6</sup>. Therefore, the use of an amorphous- phased silicon-based derivative is more realistic for the complete replacement of amorphous  $SiO_2$  in the gate dielectric. Amorphous silicon nitride (a-Si<sub>3</sub>N<sub>4</sub>) is one such material with a dielectric constant that is approximately twice the dielectric constant of SiO<sub>2</sub>, and has excellent mechanical, thermal, and electronic

<sup>1</sup>Center for Micro/Nano Science and Technology, National Cheng Kung University, Tainan 70101, Taiwan. <sup>2</sup>Department of Physics, National Cheng Kung University, Tainan 70101, Taiwan. <sup>3</sup>National Synchrotron Radiation Research Center, Hsinchu 30076, Taiwan. <sup>4</sup>National Nano Devices Laboratories, National Applied Research Laboratories, Tainan 741, Taiwan. <sup>5</sup>Department of Physics, National Tsing-Hua University, Hsinchu 30013, Taiwan. <sup>6</sup>Department of Physics, National Sun Yat-Sen University, Kaohsiung 804, Taiwan. <sup>7</sup>Department of Chemical Engineering, National Cheng Kung University, Tainan 70101, Taiwan. Correspondence and requests for materials should be addressed to S.-J.T. (email: phoebe@mail.ncku.edu.tw) or C.-L.W. (email: clwuphys@mail.ncku.edu.tw)

insulating properties<sup>7,8</sup>. Besides, a-Si<sub>3</sub>N<sub>4</sub> has been demonstrated recently for an attractive alternative for 2D material field-effect transistors (FETs)<sup>9-11</sup> because it shows less degradation on channel mobility compared to SiO<sub>2</sub><sup>12</sup> and HfO<sub>2</sub><sup>13</sup>. Therefore, the improvement in EOT downscaling for Si<sub>3</sub>N<sub>4</sub> is critical to be implemented for future generation of transistors. A thorough understanding of the conventional a-Si<sub>3</sub>N<sub>4</sub> deposition process is required to find out the solution for lower EOT.

In traditional chemical vapor deposition (CVD) processes of a-Si<sub>3</sub>N<sub>4</sub>, the hydrogen/oxygen-radicals create an inherently large concentration of defects and thus lead to dielectric charging, which in turn governs either the operation or time-dependent performance degradation in gate dielectrics<sup>14-16</sup>. Therefore, a new option of deposition method should be available through an ultra-high vacuum (UHV) physical deposition process: in an extremely pure and hydrogen-free environment that contains only the constituent elements (Si, N) for a-Si<sub>3</sub>N<sub>4</sub> deposition, and has extendibility to very large substrates with carefully source-substrate geometry design for both Si and N atoms having good uniformity of arrival rate over entire substrate area. Here, we demonstrate a-Si<sub>3</sub>N<sub>4</sub> prepared via a one-step (without a post-annealing process), two atomic beams (Si evaporated beam and N<sub>2</sub>-plasma) method called plasma-assisted atomic beam deposition (PA-ABD) for use as a long expected and versatile insulating layer that meets a wide range of requirements for high-performance gate dielectrics. We show that the use of PA-ABD enables the formation of an atomically abrupt interface and a smooth surface  $a-Si_3N_4/Si$ heterojunction with excellent insulating properties such as a large dielectric band gap ( $\sim 6 \text{ eV}$ ) and large heterojunction valence/conduction band offset (VBO/CBO) values for blocking mobile carriers while applying gate voltage. Consequently, under the current-voltage (I-V) characteristic measured on the metal/a-Si<sub>3</sub>N<sub>4</sub>/Si (MNS) heterostructure, the nearly defect-free nature inherent to the UHV PA-ABD process shows the scalability of the high-quality *a*-Si<sub>3</sub>N<sub>4</sub> insulating layer with a large breakdown field and a low leakage current.

#### Results

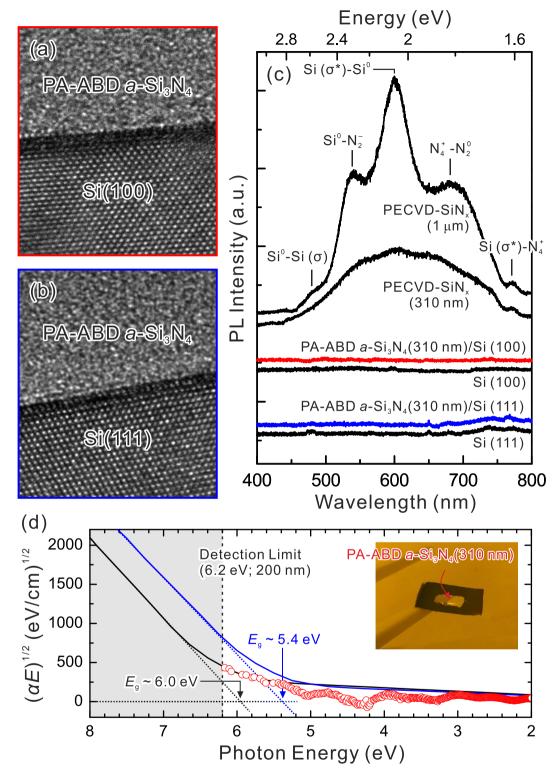

The cross-sectional high-resolution transmission electron microscopy (HR-TEM) images show that atomically abrupt amorphous/crystalline hetero-interfaces are formed on the reconstructed Si (111) surface (Fig. 1b) and the unreconstructed Si (100) surface (Fig. 1a), indicating higher electronic performance of the a-Si<sub>3</sub>N<sub>4</sub>/Si heterojunction resulting from the lower density of interface traps. We then focused on measuring the defects states inside the a-Si<sub>3</sub>N<sub>4</sub> layer that directly determine the electronic properties; this was performed with room-temperature photoluminescence (PL) using a 325 nm excitation light source from a He-Cd laser. The PL spectra shown in Fig. 1c can characterize the electronic density of defect states and provide information about chemical bonding and the composition of defects. For comparison, a-SiN<sub>x</sub> films deposited by conventional plasma-enhanced chemical vapor deposition (PECVD) with thicknesses of 1 µm and 310 nm are shown, exhibiting strong PL emission for wavelengths in the 450-800 nm range, that arises the electronic transition between gap in states of Si-Si and N-N bonds, and Si and N dangling bonds<sup>17-19</sup>. The 1-µm-thick a-SiN<sub>x</sub> showed clear peaks at about 2.6 eV<sup>17</sup>, 2.3 eV<sup>17,19</sup>, 2.1 eV<sup>17</sup>, 1.8 eV<sup>17</sup>, and 1.6 eV<sup>17</sup>, that are associated with the defect optical transitions of Si<sup>0</sup>-Si( $\sigma$ ), Si<sup>0</sup>-N<sub>2</sub><sup>-</sup>, Si( $\sigma^*$ )  $-Si^0$ ,  $N_4^+ - N_2^0$ , and  $Si(\sigma^*) - N_4^+$ , respectively. In contrast to the strong defect emissions from the typical PECVD grown a-SiN<sub>x</sub>, the PL spectra from the PA-ABD grown a-Si<sub>3</sub>N<sub>4</sub> on both (111) and (100) substrates are almost identical to the PL spectra of their substrates, demonstrating that the electrically active defects with atomic configurations that give rise to the electronic states in the a-Si<sub>3</sub>N<sub>4</sub> band gap was substantial reduced by the absence of Si-H and N-H bonding during deposition<sup>20</sup>.

Furthermore, due to the presence of the gap states, a-SiN<sub>x</sub> films grown by PECVD methods exhibit varying optical band gaps from about 2.4 eV to 5.4 eV, depending on the film composition process<sup>17,21,22</sup>. Thus, naturally, it is interesting to know whether the optical band gap of PA-ABD a-Si<sub>3</sub>N<sub>4</sub> can be further increased if the defects that generate the gap states are almost entirely absent. Two optical measurements, transmission for the PA-ABD a-Si<sub>3</sub>N<sub>4</sub> membrane and reflection for both PA-ABD a-Si<sub>3</sub>N<sub>4</sub> and PECVD a-SiN<sub>x</sub> (shown in Supplementary Fig. S1), were used to determine the optical band gaps. The PA-ABD a-Si<sub>3</sub>N<sub>4</sub> membrane was fabricated by etching away the  $2 \times 4 \text{ mm}^2$  area of the Si (100) substrate using a 49% KOH solution at 120 °C, as shown in the inset of Fig. 1d, followed by the measurement of the transmission (T) with a UV-Visible spectrophotometer. The optical band gap can be determined by plotting the absorption coefficient ( $\alpha$ ) against the photon energy (eV) and taking the intercept of the extrapolation to zero absorption with the photon energy axis (dashed lines in Fig. 1d). The detection limit of the spectrophotometer is 6.2 eV of photon energy, where the dramatic increase of absorption necessary for obtaining the intercept does not appear for PA-ABD a-Si<sub>3</sub>N<sub>4</sub>. Thus, absorption for the high photon energy region (>6.2 eV) is obtained by fitting the experimental PA-ABD a-Si<sub>3</sub>N<sub>4</sub> data (red circles) with a blue shift of about 0.6 eV for the band gap  $(E_g)$  of 5.4 eV of the well-known a-SiN<sub>x</sub><sup>23</sup>. Reflectivity measurements were carried out to determine that the Eg for PECVD a-SiNx is 3.1 eV for the comparison shown in Fig. 1d. Moreover, the  $E_g$  of PA-ABD a-Si<sub>3</sub>N<sub>4</sub> is determined to be about 6.0 eV, which is consistent with the value obtained by both transmission and reflection measurements (see Supplementary Fig. S1); to the best of our knowledge, this value is closest to the theoretical  $E_g = 6.77 \text{ eV}$  of the crystalline  $\beta$ -Si<sub>3</sub>N<sub>4</sub> with no near band-edge states attributed to the N- or Si-dangling bonds extending from the CB or VB to reduce the  $E_g^{24,25}$ .

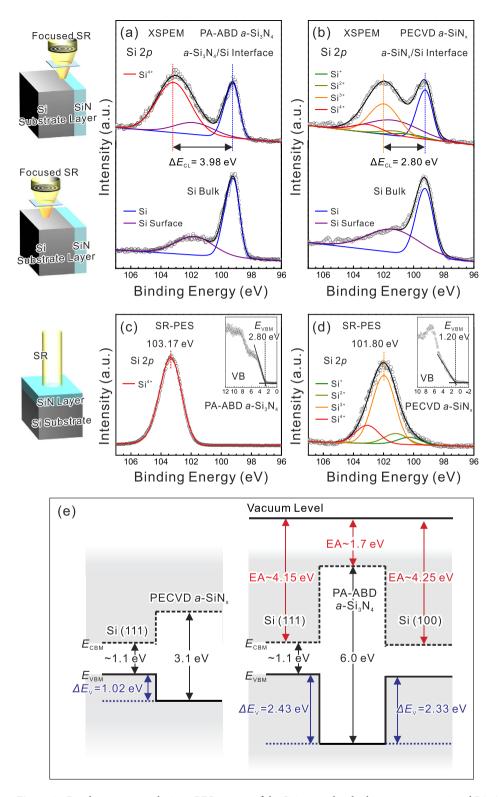

Even if the nearly defect free structure is known, the connection between the atomically abrupt amorphous/ crystalline interface at the a-Si<sub>3</sub>N<sub>4</sub>/Si heterojunction and its electronic structure is neither direct nor obvious. To directly visualize the electronic structure at the amorphous/crystalline hetero-interface, scanning photoelectron microscopy and spectroscopy (SPEM/S, National Synchrotron Radiation Research Center (NSRRC), Hsinchu, Taiwan) was used to provide the required spatial resolution (~sub-µm) for chemical mapping and the energy resolution (~50 meV) for localized photoelectron spectroscopy (µ-PES) on the cross-sectional a-Si<sub>3</sub>N<sub>4</sub>/Si(111) sample, here called cross-sectional SPEM (XSPEM). In particular, the Si (111) substrate enables *in situ* cleavage under an UHV environment for obtaining clean (no SiO<sub>x</sub> layer) and smooth exposure surface (i.e., the (100) plane), as schematically shown in the left panel of Fig. 2. The  $\mu$ -PES spectra taken from the hetero-interface region at different cross-sectional surfaces of the PA-ABD a-Si<sub>3</sub>N<sub>4</sub>/Si(111) and the PECVD a-SiN<sub>x</sub>/Si(111) heterojunctions are

**Figure 1.** TEM, PL, and optical  $E_g$  characterizations: (**a**,**b**) are cross-sectional HRTEM images of PA-ABD a-Si<sub>3</sub>N<sub>4</sub> grown on Si (100) and Si (111) substrates with pre-treatment at high temperature (600 °C) and lower temperature (950 °C), respectively. (**c**) Room temperature PL spectra for the PA-ABD a-Si<sub>3</sub>N<sub>4</sub>/Si (100) (red), the PA-ABD a-Si<sub>3</sub>N<sub>4</sub>/Si (111) (blue), the PECVD a-SiN<sub>x</sub>/Si (111) and bare Si (100) and Si (111) substrates (black curve). (**d**) Optical  $E_g$  measurement of PA-ABD a-Si<sub>3</sub>N<sub>4</sub> with red circles for experimental data, black curve for fitting) by UV-visible absorption spectra. The blue curve is previously reported data for the stoichiometric a-Si<sub>3</sub>N<sub>4</sub><sup>23</sup>. The inset is the photo of the PA-ABD a-Si<sub>3</sub>N<sub>4</sub> membrane for the transmission measurement.

**Figure 2.** Band structure analysis:  $\mu$ -PES spectra of the Si 2p core-level taken on cross-sectional PA-ABD a-Si<sub>3</sub>N<sub>4</sub>/Si(111) (**a**) and PECVD a-SiN<sub>x</sub>/Si(111) (**b**) samples for clean interface and bulk regions. SR-PES spectra of the Si 2p core-level taken on PA-ABD a-Si<sub>3</sub>N<sub>4</sub> (**c**) and PECVD a-SiN<sub>x</sub> (**d**) surfaces for obtaining energy differences between the Si 2p core-level and the valence-band maxima ( $E_{\rm CL}$ - $E_{\rm VBM}$ ). Schematic illustration of the XSPEM and SR-PES on the PA-ABD a-Si<sub>3</sub>N<sub>4</sub>/Si(111) and PECVD a-SiN<sub>x</sub>/Si(111) samples are included in the left panel of the Figure. The corresponding decomposition of Si 2p states for a-Si<sub>3</sub>N<sub>4</sub> and a-SiN<sub>x</sub> are also shown. The leading edges of valence bands for determining  $E_{\rm VBM}$  from a-Si<sub>3</sub>N<sub>4</sub> and a-SiN<sub>x</sub> can be observed in the insets of (**c**,**d**), respectively. The black dots are the experimentally spectral data points and color lines are the curve-fitting results. (**e**) The schematic energy band diagram of a-SiN<sub>x</sub>/Si(111), a-Si<sub>3</sub>N<sub>4</sub>/Si(111), and a-Si<sub>3</sub>N<sub>4</sub>/Si(100) based on the measured values of  $\Delta E_{\rm CL}$ ,  $E_{\rm CL}$ - $E_{\rm VBM}$ , in (**a**-**d**), and the crystalline orientated EA value of Si bulk.

shown in Fig. 2a,b, respectively. The differences in Si 2*p* core-levels between  $a-Si_3N_4$ ,  $a-SiN_x$ , and the Si substrate can be analyzed by curve fitting using Voigt functions. For stoichiometric  $a-Si_3N_4$  grown by PA-ABD, we find that the main chemical component of silicon nitride is the stoichiometric  $3^{4+}$  valence state without the subnitride state, and one extra surface component in the low binding energy side is added to bulk silicon to obtain reasonably good fits<sup>26</sup>. Compared to PA-ABD  $a-Si_3N_4$ , one of the main differences in PECVD  $a-SiN_x$  is that it involves various subnitride components in the Si 2*p* spectrum and reveals its non-stoichiometric nature. The Si<sup>3+</sup> component dominates in the Si 2*p* core-level spectrum because the hydrogen-containing nitridation process of PECVD results in incomplete nitridation and structural defects, leading to a binding energy shift of 2.80 eV relative to the energy reference of bulk Si<sup>27,28</sup>. The remaining subnitride components of Si<sup>4+</sup>, Si<sup>2+</sup>, and Si<sup>+</sup> show shifts of 3.80, 1.90, and 1.00 eV, respectively<sup>29,30</sup>. In summary, according to the best spectral fit, the deconvoluted Si 2*p* core-level spectra clearly indicate a huge deviation in the binding energy difference between Si 2*p* bulk and stoichiometric *a*-Si<sub>3</sub>N<sub>4</sub> and non-stoichiometric *a*-SiN<sub>x</sub> core-level emissions of about 1.2 eV ( $\Delta E_{CL}(a-Si_3N_4) = 3.98$  eV and  $\Delta E_{CL}(a-SiN_x) = 2.80$  eV).

To determine the valence band offset (VBO) values of different silicon-nitride/Si heterojunctions, it is necessary to measure the binding energy differences ( $E_{\rm CL} - E_{\rm VBM}$ ) of the dominant Si core-level with respect to the corresponding valence band maximum (VBM) positions in a-Si<sub>3</sub>N<sub>4</sub> and a-SiN<sub>x</sub> films. The measured  $E_{CL} - E_{VBM}$ value of PA-ABD a-Si<sub>3</sub>N<sub>4</sub> is about 100.37 eV (Fig. 2c), and that for PECVD a-SiN<sub>x</sub> is about 100.60 eV (Fig. 2d), both samples were contamination and native-oxide free following chemical cleaning by diluted HF solutions and then rinsing with deionized water. In combination with the measured  $E_{\rm CL} - E_{\rm VBM}$  value of the Si substrate of about 98.82 eV (shown in Supplementary Fig. S2), which is a material constant, the VBO values can be determined using the relation  $\Delta E_{\rm V} = (E_{\rm CL} - E_{\rm VBM})$ Si  $- (E_{\rm CL} - E_{\rm VBM})$ SiN  $+ (\Delta E_{\rm CL})$ SiN/Si, resulting in type-I VBOs of 2.43 eV and 1.02 eV for the PA-ABD a-Si<sub>3</sub>N<sub>4</sub>/Si (111) and the PECVD a-SiN<sub>x</sub>/Si (111) heterojunction (Fig. 2e), respectively. Taking the band gap values of a-Si<sub>3</sub>N<sub>4</sub> and a-SiN<sub>x</sub> to be equal to 6.0 eV and 3.1 eV, respectively, the nearly symmetry in band alignment (VBO = 2.43 and CBO = 2.47) of the a-Si<sub>3</sub>N<sub>4</sub>/Si (111) heterojunction is shown in Fig. 2e, indicating the absence of defects exhibits large VBO/CBO values. Moreover, the VBO of the a-Si<sub>3</sub>N<sub>4</sub>/Si (100) heterojunction can be obtained by using the crystalline dependent electron affinity (EA) value of the bulk Si, which is ~4.15 eV for Si (111) and ~4.25 eV for Si (100)<sup>31,32</sup>. As illustrated in Fig. 2e, by aligning the vacuum levels of Si (111), Si(100), and a-Si<sub>3</sub>N<sub>4</sub>, the VBO of the a-Si<sub>3</sub>N<sub>4</sub>/Si(100) heterojunction can be determined to be 2.33 eV, implying an EA of about 1.7 eV for a-Si<sub>3</sub>N<sub>4</sub>, similar to the previously reported value of  $1.8 \pm 0.1$  eV<sup>33</sup>

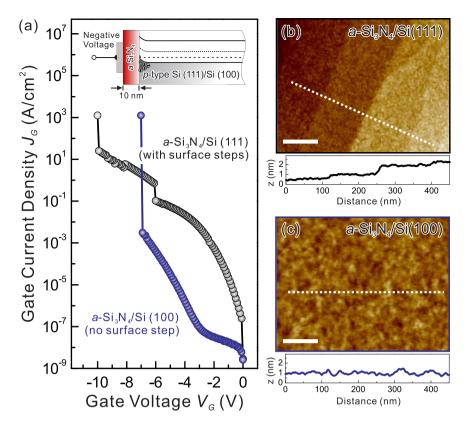

The obtained PA-ABD *a*-Si<sub>3</sub>N<sub>4</sub>/Si heterojunction offers a nitride dielectric with insulating properties that have significant implications for application in electronic devices in that it can provide a sufficient energy barrier for both electron and hole injection. However, as shown in Fig. 3a, the leakage current characteristics of the metal/10-nm-thick *a*-Si<sub>3</sub>N<sub>4</sub> (insulator)/Si(111) (MNS) structure having the desired high band offset and low interfacial defect states are highly unfavorable; namely, the leakage current is quite high for the *a*-Si<sub>3</sub>N<sub>4</sub>/Si(111) heterojunction with smooth surface morphology compared with atomic surface step (shown in Fig. 3b). Recently, large-scale molecular dynamics (MD) simulations have been performed to study the structure, dynamics, and mechanical behavior of the *a*-Si<sub>3</sub>N<sub>4</sub>/Si(111) heterostructure<sup>34,35</sup>. The *a*-Si<sub>3</sub>N<sub>4</sub> exhibits stress nano-domains at the interface with Si (111), which would result in uneven dopant distribution that is then transferred into the *a*-Si<sub>3</sub>N<sub>4</sub> layer with a thickness on the order of few nm. The observation of a large leakage current of MNS on a Si (111) substrate is in good support of the large-scale MD predictions that the interfacial stress pattern leads to the formation of a dopant pattern in the entire thin *a*-Si<sub>3</sub>N<sub>4</sub> layer, which is indeed a problem for using *a*-Si<sub>3</sub>N<sub>4</sub> as a good gate dielectric.

To avoid stress pattern formation and match the Si industry requirement of a Si (100) crystalline substrate, the MNS structure with 10-nm-thick a-Si<sub>3</sub>N<sub>4</sub> was prepared on a Si (100) substrate by PA-ABD, showing a surface roughness (~0.13 nm, shown in Fig. 3c ) identical to that of a-Si<sub>3</sub>N<sub>4</sub> grown on Si (111). As seen in Fig. 3a, the leakage characteristics of MNS on Si (100) substrate show great improvement with a leakage reduction of about 5 orders of magnitude compared to the MNS on Si (111) at -3 V. Moreover, this voltage ramp test indicates that the  $J_{\rm G}$  of the MNS structure with 10-nm-thick a-Si<sub>3</sub>N<sub>4</sub> can be maintained up to a breakdown field ( $E_{\rm BD}$ ) as high as 7 MV/cm, before it begins to exhibit breakdown at about -7 V. In addition, the  $E_{\rm BD}$  was 7~8.3 MV/cm for thicker layers of PA-ABD a-Si<sub>3</sub>N<sub>4</sub> (10~50 nm, shown in Supplementary Fig. S3), and the lower breakdown field of the PA-ABD a-Si<sub>3</sub>N<sub>4</sub> (k=7.8) compared to that of 15 MV/cm for SiO<sub>x</sub> (k=3.9) is in good agreement with an approximate  $E_{\rm BD} \sim k^{-1/2}$  dependence<sup>36</sup>.

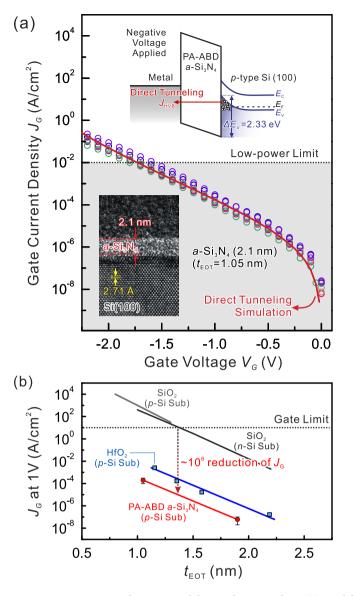

To further elucidate the insulating properties of the ultrathin PA-ABD a-Si<sub>3</sub>N<sub>4</sub> layer, its charge transport mechanism was investigated by measuring  $J_{\rm G} - V_{\rm G}$  characteristics using the MNS device with 2.1 nm-thick a-Si<sub>3</sub>N<sub>4</sub> layers (equivalent oxide thickness (EOT) =  $t \times (k_{SiOx}/k_{a-Si3N4}) = 1.05$  nm, where t is thickness and  $k_{SiOx} = 3.9$ ). The EOT values shown in Fig. 4 were also confirmed by capacitance-voltage measurements on the MNS devices. The  $J_{\rm G} - V_{\rm G}$  characteristics of seven MNS devices (Fig. 4a) over a negative  $V_{\rm G}$  range from 0 to -2.5 V are all well matched with the direct hole tunneling from valence band (HVB) model with the large VBO = 2.33 eV (shown in Fig. 2e for the a-Si<sub>3</sub>N<sub>4</sub>/Si(100) heterojunction) and  $m_h^* = 0.77$ , indicating that charge transport through the a-Si<sub>3</sub>N<sub>4</sub> layer is governed by tunneling and can be observed only when the defect density is sufficiently low so that thermally assisted conduction is suppressed significantly. This leads to a remarkable reduction of the  $J_{\rm G}$  of the ultrathin a-Si<sub>3</sub>N<sub>4</sub> by 4 orders of magnitude compared with  $J_G$  values reports for other a-SiN<sub>x</sub> films and enables a wider  $V_{\rm G}$  range for low-power operation<sup>37,38</sup>. Furthermore, no breakdown of PA-ABD *a*-Si<sub>3</sub>N<sub>4</sub> for 2.1 nm is caused by the tunneling currents flowing though the dielectric due to direct tunneling, thus lowering the strength of the local electric field in the dielectric layer. Moreover, the observation of no breakdown for ultrathin PA-ABD  $a-Si_3N_4$  is a signature of the relatively low trap/defect density in the dielectric and the superior smoothness and uniformity at the a-Si<sub>3</sub>N<sub>4</sub>/Si interface, that prevent the formation of the conduction path across the dielectric for breakdown<sup>39,40</sup>. Additionally, the gate leakage  $J_G$  of the MNS structure as a function of EOT for the *a*-Si<sub>3</sub>N<sub>4</sub> layer thickness at 1 V is plotted in Fig. 4b with conventionally used dielectrics of SiO<sub>2</sub> and HfO<sub>2</sub> for comparison,

**Figure 3.** Leakage current and surface morphology characterizations: (a) Leakage gate current densities and breakdown fields for the 10-nm thick PA-ABD *a*-Si<sub>3</sub>N<sub>4</sub> grown on Si (111) (black curve) and Si (100) (blue curve). The top inset is the schematic energy band diagram of the MNS capacitor with a *p*-type substrate for a negative gate bias. The AFM images taken on the corresponding *a*-Si<sub>3</sub>N<sub>4</sub> layers with (**b**) and without (**c**) surface steps grown on Si (111) and Si (100), respectively. The average height profiles are shown below the images and the scale bars indicate for 100 nm of length.

·

clearly indicating that the  $J_G$  value of a-Si<sub>3</sub>N<sub>4</sub> is a factor of 10<sup>6</sup> and 10<sup>1</sup>~10<sup>3</sup> lower than that of SiO<sub>x</sub><sup>41</sup> and HfO<sub>2</sub><sup>42,43</sup> at the same EOT, respectively. The extrapolation of leakage currents  $J_G$  suggests that a-Si<sub>3</sub>N<sub>4</sub> with an EOT of 0.9 and 0.5 nm could replace SiO<sub>x</sub> for 7 nm of physical gate length (18-nm node) of low standby power and high power devices, respectively<sup>1,44</sup>. These observations support of the hypothesis that the hydrogen-free nature of PA-ABD process leaves no N-H residues in the final a-Si<sub>3</sub>N<sub>4</sub> films thus making them less prone to defect formation. Furthermore, the EOT downscaling to 0.5 nm and wafer-scale fabrication capabilities of PA-ABD a-Si<sub>3</sub>N<sub>4</sub> will provide an ideal dielectric platform with defect-free nature for future 2D materials-based electronics owning to higher channel mobility compared to intrinsically defect-containing SiO<sub>2</sub><sup>9-11</sup> and other high-*k* metal oxides, such as HfO<sub>2</sub><sup>45</sup>, ZrO<sub>2</sub><sup>46</sup>, and Y<sub>2</sub>O<sub>3</sub><sup>47</sup>.

#### Discussion

In summary, to our knowledge, this work is the first demonstration of the defect-free a-Si<sub>3</sub>N<sub>4</sub> insulating layer for use as a gate dielectric on Si with an extremely large band gap energy and a low leakage current. Based on the precise control of thickness, residual-free nature, reacted-element-only environment, and low thermal budget, the PA-ABD growth technique can meet the requirements such as ultrathin film thickness demanded by emerging nano-CMOS transistors, especially taking into account the good barrier nature of silicon nitride for boron dopant penetration. Moreover, PA-ABD a-Si<sub>3</sub>N<sub>4</sub> is promising for complete replacement of SiO<sub>2</sub> in the gate stack due to the same natural advantages offered to the industry by the extremely low interface/interlayer defect density.

### Methods

**Silicon nitride deposition.** We grew a-Si<sub>3</sub>N<sub>4</sub> first on Si (111) and then on Si (100) 2-inch wafer substrates; both substrates were *p*-type with a resistivity of 5–10  $\Omega$ cm. The wafers were cleaned by a standard RCA clean procedure, and dilute HF etching was then used to remove surface contaminations and the native oxide on the Si surface. The cleaned Si wafers were loaded into an ultra-high-vacuum (UHV) chamber (less than  $1 \times 10^{-10}$  torr) equipped with a reflection high-energy electron diffraction (RHEED) system for *in-situ* determination of the surface atomic structure, a conventional thermally heated effusion cell for Si, and a radio-frequency (rf) plasma source for nitrogen. Remarkably, preparing the Si (111) surface by typical chemical wet etching and subsequent annealing at 950 °C in the UHV environment leads to the formation of the  $7 \times 7$  surface reconstructed structure, and Si (100) surface leads to the formation of the  $1 \times 1$  surface structure under subsequent annealing at 600 °C, where both determined surface structures agree with the lack of bonds to surface contaminants. Subsequently,

**Figure 4.** Gate current densities modeling and EOT analysis: (**a**) Model the gate current densities for 2.1 nm of PA-ABD *a*-Si<sub>3</sub>N<sub>4</sub> on the *p*-type Si (100) substrate with dots for experimental data and with red curve for the model of direct tunneling. The top inset is the energy band diagram of the MNS capacitor with a *p*-type substrate for a negative gate bias, and the bottom inset is cross sectional HR TEM image. (**b**) Plot of leakage current density at 1V of gate voltage versus EOT for SiO<sub>2</sub><sup>41</sup>, HfO<sub>2</sub><sup>42,43</sup>, and PA-ABD *a*-Si<sub>3</sub>N<sub>4</sub> for comparison, and PA-ABD *a*-Si<sub>3</sub>N<sub>4</sub> shows a significant leakage current reduction. The criteria of low power limit and gate limit of leakage current densities are taken from previous reports<sup>1,44</sup>.

the PA-ABD *a*-Si<sub>3</sub>N<sub>4</sub> films were deposited upon both the (111) and (100) substrates at 550 °C with N atomic beam by using an rf-plasma source of pure nitrogen gas ( $2 \times 10^{-5}$ torr) with a power of 550 W, with Si atomic beam with flux at  $5 \times 10^{-9}$ torr, and with a low growth rate of about 0.1 nm/min. The PECVD a-SiNx (Oxford Plasmalab System 100) is grown at 300 °C substrate temperature, at 25 W of rf power, at 800/25/8 sccm of N<sub>2</sub>/SiH<sub>4</sub>/NH<sub>3</sub> flow, and at a pressure of 1 torr.

**Characterization of silicon nitride band gap.** Photoluminescence (PL) spectra were performed with a spectrometer (LabRAM HR, Jobin Yvon), and transmission and reflection measurement were using a UV-Visible spectrophotometer (U-4100, Hitachi High-Tech. Corp.). The PA-ABD a-Si<sub>3</sub>N<sub>4</sub>/Si (111) with pretreatment at high temperature and PECVD a-SiN<sub>x</sub> are not resist to KOH, and thus not able to perform the transmission experiment on these samples. The optical band gap was determined from the expression given by Tauc for amorphous materials:<sup>48</sup>

$$\alpha h \nu = \left( h \nu - E_g \right)^2 \tag{1}$$

where  $\alpha$  is the absorption coefficient given by  $\alpha = 2.303 \times \log(T/d)$  (d is the thickness of PA-ABD *a*-Si<sub>3</sub>N<sub>4</sub>), hv is incident photon energy, and  $E_g$  the optical band gap.

Scanning photoelectron spectroscopy/microscopy characterization:

The SPEM/S system used here utilizes a combination of a Fresnel zone plate and an order-sorting aperture to focus the monochromatic (380 eV) soft x-ray with a beam size of about 100-200 nm. By setting the electron collecting energy window of the multiple-channel hemispherical electron energy analyzer while scanning the *a*-Si<sub>3</sub>N<sub>4</sub>/Si(111) heterojunction, a two-dimensional distribution of that particular core-level can be mapped. After acquiring the SPEM images, the focused beam was moved to specific locations to perform high-energy-resolution (~50 meV), microscopic-area photoelectron spectroscopy (µ-PES).

**Device fabrication.** The MNS capacitors were fabricated by depositing 50 nm Ti/150 nm Au on silicon nitride as top gate electrode using a shadow mask with an area of  $\sim$ 5000  $\mu$ m<sup>2</sup>. Then, the backside of p-Si substrate was polished to remove native oxide and 200 nm Pt was deposited as bottom electrode.

**Electrical characterization of MNS structure.** Leakage current densities for PA-ABD a-SiNx were measured on metal-insulator-semiconductor (MNS) capacitors using a semiconductor parameter analyzer (B1500, Keysight Technology) and a probe station (M150, Cascade).

**Direct tunneling simulation for MNS structure.** The direct tunneling gate leakage current  $(J_{HVB})$  can be described by<sup>49</sup>

$$J_{HVB} = AE_{SiN}^2 e^{\frac{-B\left[1 - \left(1 - \frac{V_{SiN}}{\phi_b}\right)^3\right]}{E_{SiN}}}$$

(2)

where  $A = \frac{q^3}{8\pi} h m_h^* \phi_b$ ,  $B = \frac{8\pi (2m_h^*)^{\frac{1}{2}} \phi_b^{\frac{3}{2}}}{3hq}$ , q is electronic charge, h is Plank's constant,  $\phi_b$  (eV) is VBO between a-Si<sub>3</sub>N<sub>4</sub> and Si substrate,  $m_h^*$  is hole effective mass for a-Si<sub>3</sub>N<sub>4</sub>, and  $E_{SiN}$  (=V/d, V for gate bias, and d for thickness of a-Si<sub>3</sub>N<sub>4</sub>) is electric field in the dielectric.

#### References

- 1. Robertson, J. High dielectric constant gate oxides for metal oxide Si transistors. Rep. Prog. Phys. 69, 327-396 (2006).

- 2. Choi, K. et al. The Past, Present and Future of High-k/Metal Gates. ECS Transactions 53, 17-26 (2013).

- Guha, S., Cartier, E., Bojarczuk, N. A., Bruley, J., Gignac, L. & Karasinski, J. High-quality aluminum oxide gate dielectrics by ultrahigh-vacuum reactive atomic-beam deposition. Appl. Phys. Lett. 90, 512–514 (2001).

- 4. Ando, T. Ultimate Scaling of High-κ Gate Dielectrics: Higher-κ or Interfacial Layer Scavenging? Materials 5, 478-500 (2012).

- 5. Kwo, J. *et al.* High  $\varepsilon$  gate dielectrics Gd<sub>2</sub>O<sub>3</sub> and Y<sub>2</sub>O<sub>3</sub> for silicon. *Appl. Phys. Lett.* **77**, 130–132 (2000).

- 6. Robertson, J. Interfaces and defects of high-K oxides on silicon. Solid-State Electronics 49, 283–293 (2005).

- Yeo, Y.-C., King, T.-J. & Hu, C. Direct Tunneling Leakage Current and Scalability of Alternative Gate Dielectrics. Appl. Phys. Lett. 81, 2091 (2002).

- Biberman, A. & Bergman, K. Optical interconnection networks for high-performance computing systems. *Rep. Prog. Phys.* 75, 046402 (2012).

- Zhu, W., Neumayer, D., Perebeinos, V. & Avouris, P. Silicon Nitride Gate Dielectrics and Band Gap Engineering in Graphene Layers. Nano Lett. 10, 3572–3576 (2010).

- 10. Chen, J. et al. Two-Stage Metal-Catalyst-Free Growth of High-Quality Polycrystalline Graphene Films on Silicon Nitride Substrates. Adv. Mater. 25, 992–997 (2013).

- Sanne, A. et al. Top-gated chemical vapor deposited MoS<sub>2</sub> field-effect transistors on Si<sub>3</sub>N<sub>4</sub> substrates. Appl. Phys. Lett. 106, 062101 (2015).

- 12. Nagashio, K. *et al.* Impacts of graphene/SiO<sub>2</sub> interaction on FET mobility and Raman spectra in mechanically exfoliated graphene films. In *IEEE Int. Electron Devices Meet. Tech. Dig.* 2010 **23**, 4.1–23.4.4, doi: 10.1109/IEDM.2010.5703421 (2010).

- Liao, L. *et al.* Top-Gated Graphene Nanoribbon Transistors with Ultrathin High-k Dielectrics. *Nano Lett.* **10(5)**, 1917–1921 (2010).

Atanassova, E., Kassabov, J. & Goranova, E. Low-temperature plasma nitridation of thin thermal SiO<sub>2</sub> and a silicon surface with native oxide. *Microelectron. I.* **21**, 5–21 (1990).

- Dimitrova, T., Atanassova, E. D., Beshkov, G. D. & Pazov, J. Thin thermal SiO<sub>2</sub> after NH<sub>3</sub> or N<sub>2</sub>O plasma action under PECVD conditions. *Thin Solid Films* 252, 89–97 (1994).

- Cartier, E., Stathis, J. H. & Buchanan, D. A. Passivation and depassivation of silicon dangling bonds at the Si/SiO2 interface by atomic hydrogen. Appl. Phys. Lett. 63, 1510–1512 (1993).

- Deshpande, S. V., Gulari, E., Brown, S. W. & Rand, S. C. Optical properties of silicon nitride films deposited by hot filament chemical vapor deposition. J. Appl. Phys. 77, 6534–6541 (1995).

- Robertson, J. Electronic Structure of Defects in Amorphous Silicon Nitride. MRS Proceedings 1992 65, doi: 10.1557/PROC-284-65 (1992).

- Mohammed, S., Nimmo, M. T., Malko, A. V. & Hinkle, C. L. Chemical bonding and defect states of LPCVD grown silicon-rich Si<sub>3</sub>N<sub>4</sub> for quantum dot applications. J. Vac. Sci. Technol. A 32, 021507 (2014).

- Bagatur'yants, A. A. et al. A. A. Silicon nitride chemical vapor deposition from dichlorosilane and ammonia: theoretical study of surface structures and reaction mechanism. Surface Science 486, 213–225 (2001).

- 21. Goodman, A. M. Photoemission of electrons and holes into silicon nitride. Appl. Phys. Lett. 13, 275–277 (1968).

- 22. Bauer, J. Optical properties, band gap, and surface roughness of Si<sub>3</sub>N<sub>4</sub>. Phys. Status Solidi A39, 411-418 (1977).

- 23. Philipp, H. R. Optical Properties of Silicon Nitride. J. Electrochem. Soc. 120, 295–300 (1973).

- 24. Ren, S.-Y. & Ching, W. Y. Electronic structures of  $\beta$  and  $\alpha$ -silicon nitride. *Phys. Rev. B* **23**, 5454–5463 (1981).

- 25. Wu, C.-L., Chen, W.-S. & Su, Y.-H. N<sub>2</sub>-plasma nitridation on Si(111): Its effect on crystalline silicon nitride growth. *Surface Science* **606**, L51 (2012).

- Karlsson, C. J., Landemark, E., Chao, Y.-C. & Uhrberg, R. I. G. Atomic origins of the surface components in the Si 2p core-level spectra of the Si(111)7 × 7 surface. *Phys. Rev. B* 50, 5767 (2994).

- Rignanese, G.-M. & Pasquarello, A. Nitrogen bonding configurations at nitrided Si(001) surfaces and Si(001) SiO<sub>2</sub> interfaces: A first-principles study of core-level shifts. *Phys. Rev. B* 63, 075307 (2001).

- Higuchi, M. et al. Subnitride and valence band offset at Si3N4/Si interface formed using nitrogen-hydrogen radicals. Appl. Phys. Lett. 90, 123114 (2007).

- 29. Oh, J. H. *et al.* A. Chemical structure of the ultrathin SiO<sub>2</sub>/Si(100) interface: An angle-resolved Si 2p photoemission study. *Phys. Rev.* B 63, 205310 (2001).

- Lee, H.-M., Kuo, C.-T., Shiu, H.-W., Chen, C.-H. & Gwo, S. Valence band offset and interface stoichiometry at epitaxial Si<sub>3</sub>N<sub>4</sub>/Si(111) heterojunctions formed by plasma nitridation. *Appl. Phys. Lett.* 95, 222104 (2009).

- Ranke, W. & Xing, Y. R. Surface dipole and Fermi-level position on clean, oxygen-, and water-covered cylindrical Si crystals: A photoelectron spectroscopy study. *Phys. Rev. B* 31, 2246 (1985).

- 32. Hunger, R. et al. Chemical and electronic characterization of methyl-terminated Si(111) surfaces by high-resolution synchrotron photoelectron spectroscopy. Phys. Rev. B 72, 045317 (2005).

- 33. Cook, T. E. et al. Band offset measurements of the Si<sub>3</sub>N<sub>4</sub>/GaN (0001) interface. J. Appl. Phys. 94, 3949 (2003).

- Omeltchenko, A. et al. Stress Domains in Si(111)/Si<sub>3</sub>N<sub>4</sub>(0001) Nanopixel 10 Million-atom Molecular Dynamics Simulations on Parallel Computers. Phys. Rev. Lett. 84, 318 (2000).

- 35. Lidorikis, E. et al. Coupling Length Scales for Multiscale Atomistic-Continuum Simulations: Atomistically- Induced Stress Distributions in Si/Si<sub>3</sub>N<sub>4</sub> Nanopixels. *Phys. Rev. Lett.* **87**, 086104 (2001).

- McPherson, J., Kim, J., Shanware, A., Mogul, H. & Rodriguez, J. Proposed universal relationship between dielectric breakdown and dielectric constant. In *IEEE Int. Electron Devices Meet. Tech. Dig.* 2002, 633–636, doi: 10.1109/IEDM.2002.1175919 (2002).

- Higuchi, M. et al. Electric Characteristics of Si<sub>3</sub>N<sub>4</sub> Films Formed by Directly Radical Nitridation on Si(110) and Si(100) Surfaces. Jpn. J. Appl. Phys. 46, 1895 (2007).

- Yeo, Y. C. et al. Direct Tunneling Gate Leakage Current in Transistors with Ultrathin Silicon Nitride Gate Dielectric. IEEE Electron Device Lett. 21, 540 (2000).

- Degraeve, R. et al. A consistent model for the thickness dependence of intrinsic breakdown in ultra-thin oxides. In IEEE Int. Electron Devices Meet. Tech. Dig. 1995, 863–866, doi: 10.1109/IEDM.1995.499353 (1995).

- 40. Degraeve, R. *et al.* New insights in the relation between electron trap generation and the statistical properties of oxide breakdown. *IEEE Trans. Electron Devices* **45**, 904 (1998).

- 41. Gusev, E. P. et al. Ultrathin high-K gate stacks for advanced CMOS devices. In *IEEE Int. Electron Devices Meet. Tech. Dig.* 2001, 20.1.1, doi: 10.1109/IEDM.2001.979537 (2001).

- Lee, B. H. et al. Ultrathin Hafnium Oxide with Low Leakage and Excellent Reliability for Alternative Gate Dielectric Application. In IEEE Int. Electron Devices Meet. Tech. Dig. 1999, 133, doi: 10.1109/IEDM.1999.823863 (1999).

- 43. Wang, Y., Wang, H., Ye, C., Zhang, J. & Wang, H. & Jiang, Y. Interfacial reaction and electrical properties of HfO<sub>2</sub> film gate dielectric prepared by pulsed laser deposition in nitrogen: role of rapid thermal annealing and gate electrode. ACS *Appl. Mater. Interfaces* 3(10), 3813–3818 (2011).

- 44. Lo, S. H., Buchanan, D. A., Taur, Y. & Wang, W. Quantum-mechanical modeling of electron tunneling current from the inversion layer of ultra-thin-oxide nMOSFET's. *IEEE Electron Device Lett.* **18**, 209–211 (1997).

- Liao, L. *et al.* Top-Gated Graphene Nanoribbon Transistors with Ultrathin High-k Dielectrics. *Nano Lett.* 10(5), 1917 (2010).

Liao, L. *et al.* High-Performance Top-Gated Graphene-Nanoribbon Transistors Using Zirconium Oxide Nanowires as High-

- Dielectric-Constant Gate Dielectrics. Adv. Mater. 22, 1941–1945 (2010).

- 47. Wang, Z. et al. Growth and Performance of Yttrium Oxide as an Ideal High-Kappa Gate Dielectric for Carbon-Based Electronics. Nano Lett. 10, 2024 (2010).

- 48. Tauc, J. (ed.) Amorphous and Liquid Semiconductors (Plenum, 1974).

- Schuegraf, K. F. & Hu, C. Hole Injection SiO<sub>2</sub> Breakdown Model for Very Low Voltage Lifetime Extrapolation. IEEE Trans. Electron Devices 41, 761 (1994).

#### Acknowledgments

We thank Mei-Lan Liang, Shi-Wen Zeng, and Dr. Zhong-Xing Bao for TEM sample preparation, characterization, and analysis, respectively. This work was supported by the Ministry of Science and Technology in Taiwan.

### **Author Contributions**

S.-J.T. initiated the PA-ABD *a*-Si<sub>3</sub>N<sub>4</sub>, came up with the experimental design, synthesized the samples and devices, performed and analyzed the PL, optical band gap, AFM and electrical measurements, calculated the leakage current, wrote the paper, and supervised the project. C.-L.W. performed  $\mu$ -PES measurement and calculate leakage current. H.-C.L., C.-Y.L. and L.-W.T. assisted with PA-ABD growth. J.-W.C., H.-W.S., L.-Y.C., Y.-C.C. and C.-H.C. assisted with  $\mu$ -PES measurement. H.-T.H. synthesized the PECVD a-SiNx. H.-Y.C. and H.T. assisted with analysis of optical band gap. J.-Y.T., Y.-H.L. and T.-C.C. supported electrical measurements. C.-L.W. identify the PA-ABD *a*-Si<sub>3</sub>N<sub>4</sub> as the material of interest, analyzed the TEM and  $\mu$ -PES data, organized the project, and wrote the paper. All authors reviewed the manuscript.

### Additional Information

Supplementary information accompanies this paper at http://www.nature.com/srep

Competing financial interests: The authors declare no competing financial interests.

How to cite this article: Tsai, S.-J. *et al.* Approaching Defect-free Amorphous Silicon Nitride by Plasma-assisted Atomic Beam Deposition for High Performance Gate Dielectric. *Sci. Rep.* **6**, 28326; doi: 10.1038/srep28326 (2016).

This work is licensed under a Creative Commons Attribution 4.0 International License. The images or other third party material in this article are included in the article's Creative Commons license, unless indicated otherwise in the credit line; if the material is not included under the Creative Commons license, users will need to obtain permission from the license holder to reproduce the material. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/