# **OPEN**

Received: 05 April 2016 Accepted: 23 May 2016 Published: 09 June 2016

# Improved Gate Dielectric Deposition and Enhanced Electrical Stability for Single-Layer MoS<sub>2</sub> MOSFET with an AIN Interfacial Layer

Qingkai Qian<sup>1</sup>, Baikui Li<sup>1</sup>, Mengyuan Hua<sup>1</sup>, Zhaofu Zhang<sup>1</sup>, Feifei Lan<sup>2</sup>, Yongkuan Xu<sup>2</sup>, Ruyue Yan<sup>2</sup> & Kevin J. Chen<sup>1</sup>

Transistors based on  $MoS_2$  and other TMDs have been widely studied. The dangling-bond free surface of  $MoS_2$  has made the deposition of high-quality high-k dielectrics on  $MoS_2$  a challenge. The resulted transistors often suffer from the threshold voltage instability induced by the high density traps near  $MoS_2$ /dielectric interface or inside the gate dielectric, which is detrimental for the practical applications of  $MoS_2$  metal-oxide-semiconductor field-effect transistor (MOSFET). In this work, by using AIN deposited by plasma enhanced atomic layer deposition (PEALD) as an interfacial layer, top-gate dielectrics as thin as 6 nm for single-layer  $MoS_2$  transistors are demonstrated. The AIN interfacial layer not only promotes the conformal deposition of high-quality  $Al_2O_3$  on the dangling-bond free  $MoS_2$ , but also greatly enhances the electrical stability of the  $MoS_2$  transistors. Very small hysteresis ( $\Delta V_{\rm th}$ ) is observed even at large gate biases and high temperatures. The transistor also exhibits a low level of flicker noise, which clearly originates from the Hooge mobility fluctuation instead of the carrier number fluctuation. The observed superior electrical stability of  $MoS_2$  transistor is attributed to the low border trap density of the AIN interfacial layer, as well as the small gate leakage and high dielectric strength of AIN/Al $_2O_3$  dielectric stack.

Molybdenum disulfide ( $MoS_2$ ), as a layered material from the transition metal dichalcogenide (TMD) family, has been widely studied in recent years<sup>1-3</sup>, for its intriguing properties such as atomic-layer thickness, tunable bandgap<sup>4</sup>, high mobility<sup>3</sup> and good thermal stability<sup>1</sup>.  $MoS_2$  MOSFET has been shown to exhibit suppressed short channel effect and has the potential to be used in the next generation nanoelectronics<sup>2,5</sup>. Many other applications based on single- or multi-layer  $MoS_2$ , such as flexible electronics<sup>6-8</sup>, photon detectors<sup>9,10</sup> and gas sensors<sup>11</sup>, have been demonstrated. Single-layer  $MoS_2$  also offers new opportunities in novel piezoelectronics<sup>12,13</sup> and valleytronics<sup>14,15</sup>. Moreover, the recent advance in wafer-scale deposition of high-quality  $MoS_2$  films<sup>16</sup> has made these  $MoS_2$  based applications even more promising.

However, the performance of  $MoS_2$  MOSFET is very sensitive to the ambient conditions and electrical stress<sup>17–19</sup>. As reported previously, when exposed to air, the  $MoS_2$  MOSFETs could exhibit large performance variation in terms of large shift in threshold voltage (i.e. hysteresis), due to the water or oxygen adsorbates<sup>18,19</sup>. This threshold voltage instability ( $\Delta V_{\rm th}$ ) is detrimental to both logic and analog circuit applications. Moreover, these ambient adsorbates will further degrade the carrier mobility and cause severe current fluctuation noise<sup>20</sup>. The  $MoS_2$  MOSFET has to be passivated in order to alleviate the ambient influence and achieve reliable performance. Because of the dangling-bond-free nature of  $MoS_2$  surface, the deposition of high quality dielectric on  $MoS_2$  can be challenging<sup>21–25</sup>. Even with passivation,  $MoS_2$  MOSFETs still exhibit significant hysteresis problem<sup>7,26</sup>, due to high-density traps at  $MoS_2$ /dielectric interface or in the gate dielectric.

<sup>1</sup>Department of Electronic and Computer Engineering, Hong Kong University of Science and Technology, Clear Water Bay, Hong Kong SAR, China. <sup>2</sup>The 46th Research Institute, CETC, Tianjin 300220, China. Correspondence and requests for materials should be addressed to K.J.C. (email: eekjchen@ust.hk)

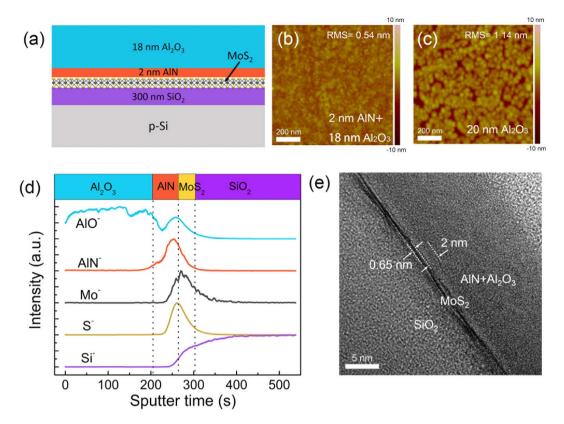

**Figure 1.** (a) Schematic of  $MoS_2$  sample after the deposition of  $AlN/Al_2O_3$ . (b) AFM image of  $MoS_2$  surface after the deposition of 2-nm AlN and 18-nm  $Al_2O_3$ . (c) AFM image of  $MoS_2$  surface after the direct deposition of 20-nm  $Al_2O_3$ . (d) Element distribution profiles from ToF-SIMS measurement and (e) Cross-sectional HRTEM image of the structure in (a).

Both hexagonal boron nitride (hBN) and aluminum nitride (AlN) are suggested to be ideal gate dielectrics for  $MoS_2$  FETs<sup>27</sup>. It has already been demonstrated that the hysteresis of  $MoS_2$  transistor was greatly reduced by using the exfoliated hBN as gate dielectric, benefiting from the good  $MoS_2$ /dielectric interface<sup>8</sup>. But as a layered material, hBN is usually obtained by mechanical exfoliation<sup>8,28</sup> or synthesized at high temperatures<sup>29,30</sup>, which makes it difficult to be deposited reliably on large scale as top-gate dielectric. In contrast to the layered hBN, AlN is a bulk material with a larger bandgap of 6.3 eV and higher dielectric constant of 9.14<sup>27,31</sup>, and can be deposited uniformly on large samples by PEALD<sup>32</sup> or thermal ALD<sup>33</sup>. Moreover, our recent result has shown that by using AlN and  $Al_2O_3$  stack as gate dielectric, AlN is capable of isolating the channel from the bulk traps of  $Al_2O_3$  and achieving a low border trap density<sup>34,35</sup>.

In this paper, we report the experimental demonstration of single-layer  $MoS_2$  MOSFETs with  $AlN/Al_2O_3$  as top-gate dielectric. By the insertion of AlN interfacial layer, the gate dielectrics scaling down to as thin as 6 nm are realized. The electrical stabilities of the fabricated devices are systematically characterized under different conditions. The transistor shows very small hysteresis even under large gate biases and high temperatures. Low-frequency noise characterization is conducted and the  $MoS_2$  transistor exhibits suppressed current fluctuation. The observed excellent threshold voltage stability is contributed by the low border trap density of AlN near the  $MoS_2$  interface, as well as the small gate leakage and high dielectric strength of  $AlN/Al_2O_3$ .

# **Results and Discussion**

MoS $_2$  samples used here were synthesized on sapphire substrate by CVD method using high purity MoO $_3$  and S powder as precursors. The triangular MoS $_2$  flakes have a size of about 100  $\mu$ m (See Supplementary Figure S1). The Raman characterization shows peak distance of 19 cm $^{-1}$  for  $E_{2g}^1$  and  $A_{1g}$ , suggesting the MoS $_2$  flakes are single layered $^{36}$ . The MoS $_2$  flakes were then transferred to a silicon substrate capped with 300-nm thermally grown SiO $_2$ . Depositing dielectric on the dangling-bond-free MoS $_2$  is a challenging task $^{21-25}$ . At first, the process for depositing AlN/Al $_2$ O $_3$  dielectric stack on MoS $_2$  was carefully tested. Both AlN and Al $_2$ O $_3$  were deposited using the Oxford Instruments OpAL ALD system. AlN was deposited at 170 °C by using trimethylaluminum (TMA) and remote N $_2$  plasma (20 sccm with a coil power of 25 W) as Al and N sources. The growth temperature and the RF power were optimized to minimize the plasma damage to the MoS $_2$ , resulting in a relatively slow growth rate of 0.18 Å/cycle. The detailed optimization processes are provided in Supplementary Figure S2. After the deposition of 2-nm AlN, 18-nm Al $_2$ O $_3$  was grown *in-situ* under thermal ALD mode at 200 °C by using TMA and water vapor as Al and O sources.

The schematic structure of the single-layer  $MoS_2$  sample after the deposition of 2-nm AlN and 18-nm  $Al_2O_3$  is shown in Fig. 1a. The surface morphology was characterized by AFM and shown in Fig. 1b. Continuous and smooth surface was obtained. Within a  $1 \mu m^2$  area, the root mean square (RMS) surface roughness is 0.54 nm.

In our experiment, the bare SiO<sub>2</sub>/Si wafer usually has a surface roughness of 0.15 nm. However, since the MoS<sub>2</sub> samples are transferred to the SiO<sub>2</sub>/Si wafer, the surface roughness increases to 0.35–0.5 nm and dominates the above measured results. In contrast, for the MoS<sub>2</sub> sample covered by 20-nm Al<sub>2</sub>O<sub>3</sub> deposited at 200 °C, as shown by the AFM image in Fig. 1c, the dielectric film is full of broken areas due to weak adhesion of the precursors (TMA and water) on the dangling-bond-free MoS<sub>2</sub> surface, which is consistent with previous reports<sup>23,25</sup>. Since it has been suggested that organic or solvent residue can assist the successful deposition of dielectrics on MoS<sub>2</sub><sup>22</sup>, the failure of direct deposition of Al<sub>2</sub>O<sub>3</sub> on the MoS<sub>2</sub> sample also reflects that the MoS<sub>2</sub> has maintained a clean surface during the fabrication process. The successful deposition of AlN/Al<sub>2</sub>O<sub>3</sub> on MoS<sub>2</sub> could be the result of the relatively low growth temperature of AlN. However, we found that even when the ALD growth temperature of Al<sub>2</sub>O<sub>3</sub> was reduced to 170 °C, similar poor quality was still observed when Al<sub>2</sub>O<sub>3</sub> was directly deposited on MoS<sub>2</sub> (See Supplementary Figure S1). Thus, we conclude that the improved surface morphology and quality of AlN/Al<sub>2</sub>O<sub>3</sub> dielectric stack on the dangle-bond-free MoS<sub>2</sub> surface is mainly the benefits of the low-power remote nitrogen plasma during the PEALD growth of AlN, which is similar to the O<sub>2</sub> plasma functionalization of the multilayer MoS<sub>2</sub> that was used to promote the ALD deposition of Al<sub>2</sub>O<sub>3</sub><sup>25</sup>. Even though the remote pure N<sub>2</sub> plasma is very mild to single-layer MoS<sub>2</sub> during several hours' treatment (See Supplementary Figure S4), defects are still observed due to the possible Ar/H plasma damage during dose and purge of TMA (See Supplementary Figure S2(c)). At present, it cannot be determined to what extent the plasma damage facilitates the uniform dielectric deposition. Further experiments are needed to verify the possibility of AlN deposition on the dangling-bond free MoS<sub>2</sub> only by the physical absorption of N-ion on the MoS<sub>2</sub> surface, even for single-layer MoS<sub>2</sub>.

The successful deposition of  $AlN/Al_2O_3$  stack on  $MoS_2$  was further verified by Time-of-Flight Second Ion Mass Spectrometry (ToF-SIMS), as shown in Fig. 1d. In this plot each relevant element's intensity has been normalized by its peak value and offset vertically for clearer view. We can clearly identify the peak for  $AlN^-$ , which appears ahead of  $Mo^-$  and  $S^-$  during the surface sputtering. Figure 1e shows the cross-sectional high resolution transmission electron microscopic (HRTEM) image of the  $SiO_2/MoS_2/AlN/Al_2O_3$  structure. The single-layer  $MoS_2$  can be clearly identified. Both AlN and  $Al_2O_3$  are in amorphous state without a visible distinct junction boundary between them. The N atom concentration is more likely to be higher near the  $MoS_2$  interface, due to the possible oxidation of AlN surface during the subsequent  $Al_2O_3$  growth. The relatively bright area near  $MoS_2/AlN$  interface might be the result of smaller density of AlN compared to that of  $Al_2O_3$ , which causes less electron scattering in the bright field TEM and thus becomes brighter. The  $AlN/Al_2O_3$  layers are uniformly grown on  $MoS_2$  surface with no gaps or agglomerates, implying a reliable deposition process of  $AlN/Al_2O_3$  as gate dielectric for  $MoS_2$  transistors.

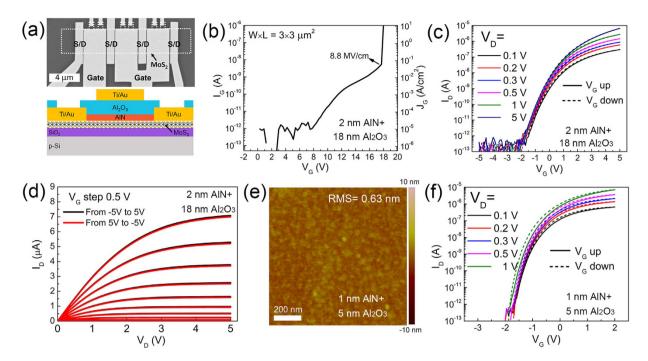

Single-layer  $MoS_2$  transistors with 2-nm AlN/18-nm  $Al_2O_3$  as top-gate dielectric were fabricated. Source/drain contacts were defined by electron-beam photolithography (EBL), followed by e-beam evaporation of 10-nm Ti and 50-nm Au and lift-off. The  $MoS_2$  flakes are further patterned into the designed channel size by EBL and  $O_2$  plasma etch. Then an  $AlN/Al_2O_3$  (2 nm/18 nm) stack was deposited on top of  $MoS_2$  as gate dielectric following the afore-described PEALD/ALD procedure. Another EBL was conducted to define the top gate, followed by e-beam evaporation of Ti/Au (10 nm/50 nm) and lift-off. Finally, the contact holes were formed by etching  $AlN/Al_2O_3$  with developer FHD-5. The SEM image of fabricated devices is shown in Fig. 2a, together with the schematic cross-sectional view of the device. The channel width and gate length are  $3\,\mu m$ . There is 100-nm spacing between the gate and source/drain contacts. The  $MoS_2$  transistors were measured at room temperature in atmosphere by Agilent B1505A device analyzer/curve tracer. Figure 2b shows result of the gate leakage and the hard breakdown test for the gate dielectric. The current of about 1 pA when biased at small gate voltage is mainly limited by the equipment resolution. The  $AlN/Al_2O_3$  dielectric shows a small leakage of about 0.1 pA/ $\mu$ m<sup>2</sup> for gate electric field as high as 4 MV/cm. At the same time a high breakdown electric field of 8.8 MV/cm is measured.

Figure 2c shows the transfer curves measured under different drain voltage biases ranging from 0.1 V to 5 V for transistor with 2-nm AlN and 18-nm Al<sub>2</sub>O<sub>3</sub> as gate dielectric. During the measurements the gate voltage is swept from -5 V to 5 V then back to -5 V again. The transfer curves for sweeping  $V_G$  up and  $V_G$  down are plotted by the solid and dashed lines respectively. Remarkably the transfer curves exhibit very small hysteresis for all the drain voltage biases. A large on/off ratio of about 106 is achieved, and the off-current is still limited by the equipment current resolution. The field effect mobility is extracted to be 3.3 cm<sup>2</sup>/V·s by using equation  $\mu = dI_D/dV \times L/dV$  $(WC_{ox}V_D)$  in four-probe measurement configuration, during which  $\varepsilon = 9$  is adopted as the relative dielectric constant for both AlN and Al<sub>2</sub>O<sub>3</sub> to calculate  $C_{ox}$ . This observed mobility is comparable to previous results for single-layer MoS<sub>2</sub> transistors with MoS<sub>2</sub> channel exposed to air<sup>8,37</sup>, but is smaller than that of  $13-16\,\mathrm{cm^2/V}\cdot\mathrm{s}$  for similar devices passivated by ALD Al<sub>2</sub>O<sub>3</sub><sup>38,39</sup>. The relatively smaller mobility might be the results of varied CVD growth and fabrication conditions<sup>40</sup> or specifically the remote plasma damage introduced by the PEALD growth of AlN in our case (See Supplementary Figure S4). Because single-layer MoS, has only one atomic layer thickness and lacks the Thomas-Fermi screening effect to mitigate the impacts from the MoS<sub>2</sub>/dielectric interfaces<sup>3</sup>, the mobility of single-layer MoS, becomes more sensitive to the dielectric environments and the plasma damage, and is reported to be smaller than that of multilayer ones $^{8,37,41}$ . By using high-quality exfoliated multilayer MoS<sub>2</sub> in the future, which is less vulnerable to potential variations<sup>37</sup> and more resistant to surface plasma treatment<sup>25,42</sup>, higher mobility can be achieved. Figure 2d shows the output curves, the black and red curves represent the results for stepping  $V_G$  up and  $V_G$  down respectively. Very good current saturation is observed, and the  $I_D$ - $V_D$  near  $V_D$ =0 Vexhibits linear relationship. There is almost no discrepancy between the output curves for sweeping  $V_G$  up and  $V_G$ down, suggesting reliable performance.

To fully exploit the potential of the AlN interfacial layer in promoting the uniform deposition of high-quality dielectric on the dangling-bond free MoS<sub>2</sub> surface, gate dielectric consisting of 1-nm AlN and 5-nm Al<sub>2</sub>O<sub>3</sub> is deposited, which is the thinnest dielectric ever reported for MoS<sub>2</sub> transistor<sup>25</sup>. The MoS<sub>2</sub> surface after the dielectric deposition is characterized by AFM and shown in Fig. 2e. Even with greatly reduced thickness, the AlN/Al<sub>2</sub>O<sub>3</sub> on the dangling-bond free MoS<sub>2</sub> still maintains a smooth surface with no pinholes, implying uniform nucleation

Figure 2. (a) SEM image and schematic of single-layer MoS $_2$  transistor with AlN/Al $_2$ O $_3$  as top-gate dielectric. (b) Forward gate I-V characteristics with gate dielectric breakdown. (c) Transfer curves ( $I_D$  vs.  $V_G$ ) at different drain biases with the gate voltage swept from -5 V to 5 V (solid lines, up-sweep) then back to -5 V (dashed line, down-sweep). (d) Output curves by stepping  $V_G$  up (black) and down (red) with a  $V_G$  step 0.5 V. Performances of (b-d) are measured for transistor with 2-nm AlN/18-nm Al $_2$ O $_3$  dielectric stack. (e) AFM image of MoS $_2$  surface after the deposition of 1-nm AlN and 5-nm Al $_2$ O $_3$ . (f) Transfer curves swept from -2 V to 2 V then back to -2 V for transistor with 1-nm AlN and 5-nm Al $_2$ O $_3$  as gate dielectric.

sites provided by the 1-nm AlN interfacial layer. Figure 2f shows the transfer curves for  $MoS_2$  transistor with this ultra-thin stack as gate dielectric. Effective gate modulation and small hysteresis are observed, suggesting that by using PEALD AlN as an interfacial layer, high-quality dielectric even with sub-10 nm thickness can be successfully deposited on the dangling-bond free  $MoS_2$ , which is very important for the continuous scaling down of  $MoS_2$  FET for higher performance.

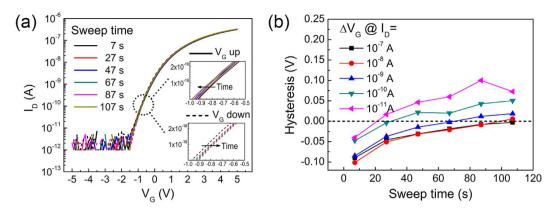

The transfer curves for transistor with 2-nm Aln/18-nm Al<sub>2</sub>O<sub>3</sub> gate dielectric shown in Fig. 2c were measured with a total sweep time of 7 s. However there are reports suggesting that the threshold voltage instability can be strongly affected by the sweep rate<sup>18,19</sup>. So we also measured the transfer curves with different sweep time ranging from 7 s to 107 s as shown in Fig. 3a. Still no obvious hysteresis is observed. By zooming in the transfer curves as shown in the two insets of Fig. 3a, we can identify the trends of shifting in the transfer curves. With increased sweep time, the transfer curve continuously shifts left during the up-sweep, and shifts right during the down-sweep. The above observation suggests that more trapped electrons are emitted with a slower up-sweep, and more electrons are trapped with a slower down-sweep. These threshold voltage shift trends result in an increased hysteresis as plotted in Fig. 3b, in which the hysteresis is calculated by the difference of  $V_{\rm G}$  corresponding to the same  $I_D$  during the up- and down-sweep. Different  $I_D$  criteria have been used, and the resultant hysteresis differs from each other due to the complex trapping and stabilization processes involved during a complete sweep. We find that smaller  $I_D$  criterion yields larger hysteresis. Interestingly, a negative hysteresis is observed when the sweep time is short, which might be the result of gate-side electron injection<sup>43</sup> and is consistent with the pulsed I-V measurement results (See Supplementary Figure S5). In general, with increased sweep time, the hysteresis increases but tends to be stabilized and is limited within 0.1 V for all the  $I_D$  criteria. Such a small hysteresis is the best result ever reported to date for MoS<sub>2</sub> FET.

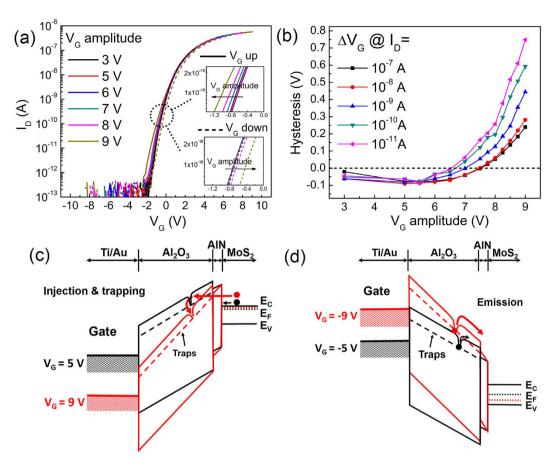

To better understand the observed hysteresis, transfer curves with different  $V_G$  sweep amplitudes for transistor with 2-nm AlN/18-nm Al $_2$ O $_3$  gate dielectric were measured and plotted in Fig. 4a. The gate is swept from negative to positive then back to negative voltage with a total sweep time of 7 s. The hysteresis becomes more pronounced with increased  $V_G$  amplitude. The hysteresis is extracted quantitatively as shown in Fig. 4b. It is observed that the hysteresis has little change when  $V_G$  amplitude is smaller than 7 V, but increases more significantly when  $V_G$  amplitude is larger. It is also noticed that there is almost no  $V_{th}$  shift until the  $V_G$  amplitudes is larger than 8 V during the down-sweep. Recalling that the gate leakage in Fig. 2b also becomes prominent only when  $V_G$  is larger than 8 V, this  $V_{th}$  shift can then be correlated with the injection and trapping of electrons inside the gate dielectric  $^{44,45}$  as schematically shown in Fig. 4c. On the other hand, when the gate is negatively biased, the high electric field will enhance the emission of electrons trapped inside the gate dielectric, accounting for the negative  $V_{th}$  shift at larger  $V_G$  amplitude in the down-sweep, as schematically shown in Fig. 4d. The above observation reveals that the MoS $_2$  transistor with AlN/Al $_2$ O $_3$  as top-gate dielectric presents small hysteresis even under large gate voltage

Figure 3. (a) Transfer curves with different sweep time for transistor with 2-nm AlN/18-nm Al $_2$ O $_3$  gate dielectric. The  $V_{\rm G}$  is swept from -5 V to 5 V then back to -5 V again, and  $V_{\rm D}$  is 0.1 V. The two insets show the zoomed-in transfer curves for sweeping  $V_{\rm G}$  up and  $V_{\rm G}$  down respectively. (b) Hysteresis extracted from (a) by calculating the difference of  $V_{\rm G}$  corresponding to a specific  $I_{\rm D}$  during sweeping  $V_{\rm G}$  down and  $V_{\rm G}$  up. Different  $I_{\rm D}$  criteria are used.

bias, and the observed weak threshold voltage instability is mainly caused by the gate leakage at high gate electric field and the resultant trapping/detrapping of electrons in the border traps (within the bulk  $Al_2O_3$  but close to the dielectric/MoS<sub>2</sub> interface).

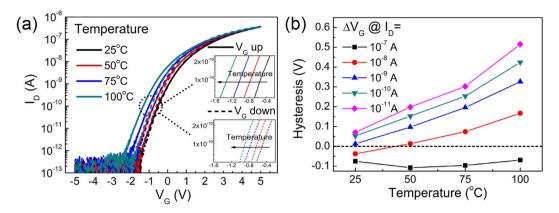

It has been demonstrated that  $MoS_2$  transistor is capable of working at high temperature, although significant mobility degradation and threshold voltage shift have been observed<sup>46</sup>. The  $MoS_2$  transistors fabricated in this work with 2-nm AlN/18-nm  $Al_2O_3$  gate dielectric was tested at temperatures ranging from 25 °C to 100 °C, all conducted in ambient environment. The transfer curves are plotted in Fig. 5a, with a sweep time of 70 s. The two insets of Fig. 5a show the zoomed-in transfer curves, from which we can clearly see the shifting trends of the transfer curves with increased temperature. A negative shift in  $V_{th}$  is observed at higher temperature, which is caused by enhanced emission of electrons trapped in the gate dielectric. The hysteresis increases at higher temperature, as quantitatively shown in Fig. 5b. This is because the gate leakage and the consequent electron injection/trapping is enhanced at higher temperature. Nevertheless, the hysteresis still remains smaller than 0.5 V.

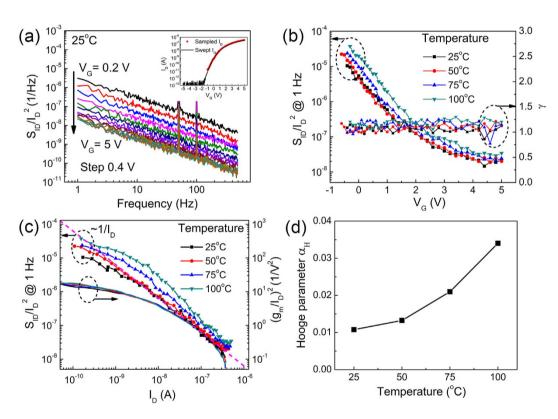

Nanoscale devices can suffer from the flicker noise (1/f noise) which increases with smaller channel size<sup>47</sup>. Thus, maintaining a low level of flicker noise is necessary to obtain high performance MoS<sub>2</sub> transistors. On the other hand, the flicker noise characterization is a useful tool to diagnose the channel/gate-dielectric interface<sup>20,47,48</sup>, since the conventional C-V measurement has become difficult due to the limited channel area. The flicker noise spectra for the fabricated MoS<sub>2</sub> transistor with 2-nm AlN/18-nm Al<sub>2</sub>O<sub>3</sub> gate dielectric at various temperatures were measured using SR570 low-noise current preamplifier. The results at 25 °C are shown in Fig. 6a. The spectra correspond to different gate biases with a fixed drain bias of 0.1 V. The measurement of each spectrum takes a total sampling time of 120 s. The inset of Fig. 6a shows the average sampled  $I_D$  (red), together with the quasi-static  $I_D$  (black), showing no obvious discrepancy. This agreement suggests again very good electrical stability of the MoS<sub>2</sub> transistors even after long-term electrical stress. The normalized flicker noise can be expressed as  $S_{ID}/I_D^2 = A/f^\gamma$ , in which A is the noise amplitude and f is the frequency. Ideally the frequency exponent  $\gamma$  should be close to 1<sup>20</sup>. Figure 6b shows the noise amplitude A ( $S_{ID}/I_D^2$  at 1 Hz) and also the fitted frequency exponent  $\gamma$ , for different gate biases at various temperatures. All the values of  $\gamma$  are close to 1, suggesting that the noise spectra follow the 1/f relationship well. Meanwhile, we find that higher flicker noise occur at higher temperatures. The normalized noise  $S_{ID}/I_D^2$  at 1 Hz decrease monotonously with the gate voltage, suggesting that there is less relative fluctuation when more carriers are present in the channel.

The generation of flicker noise can be explained by the carrier number fluctuation or the mobility fluctuation  $^{49}$ . For noise generated by carrier number fluctuation, the flicker noise  $S_{ID}/I_D^{-2}$  is proportional to  $(g_m/I_D)^2$ , where  $g_m$  is the gate transconductance, while the flicker noise  $S_{ID}/I_D^{-2}$  generated by the mobility fluctuation would be simply proportional to  $1/I_D^{-49}$ . To find the exact origin of the flicker noise,  $S_{ID}/I_D^{-2}$  (at 1 Hz) and  $(g_m/I_D)^2$  are plotted together in Fig. 6c. We find that  $S_{ID}/I_D^{-2}$  deviates from  $(g_m/I_D)^2$  significantly by several orders. On the other hand,  $S_{ID}/I_D^{-2}$  follows  $1/I_D$  relationship well as indicated by the dashed line. Therefore, we conclude that the flicker noise observed in our MoS<sub>2</sub> transistor is caused by the mobility fluctuation instead of the carrier number fluctuation, which is consistent with previous report for single-layer MoS<sub>2</sub> transistor<sup>20</sup>.

According to the Hooge empirical relationship, the flicker noise can be expressed by  $S_{ID}/I_D^2 = q\alpha_H \mu V_D/fL^2I_D^{47}$ . The Hooge parameter  $\alpha_H$  is extracted and plotted in Fig. 6d. It can be seen that the Hooge parameter increases with temperature, indicating severer mobility fluctuation at higher temperature. The measured Hooge parameter at 25 °C is 0.011, which is two orders of magnitude smaller than the published result for the same mobility range<sup>20</sup>, suggesting excellent suppression of flicker noise. The flicker noise caused by carrier number fluctuation is related to the border trap density by equation  $S_{ID}/I_D^2 = (g_m/I_D)^2 S_{VG}$ , in which  $S_{VG} = q^2kT\lambda N_t/WLC_{ox}^2 f$  is the equivalent gate voltage spectral density<sup>47</sup>. Since in our case the flicker noise is generated by the mobility fluctuation, it is difficult to extract the accurate border trap density directly, but the observed flicker noise has placed an upper limit on the possible border trap density. By assuming the flicker noise is all generated by the carrier number fluctuation when

**Figure 4.** (a) Transfer curves measured with different  $V_G$  sweep amplitude for transistor with 2-nm AlN/18-nm Al<sub>2</sub>O<sub>3</sub> gate dielectric. The sweep time is 7 s and the drain bias is 0.1 V. The two insets show the zoomed-in transfer curves during the up- and down-sweep. (b) Hysteresis extracted from (a). (c) Schematic band diagram when the gate are positively biased at 5 V and 9 V. With a larger sweep amplitude, enhanced electron injection and trapping would occur since the tunneling barrier is reduced. (d) Schematic band diagram when the gate is negatively biased at -5 V and -9 V. The detrapping of electrons is assisted by higher electric field.

$V_{\rm G}$  is biased above the threshold voltage at 25 °C, we calculate the upper limit of the border trap density to be  $\lambda N_t \ll 1.6 \times 10^{12} cm^{-2} eV^{-1}$  (See Supplementary Figure S6 for the results of  $S_{VG}$ ).

### Conclusion

Single-layer  $MoS_2$  MOSFETs with  $AlN/Al_2O_3$  gate dielectric are demonstrated. Gate dielectrics scaling down to 6 nm on the dangling-bond free  $MoS_2$  are realized by the insertion of AlN interfacial layer. The  $MoS_2$  transistor with 20-nm top-gate dielectric exhibits hysteresis smaller than  $0.1\,V$  at room temperature in ambient environment. The hysteresis increases when biased at higher gate voltage or measured at higher temperature, but remains below  $0.8\,V$  even for gate-dielectric electric-field as high as  $4.5\,MV/cm$  or temperature up to  $100\,^{\circ}C$ . This remarkable electrical stability mainly benefits from the low border trap density, enabled by the inserted AlN interfacial layer, and consequently small gate leakage and high dielectric strength of the  $AlN/Al_2O_3$  stack. The  $MoS_2\,MOSFET$  also presents a low level of flicker noise, which is generated by the mobility fluctuation instead of the carrier number fluctuation.  $AlN/Al_2O_3$  with AlN as interfacial layer is shown to be a promising candidate as both excellent gate dielectric and effective passivation for implementing reliable  $MoS_2\,MOSFETs$ , and probably also has the potential to be used in other nanodevices, such as transistors based on graphene, carbon nanotubes and other TMDs, which also face the problems of large hysteresis and reliable dielectric deposition due to the lack of surface bond.

### Methods

**MoS**<sub>2</sub> **Preparation.** MoS<sub>2</sub> flakes were synthesized on sapphire substrate by CVD method using high purity MoO<sub>3</sub> and S powder as precursors. The synthesized MoS<sub>2</sub> has a flake size of about  $100\,\mu\text{m}$ , and the layer thickness was checked by Raman measurement (514 nm, inVia Renishaw). The Raman characterization shows peak distance of  $19\,\text{cm}^{-1}$  for  $E_{2g}^1$  and  $A_{1g}$ , suggesting the MoS<sub>2</sub> flakes are single layered. To transfer the MoS<sub>2</sub> flakes to Si substrate covered by 300 nm thermal SiO<sub>2</sub>, the sample was first spin coated with PMMA A4 at 3000 rpm and baked at 130 °C for 2 min, then soaked in 10% KOH at 80 °C for hours until the PMMA membrane was separated

**Figure 5.** (a) Transfer curves measured at different temperatures for transistor with 2-nm AlN/18-nm  $Al_2O_3$  gate dielectric. The sweep time is 70 s and the drain bias is 0.1 V. Insets show the zoomed-in transfer curves during the up- and down-sweep. (b) Hysteresis extracted from (a).

**Figure 6.** (a) Normalized current power spectra  $S_{\rm I_D}/I_{\rm D}^2$  for different gate biases at 25 °C for transistor with 2-nm AlN/18-nm Al<sub>2</sub>O<sub>3</sub> gate dielectric. The inset shows the average sampled  $I_{\rm D}$  (red) during the power spectrum measurement in comparison with the swept transfer curve (black). (b)  $S_{\rm ID}/I_{\rm D}^2$  at 1 Hz and fitted frequency exponent  $\gamma$  for different temperatures. (c) Plots of  $S_{\rm ID}/I_{\rm D}^2$  at 1 Hz and  $(g_{\rm m}/I_{\rm D})^2$  versus  $I_{\rm D}$ . (d) Hooge parameter  $\alpha_{\rm H}$  extracted from (c).

from the sapphire substrate and floated on the water surface. The PMMA membrane was fished to DIW for several times and finally fished to the Si target substrate.

**Transistor Fabrication.** Source/drain contacts were first formed by EBL (Raith e-line), followed by e-beam evaporation of 10-nm Ti and 50-nm Au and lift-off in acetone. MoS<sub>2</sub> flakes were then patterned to the desired channel size by EBL and O<sub>2</sub> plasma etch. Both AlN and Al<sub>2</sub>O<sub>3</sub> were deposited using the Oxford Instruments OpAL ALD system. AlN was deposited at 170 °C by using trimethylaluminum (TMA) and remote N<sub>2</sub> plasma (20 sccm with a coil power of 25 W) as Al and N sources. The growth temperature and the RF power were

optimized to minimize the plasma damage to the MoS<sub>2</sub>, resulting in a relatively slow growth rate of  $0.18\,\text{Å/cycle}$ . After the deposition of AlN, Al<sub>2</sub>O<sub>3</sub> was grown *in-situ* under thermal ALD mode at 200 °C by using TMA and water vapor as Al and O sources. Two kinds of AlN/Al<sub>2</sub>O<sub>3</sub> dielectric stacks consisting of 2-nm AlN/18-nm Al<sub>2</sub>O<sub>3</sub> or 1-nm AlN/5-nm Al<sub>2</sub>O<sub>3</sub> are deposited. The thicknesses of AlN and Al<sub>2</sub>O<sub>3</sub> were verified by ellipsometer on the Si dummy wafer (J.A. Woollam M-2000V). During the measurement, 1.5 nm native SiO<sub>2</sub> layer was taken into consideration. A Cauchy dielectric model for AlN was developed by fitting the Ellipsometer data measured from 18.5 nm AlN. Another EBL was conducted to define the 3- $\mu$ m-long gate electrode made of Ti/Au (10 nm/50 nm). Finally the source and drain contact holes were formed by EBL and wet etch in FHD-5 for 10 min. After the fabrication, no further annealing was conducted.

**Characterization.** The successful deposition of AlN and Al $_2$ O $_3$  thin films was verified by TOF-SIMS V (ION-TOF GmbH, Münster, Germany), with an analysis spot size of  $41\,\mu\text{m} \times 41\,\mu\text{m}$ . The surface of MoS $_2$  after deposition was checked by AFM (XE150S, Park system). The cross-sectional view of MoS $_2$ /AlN/Al $_2$ O $_3$  was done by TEM (JEOL 2010F). The electric device performances were measured by Agilent B1505A device analyzer/curve tracer, inside a probe station equipped with a thermal chuck. To measure the low frequency noise, the transistor was first biased at a fixed gate voltage and drain voltage ( $V_D = 0.1\,V$ ), then the drain current was amplified by the low noise current preamplifier (SR570, Stanford Research System) and sampled for a total time of 120 s. Later on Fourier transformation was performed to the recorded current for every 4 s, and the final single-sided current power spectrum was obtained by averaging the 30 independent results.

### References

- 1. Radisavljevic, B., Radenovic, A., Brivio, J., Giacometti, V. & Kis, A. Single-Layer MoS<sub>2</sub> Transistors. *Nat. Nanotechnol.* **6,** 147–150 (2011).

- 2. Yoon, Y., Ganapathi, K. & Salahuddin, S. How Good Can Monolayer MoS<sub>2</sub> Transistors Be? Nano Lett. 11, 3768-3773 (2011).

- 3. Das, S., Chen, H., Penumatcha, A. V. & Appenzeller, J. High Performance Multilayer MoS<sub>2</sub> Transistors with Scandium Contacts. *Nano Lett.* **13**, 100–105 (2013).

- 4. Mak, K. F., Lee, C., Hone, J., Shan, J. & Heinz, T. F. Atomically Thin MoS<sub>2</sub>: A New Direct-Gap Semiconductor. *Phys. Rev. Lett.* **105** (2010).

- 5. Liu, H., Neal, A. T. & Ye, P. D. Channel Length Scaling of MoS<sub>2</sub> MOSFETs. ACS Nano 6, 8563-8569 (2012).

- 6. Pu, J. et al. Highly Flexible MoS<sub>2</sub> Thin-Film Transistors with Ion Gel Dielectrics. Nano Lett. 12, 4013-4017 (2012).

- 7. Salvatore, G. A. et al. Fabrication and Transfer of Flexible Few-Layers MoS<sub>2</sub> Thin Film Transistors to Any Arbitrary Substrate. ACS Nano 7, 8809–8815 (2013).

- 8. Lee, G. et al. Flexible and Transparent MoS<sub>2</sub> Field-Effect Transistors on Hexagonal Boron Nitride-Graphene Heterostructures. ACS Nano 7, 7931–7936 (2013).

- 9. Lopez-Sanchez, O., Lembke, D., Kayci, M., Radenovic, A. & Kis, A. Ultrasensitive Photodetectors Based on Monolayer MoS<sub>2</sub>. *Nat. Nanotechnol.* **8**, 497–501 (2013).

- 10. Tsai, D. et al. Few-Layer MoS<sub>2</sub> with High Broadband Photogain and Fast Optical Switching for Use in Harsh Environments. ACS Nano 7, 3905–3911 (2013).

- 11. Perkins, F. K. et al. Chemical Vapor Sensing with Monolayer MoS<sub>2</sub>. Nano Lett. 13, 668–673 (2013).

- 12. Wu, W. et al. Piezoelectricity of Single-Atomic-Layer MoS<sub>2</sub> for Energy Conversion and Piezotronics. Nature 514, 470-474 (2014).

- Qi, J. et al. Piezoelectric Effect in Chemical Vapour Deposition-Grown Atomic-Monolayer Triangular Molybdenum Disulfide Piezotronics. Nat. Commun. 6, 7430 (2015).

- Mak, K. F., He, K., Shan, J. & Heinz, T. F. Control of Valley Polarization in Monolayer MoS<sub>2</sub> by Optical Helicity. Nat. Nanotechnol. 7, 494–498 (2012).

- Zeng, H., Dai, J., Yao, W., Xiao, D. & Cui, X. Valley Polarization in MoS<sub>2</sub> Monolayers by Optical Pumping. Nat. Nanotechnol. 7, 490–493 (2012).

- Kang, K. et al. High-Mobility Three-Atom-Thick Semiconducting Films with Wafer-Scale Homogeneity. Nature 520, 656–660 (2015).

- Park, W. et al. Oxygen Environmental and Passivation Effects on Molybdenum Disulfide Field Effect Transistors. Nanotechnology 24, 95202 (2013).

- 18. Late, D. J., Liu, B., Matte, H. S. S. R., Dravid, V. P. & Rao, C. N. R. Hysteresis in Single-Layer MoS<sub>2</sub> Field Effect Transistors. ACS Nano 6, 5635–5641 (2012).

- Cho, K. et al. Electric Stress-Induced Threshold Voltage Instability of Multilayer MoS<sub>2</sub> Field Effect Transistors. ACS Nano 7, 7751–7758 (2013).

- 20. Sangwan, V. K. et al. Low-Frequency Electronic Noise in Single-Layer MoS<sub>2</sub> Transistors. Nano Lett. 13, 4351-4355 (2013).

- 21. Yang, J. et al. Improved Growth Behavior of Atomic-Layer-Deposited High-k Dielectrics on Multilayer MoS<sub>2</sub> by Oxygen Plasma Pretreatment. ACS Appl. Mater. Interfaces 5, 4739–4744 (2013).

- 22. McDonnell, S. et al. HfO<sub>2</sub> on MoS<sub>2</sub> by Atomic Layer Deposition: Adsorption Mechanisms and Thickness Scalability. ACS Nano 7, 10354–10361 (2013).

- 23. Cheng, L. et al. Atomic Layer Deposition of A High-k Dielectric on MoS<sub>2</sub> Using Trimethylaluminum and Ozone. ACS Appl. Mater. Interfaces 6, 11834–11838 (2014).

- Zou, X. et al. Interface Engineering for High-Performance Top-Gated MoS<sub>2</sub> Field-Effect Transistors. Adv. Mater. 26, 6255–6261 (2014).

- 25. Yang, W. et al. The Integration of Sub-10 nm Gate Oxide on MoS<sub>2</sub> with Ultra Low Leakage and Enhanced Mobility. Scientific reports 5, 11921 (2015).

- 26. Wang, H. et al. Integrated Circuits Based on Bilayer MoS<sub>2</sub> Transistors. Nano Lett. 12, 4674–4680 (2012).

- 27. Ma, N. & Jena, D. Charge Scattering and Mobility in Atomically Thin Semiconductors. Phys. Rev. X 4 (2014).

- 28. Dean, C. R. et al. Boron Nitride Substrates for High-Quality Graphene Electronics. Nat. Nanotechnol. 5, 722-726 (2010).

- 29. Watanabe, K., Taniguchi, T. & Kanda, H. Direct-Bandgap Properties and Evidence for Ultraviolet Lasing of Hexagonal Boron Nitride Single Crystal. *Nat. Mater.* **3**, 404–409 (2004).

- 30. Shi, Y. et al. Synthesis of Few-Layer Hexagonal Boron Nitride Thin Film by Chemical Vapor Deposition. Nano Lett. 10, 4134–4139 (2010).

- 31. Wu, C. I., Kahn, A., Hellman, E. S. & Buchanan, D. N. E. Electron Affinity at Aluminum Nitride Surfaces. *Appl. Phys. Lett.* **73**, 1346 (1998).

- 32. Huang, S., Jiang, Q., Yang, S., Zhou, C. & Chen, K. J. Effective Passivation of AlGaN/GaN HEMTs by ALD-Grown AlN Thin Film. *IEEE Electron Device Lett.* 33, 516–518 (2012).

- 33. Van Bui, H. et al. Self-Limiting Growth and Thickness- and Temperature- Dependence of Optical Constants of ALD AlN Thin Films. ECS J. Solid State Sci. Technol. 3, P101–P106 (2014).

- 34. Yang, S. et al. High-Quality Interface in Al<sub>2</sub>O<sub>3</sub>/GaN/AlGaN/GaN MIS Structures With *In Situ* Pre-Gate Plasma Nitridation. *IEEE Electron Device Lett.* **34**, 1497–1499 (2013).

- Liu, S. et al. Interface/Border Trap Characterization of Al<sub>2</sub>O<sub>3</sub>/AlN/GaN Metal-Oxide-Semiconductor Structures with An AlN Interfacial Layer. Appl. Phys. Lett. 106, 51605 (2015).

- 36. Lee, C. et al. Anomalous Lattice Vibrations of Single- and Few-Layer MoS2. ACS Nano 4, 2695-2700 (2010).

- 37. Jeon, J. et al. Layer-Controlled CVD Growth of Large-Area Two-Dimensional MoS<sub>2</sub> Films. Nanoscale 7, 1688-1695 (2015).

- 38. Amani, M. et al. Electrical Performance of Monolayer MoS<sub>2</sub> Field-Effect Transistors Prepared by Chemical Vapor Deposition. Appl. Phys. Lett. 102, 193107 (2013).

- 39. Liu, H. et al. Statistical Study of Deep Submicron Dual-Gated Field-Effect Transistors on Monolayer Chemical Vapor Deposition Molybdenum Disulfide Films. Nano Lett. 13, 2640–2646 (2013).

- 40. Amani, M. et al. Growth-substrate induced performance degradation in chemically synthesized monolayer MoS<sub>2</sub> field effect transistors. Appl. Phys. Lett. **104**, 203506 (2014).

- Yang, R., Wang, Z. & Feng, P. X. Electrical Breakdown of Multilayer MoS<sub>2</sub> Field-Effect Transistors with Thickness-Dependent Mobility. Nanoscale 6, 12383–12390 (2014).

- 42. Chen, M. et al. Stable Few-Layer MoS<sub>2</sub> Rectifying Diodes Formed by Plasma-Assisted Doping. Appl. Phys. Lett. **103**, 142110 (2013).

- 43. Egginger, M., Bauer, S., Schwödiauer, R., Neugebauer, H. & Sariciftci, N. S. Current Versus Gate Voltage Hysteresis in Organic Field Effect Transistors. *Monatsh. Chem.* **140**, 735–750 (2009).

- 44. Sze, S. M. & Kwok, K. N. Physics of Semiconductor Devices (Wiley-Interscience, 2007)

- 45. Zhao, C., Zhao, C., Taylor, Ś. & Chalker, P. Review on Non-Volatile Memory with High-k Dielectrics: Flash for Generation Beyond 32 nm. *Materials* 7, 5117–5145 (2014).

- Jiang, C., Rumyantsev, S. L., Samnakay, R., Shur, M. S. & Balandin, A. A. High-Temperature Performance of MoS<sub>2</sub> Thin-Film Transistors: Direct Current and Pulse Current-Voltage Characteristics. J. Appl. Phys. 117, 64301 (2015).

- Ghibaudo, G. & Boutchacha, T. Electrical Noise and RTS Fluctuations in Advanced CMOS Devices. Microelectron. Reliab. 42, 573–582 (2002).

- 48. Vanamme, L. K. J. Noise as A Diagnostic-Tool for Quality And Reliability of Electronic Devices. *IEEE Trans. Electron Devices* 41, 2176–2187 (1994).

- 49. Ghibaudo, G., Roux, O., Nguyenduc, C., Balestra, F. & Brini, J. Improved Analysis of Low Frequency Noise in Field-Effect MOS Transistors. *Phys. Status Solidi A* 124, 571–581 (1991).

# Acknowledgements

This work was financially supported by N\_HKUST636/13. The authors would like to thank all the supports from the technical staffs in Nanoelectronics Fabrication Facility (NFF) and Material Characterization and Preparation Facility (MCPF) of The Hong Kong University of Science and Technology.

### **Author Contributions**

K.J.C. and Q.Q. conceived the experiments. F.L., Y.X. and R.Y. synthesized the MoS<sub>2</sub> flakes. Q.Q., M.H. and Z.Z. fabricated the devices. B.L. helped with the EBL procedure. Q.Q. conducted the ALD deposition and test of devices. Q.Q. and M.H. performed the SIMS/TEM characterizations. K.J.C., Q.Q. and B.L. wrote the manuscript. All authors reviewed the manuscript.

# **Additional Information**

**Supplementary information** accompanies this paper at http://www.nature.com/srep

**Competing financial interests:** The authors declare no competing financial interests.

**How to cite this article**: Qian, Q. *et al.* Improved Gate Dielectric Deposition and Enhanced Electrical Stability for Single-Layer MoS<sub>2</sub> MOSFET with an AlN Interfacial Layer. *Sci. Rep.* **6**, 27676; doi: 10.1038/srep27676 (2016).

This work is licensed under a Creative Commons Attribution 4.0 International License. The images or other third party material in this article are included in the article's Creative Commons license, unless indicated otherwise in the credit line; if the material is not included under the Creative Commons license, users will need to obtain permission from the license holder to reproduce the material. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/