# SCIENTIFIC REPORTS

Received: 19 March 2015 Accepted: 16 July 2015 Published: 08 September 2015

## **OPEN** Stacked 3D RRAM Array with **Graphene/CNT as Edge Electrodes**

Yue Bai<sup>1</sup>, Huaqiang Wu<sup>1,2</sup>, Kun Wang<sup>1</sup>, Riga Wu<sup>3</sup>, Lin Song<sup>1</sup>, Tianyi Li<sup>4</sup>, Jiangtao Wang<sup>4</sup>, Zhiping Yu<sup>1,2</sup> & He Qian<sup>1,2</sup>

There are two critical challenges which determine the array density of 3D RRAM: 1) the scaling limit in both horizontal and vertical directions; 2) the integration of selector devices in 3D structure. In this work, we present a novel 3D RRAM structure using low-dimensional materials, including 2D graphene and 1D carbon nanotube (CNT), as the edge electrodes. A two-layer 3D RRAM with monolayer graphene as edge electrode is demonstrated. The electrical results reveal that the RRAM devices could switch normally with this very thin edge electrode at nanometer scale. Meanwhile, benefited from the asymmetric carrier transport induced by Schottky barrier at metal/CNT and oxide/ CNT interfaces, a selector built-in 3D RRAM structure using CNT as edge electrode is successfully fabricated and characterized. Furthermore, the discussion of high array density potential is presented.

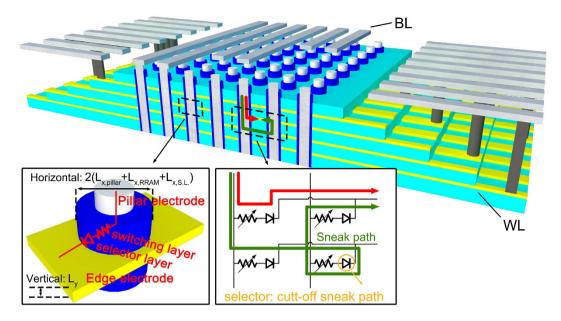

The growing demands in high-density memories drive the rapid development of advanced memory technologies. As one of the most promising emerging non-volatile memory (NVM) devices, oxide-based resistive switching memory (RRAM) has attracted significant interests due to the super endurance, fast switching speed, low power consumption and good CMOS compatibility<sup>1-7</sup>. On the other hand, current flash technology also found a way to overcome its scaling limit by adopting three dimensional (3D) structure to achieve high density<sup>8,9</sup>. The 3D RRAM approach, which combines the advantages of excellent electrical performances in RRAM cell and high density of 3D configuration, becomes a very attractive candidate for next generation high density NVM applications<sup>10-12</sup>. Since various 3D RRAM structures have been proposed, in this article, the 3D RRAM structure specifically refers to a typical architecture which is shown in Fig. 1: the RRAM cell is consisted with vertical resistive switching layer on the side wall of the drilled hole, vertical metal pillar as one electrode, and the edge of metal plane as the other electrode. Figure 1 shows that, different from planar RRAM, the effective area, Seffective, of 3D RRAM cell could be calculated as:

$$S_{effective} = L_y \times L_{effective} \tag{1}$$

Where L<sub>v</sub> and L<sub>effective</sub> represent the thicknesses of the metal plane and the effective perimeter which is in touch with resistive switching layer at horizontal direction. For traditional metal plane electrode based 3D RRAM, since it has cylindrical shape with surrounding electrode, the L<sub>effective</sub> could be calculated as:

$$L_{effective} = 2\pi \left( L_{x,TE} + L_{x,RRAM} + L_{x,S.L} \right)$$

<sup>(2)</sup>

Where L<sub>x,pillar</sub>, L<sub>x,RRAM</sub>, L<sub>x,S.L.</sub> represent thicknesses of pillar electrode, resistive switching layer and selector layer respectively. Previous studies on planar RRAM structure have already shown that 3 nm RRAM device could deliver normal resistive switching performances<sup>13</sup>. Therefore, to evaluate the potential of 3D RRAM in competing with 3D NAND, two critical questions should be addressed. 1) Literatures have

<sup>1</sup>Institute of Microelectronics, Tsinghua University, Beijing, China, 100084. <sup>2</sup>Tsinghua National Laboratory for Information Science and Technology (TNList), Beijing, China, 100084. 3Inner Mongolia University, Hohhot, Inner Mongolia, China, 010021. 4State Key Laboratory of Low-Dimensional Quantum Physics, Department of Physics and Tsinghua-Foxconn Nanotechnology Research Center, Tsinghua University, Beijing 100084, China. Correspondence and requests for materials should be addressed to H.W. (email: wuhq@mail.tsinghua.edu.cn)

**Figure 1. The typical schematic of 3D RRAM architecture.** The sneak path currents exist in each vertical plane which dominates the maximum number of cells in the array. Therefore, the selector is a critical element to cut off the sneak path and achieve high density integration. The feature size scaling down of 3D RRAM can be divided into two parts: 1) the vertical direction decided by the thickness of metal plane; 2) the horizontal direction determined by the thickness of metal pillar, resistive switching layer and selector layer.

shown that metal plane edge electrode provides significant scaling benefit in vertical direction<sup>14,15</sup>. What is the scaling limit of  $L_y$ ? 2) How to find an efficient method to integrate a selector device? Similar to 2D crossbar structure, 3D RRAM array also has sneak path current issue, as shown in Fig. 1, which could be addressed by integrating a selector<sup>16</sup>. A few research groups chose an oxide layer insertion to create a selector in series<sup>10,17</sup>. However, the selector layer thicknesses ( $L_{x,S,L}$ ) in those approaches are even larger than that of switching layer ( $L_{x,RRAM}$ ), which limits the size scaling in horizontal direction<sup>10</sup>.

Recently, carbon based low dimensional materials, including carbon nanotube(CNT) and graphene, have drawn significant scientific and technological interests as the emerging interconnect solution<sup>18,19</sup>. Being only one or a few atomic layer thick, they represent the ultimate limit of size<sup>20</sup>. Meanwhile, the previous studies have shown that CNT and graphene electrode could bring better performance in planar RRAM structure<sup>21,22</sup>. In this work, we used graphene and CNT as the electrode materials to investigate the scaling limit in 3D RRAM structure. This study could answer if 3D RRAM cell would operate at sub-nanometer scale in vertical direction. Meanwhile, benefited from Schottky barrier, a selector could be self-integrated at the interface between resistive switching layer and CNT electrode. Through this innovative structure, the selector layer could be avoided and higher density could be achieved with smaller pitch in horizontal direction.

#### **Results and Disscussion**

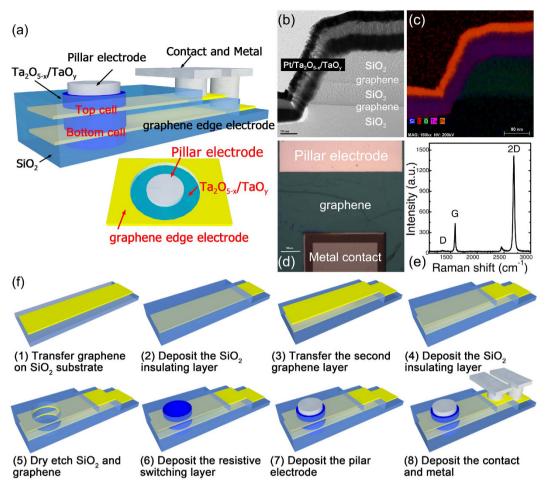

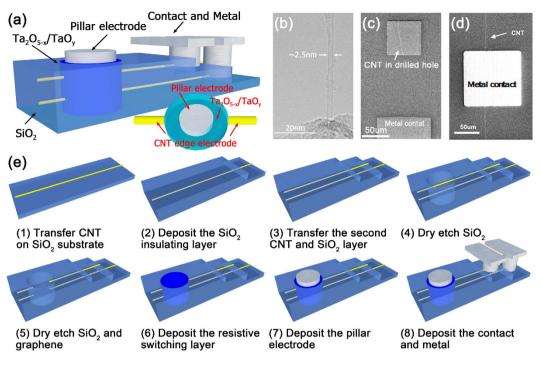

**Scaling in vertical direction (L<sub>y</sub> scaling down).** Two-layer 3D Ta<sub>2</sub>O<sub>5-x</sub>/TaO<sub>y</sub> RRAM cells are fabricated using monolayer graphene as the edge electrode. Figure 2(a) shows the schematic view of the device structure. The monolayer graphene was grown on the Pt substrate using CVD method and transferred to SiO<sub>2</sub> substrate by an electrochemical approach<sup>23</sup>. The Pt pillar and graphene layer serve as pillar electrode and edge electrode respectively, while the transitional metal oxide (TMO) resistive switching layer is located vertically on the sidewall between pillar electrode and edge electrode. Pd is chosen as the contact metal to graphene for signal output. The cross-sectional TEM image in Fig. 2(b) and magnified false-color EELS map in Fig. 2(c) show the typical structure of 3D Ta<sub>2</sub>O<sub>5-x</sub>/TaO<sub>y</sub> RRAM devices using monolayer graphene as the edge electrode. Figure 2(d) shows the optical top view of the monolayer graphene with pillar electrode and metal contact. Raman spectrum analysis was applied on the grown graphene layer, as shown in Fig. 2(e). The position and shape of G and 2D peaks in the spectrum confirm that the graphene used in the 3D RRAM structure is a monolayer graphene with thickness of ~0.3 nm.

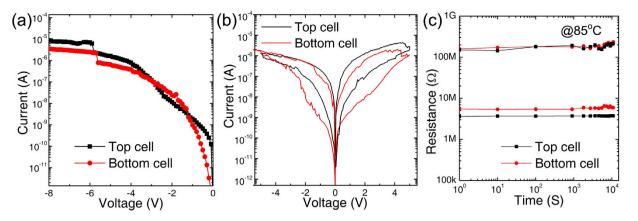

The electrical performance of two-layer 3D  $Ta_2O_{5-x}/TaO_y$  RRAM with graphene edge electrode is shown in Fig. 3. The successful forming operations of both top and bottom layer cells are shown in Fig. 3(a), with a forming voltage of -6V. Figure 3(b) shows the typical double I-V DC sweeping curves of top and bottom layer cells, with the SET and RESET voltages at -4.5V and 4.5V respectively. It shows a self-compliance property without external current limiting device in forming and SET operations.

**Figure 2.** (a) The Schematic diagram of two-layer 3D  $\text{Ta}_2O_{5-x}/\text{Ta}O_y$  RRAM with graphene edge electrode; the physical structure was characterized by (b) TEM image and (c) magnified false-color EELS map in cross-sectional view and (d) optical microscope image in top view; (e) the Raman spectra indicated the single layer graphene; (f) The fabrication flow of the single 3D RRAM cell.

Comparing to pervious 3D RRAM with Pt metal plane as the edge electrode<sup>11</sup>, graphene edge electrode device has much smaller operation current ( $\mu$ A with graphene edge electrode vs. ~mA with Pt metal plan edge electrode). One possible explanation is that, when the TaO<sub>y</sub> oxide layer contacts with graphene layer during deposition process, the edge of graphene could be oxidized. The previous studies have shown that, in the graphene/Ta<sub>2</sub>O<sub>5-x</sub>/TaO<sub>y</sub>/graphene system, a certain concentration of epoxide groups were grafted onto the basal plane of graphene<sup>24</sup>. As a result, the graphene is partially oxidized which increases contact resistance significantly. As a result, a high resistance region is generated at the interface between TaO<sub>y</sub> and graphene. Serving as an internal resistor, this high resistance region helps control the overshoot current and achieves self-compliance property during SET and forming operations. Figure 3(c) shows the retention test results where both HRS at 100 M\Omega and LRS at 10 M\Omega could be kept stable for more than 10<sup>4</sup> s at 85 °C.

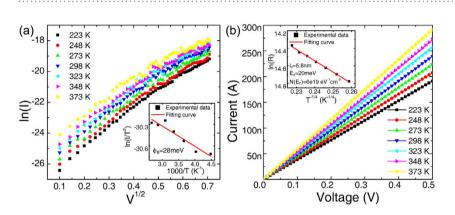

Furthermore, It is necessary to investigate the mechanism when the edge electrode scaling to sub-nanometer. Therefore, The temperature dependent transport characteristics in HRS and LRS are studied to understand the conduction mechanism. Figure 4 shows that electrical measurement results in HRS are well fitted with Schottky barrier emission. While the electron transport is facilitated by electron hopping for LRS state. The conduction mechanism is quite similar with our previous study<sup>11</sup>. Therefore we propose a possible switching mechanism of graphene electrode based 3D RRAM: The mechanism is still caused by the formation/rupture of conductive filaments. And the filaments formation/rupture happen at the pillar electrode Pt/Ta<sub>2</sub>O<sub>5-x</sub> interface, other than graphene/TaO<sub>y</sub> interface. During forming process, the oxygen vacancies in TaO<sub>y</sub> layer move to Ta<sub>2</sub>O<sub>5-x</sub> layer, at the Pt/Ta<sub>2</sub>O<sub>5-x</sub> the conductive filaments are formed. On the graphene/TaO<sub>y</sub> side, there are a lot of oxygen vacancies in TaO<sub>y</sub> which has good conductivity. Electrons could transport from graphene to TaO<sub>y</sub> easily and enough current could be supplied. Since the graphene electrode has little effects on this process, it is possible that the filament size is still in several-nanometers order, which could be larger than graphene electrode.

Figure 3. Electrical performance of two-layer 3D  $Ta_2O_{5-x}/TaO_y$  RRAM with graphene edge electrode: (a) Forming process of the cells in top and bottom layer which shows a self -compliance property without external device to limit the currents; (b) typical bipolar resistive switching; (c) retention measurement at 85 °C with 1 V read voltage.

Figure 4. The conductive mechanism of 3D  $Ta_2O_{5-x}/TaO_y$  RRAM with graphene edge electrode in (a) HRS and (b) LRS, fitted to Schottky emission model and electron hopping model respectively. Insets show the fitting curves and corresponding fitting parameters.

The above physical characterizations and electrical results prove the proposed 3D RRAM cell could switch successfully with monolayer graphene as edge electrode. This ultra-small feature size (~0.3 nm) confirms the 3D RRAM could scale down to sub-nanometer in vertical direction.

**Scaling in horizontal direction (L**<sub>x,S.L.</sub> **scaling down).** 3D RRAM has more challenges of scaling down in horizontal direction. Due to the sneak path current issue, as shown in Fig. 1, RRAM array would not work without a selector device in series. In previous studies,  $NbO_2^{17}$ ,  $TiO_x^{10.25}$  have been tried as the selector layer material in 3D RRAM cells. However, in published experimental results, the thickness of selector layer is almost double of the resistive switching layer. This causes it very challenge to achieve the continuing hole dimension scaling. Therefore, creative solutions for selector devices integration in 3D RRAM structure are very much desired.

A novel approach of using CNT as the edge electrode and a self-integrated selector is proposed and devices are fabricated. Figure 5(a) shows the schematic view of the 3D  $Ta_2O_{5-x}/TaO_y$  RRAM using CNT as the edge electrode. The effective area  $S_{effective}$  in this case is further reduced, which closes to the magnitude of CNT cross-section area. The fabrication process is similar to that of 3D RRAM with graphene edge electrode, as shown in Fig. 5(e). The CNT was synthesized on SiO<sub>2</sub> substrate directly by CVD method<sup>26</sup>. Figure 5(b) shows the TEM image of semiconducting CNT which confirms the single wall property with a diameter of 2.5 nm. Since CNT is tiny, it is very challenge to get good electrical contact between TMO and CNT. CNT could be etched away during the hole etching process and leaves no electrical contact or bad electrical contact between TMO and CNT: 1) etching the SiO<sub>2</sub> insulator layer using HF chemistry which wouldn't damage the CNT, as shown in Fig. 5(c); 2) etching the CNT using low power oxygen plasma in the drilled hole. Our experimental results showed that this two-step etching process could deliver repeatable and controllable holes without damaging CNT. In this 3D RRAM

**Figure 5.** (a) Schematic diagram of 3D  $Ta_2O_{5-x}/TaO_y$  RRAM with CNT edge electrode; (b) TEM image of CNT with a diameter about 2.5nm; (c) The top view SEM image of the drilled hole after etching SiO<sub>2</sub> layer without damaging the CNT electrode and (d) the metal contact Sc deposited on CNT; (e) The fabrication flow of the single 3D RRAM cell.

structure, metal Sc was chosen as the contact metal to CNT for signal output, as shown in Fig. 5(d). It is worth to point out that the architecture of CNT edge electrode based 3D RRAM array is different from the traditional 3D RRAM array (as shown in Fig. 1). To access each cell, the architecture in Figure S1 of supplemental material should be adopted which is suitable for other nanowire materials.

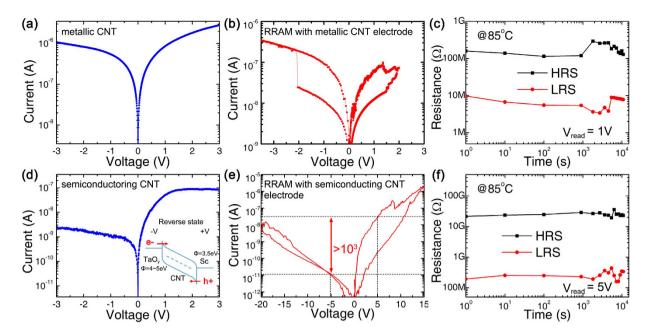

Figure 6 shows the electrical performance of the 3D  $Ta_2O_{5-x}/TaO_y$  RRAM with CNT edge electrode. Both metallic and semiconducting CNTs were investigated. The metallic CNT with  $TaO_y$  and Sc electrodes shows a near-ohmic behaviour as shown in Fig. 6(a). Following the transport property of CNT, the fabricated 3D RRAM device using metallic CNT as edge electrode has symmetrical I-V curve, as shown in Fig. 6(b). It confirms that 3D RRAM with metallic CNT edge electrode could switch successfully similar to the cell with graphene edge electrode. The cell retention measurement result shows that both HRS and LRS could be kept stable at  $100 M\Omega$  and  $10 M\Omega$  for more than  $10^4$  s at 85 °C, as shown in Fig. 6(c).

For semiconducting CNT as edge electrode case, a totally different transport property was observed, as shown in Fig. 6(d). It is believed that this asymmetrical I-V curve originates from the Schottky barrier formed between metal and semiconducting  $CNT^{27}$ . The Fermi level of Sc aligns, in an almost barrier-free manner, with the conductance band of CNT. While the valence band of CNT aligns with the Fermi level of TaO<sub>y</sub>. At reverse cut-off state with positive voltage on edge electrode and negative voltage on pillar electrode, the Schottky barriers block the hole transport at Sc/semiconducting CNT end and the electron transport at TaO<sub>y</sub>/semiconducting CNT end, as shown in the inset of Fig. 6(d). This built-in current rectifying characteristics of contacts between CNT with Sc and TaO<sub>y</sub> could serve as the built-in bi-directional selector for 3D RRAM without inserting any additional selector layer.

By choosing the metal contact Sc and TMO deposition sequence, the built-in selector could reduce the over-shoot current and sneak-path current simultaneously: During SET process with negative voltage on pillar electrode, the build-in selector is under reverse bias, which reduces the over-shoot current and achieve better self-compliance property. While in RESET process, the selector under forward bias supplies enough driving current to assist the resistive switching process. Figure 6(e) shows the switching behaviour of 3D RRAM integrated with semiconducting CNT edge electrode. The asymmetrical I-V curve is totally different from that of the devices with graphene or metallic CNT edge electrode. The LRS resistance on positive read bias is 1000 times of that on negative read bias. This transport property could reduce the sneak path current efficiently. This is because that at least one of the cells on sneak path would have negative bias. For the asymmetrical I-V devices, the equivalent resistance on sneak path will be more than 1000 time of that on selected cell. Additionally, it is noticed that the switching voltage in device with semiconducting CNT edge electrode is about 10 times larger than that in device with metallic CNT edge electrode. A possible reason is that a large series resistance is introduced at the contact between semiconducting CNT and TMO layer, which causes the effective voltage across the

Figure 6. Electrical performance of 3D  $Ta_2O_{5-x}/TaO_y$  RRAM with metallic CNT edge electrode: (a) the Semi-log I-V curves of CNT between  $TaO_y$  and Sc electrode; (b) the typical bipolar resistive switching; (c) the retention measurement at 85 °C with 1V read voltage. And electrical performance of device with semiconducting CNT BE: (a) the Semi-log I-V curves of CNT between  $TaO_y$  and Sc electrode, with the band-gap structure shown in the inset image; (b) the typical bipolar resistive switching with a rectification ratio more than  $10^3$ ; (c) the retention measurement at 85 °C with 5V read voltage.

RRAM reduced. In addition, the HRS and LRS of 3D RRAM with semiconducting CNT edge electrode could also be kept stable for more than  $10^4$ s at 85 °C at  $10 \text{ G}\Omega$  and  $100 \text{ M}\Omega$  with 5V read voltage, as shown in Fig. 6(f).

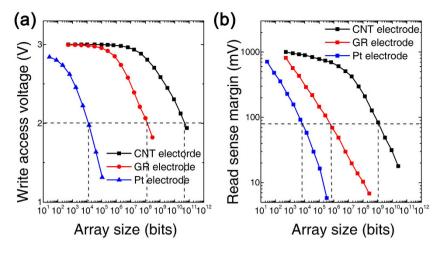

**Performance potential of 3D vertical RRAM array.** Since the 3D RRAM has been experimentally demonstrated at single cell level, it is important to evaluate the performance potential at the array level. Next, a simulation study is conducted to evaluate the 3D RRAM architecture with metal plane/2D/1D nano-materials. A resistor network model is constructed using SPICE method assisted by MATLAB. Three types of 3D RRAM cells, using Pt edge electrode, graphene edge electrode and semiconducting CNT edge electrode, have been compared based on measured data. Moreover, the interconnect resistance between neighboring cells is taken into account, following previous literature<sup>28</sup>. The simulation detail is described in the supplemental material.

Figure 7 show the performance of 3D RRAM with three types of edge electrodes at array level. The write access voltage versus array size in Fig. 7(a) shows the advantage of device with graphene and CNT edge electrodes. An obvious decline could be observed at 10<sup>4</sup> bits for device with Pt edge electrode. In contrast, for graphene and CNT edge electrode devices, the voltage degrade to 2 V when the array sizes increase to 10<sup>8</sup> bits and 10<sup>10</sup> bits. The decrease of write access voltage mainly comes from the interconnect resistance. With the array size increase, the equivalent resistance of interconnect is comparable with RRAM cells, which causes the divided voltage on selected cell decrease. Therefore the 3D RRAM with Pt edge electrode has the limited array size due to small HRS/LRS resistances. For 3D RRAM cells with graphene and CNT edge electrodes, the HRS/LRS resistances are 1000X larger. This property offers much large array size without write access voltage degradation.

Figure 7(b) shows the read sensing margin versus array size. By measuring the voltage difference in a 3D RRAM array when the selected cell is in HRS or LRS, the read sense margin could be evaluated. For three types of devices, hundreds mV read sense margin could be achieved when the array size is small. With array size increasing, it shows a sharp read sense margin decline in Pt edge electrode device due to cross talk issue. Again, benefited from the higher resistance and nonlinearity in HRS/LRS, the performance of graphene edge electrode device is improved. However, if the minimum read sense margin  $V_m = 80 \text{ mV}$  is set as the criterion<sup>29</sup>, the graphene edge electrode device could only support 10<sup>6</sup> bits which is still not good enough for high density applications. With semiconducting CNT edge electrode case, owing to the built-in selector benefit, the sneak path currents could be reduced efficiently and less voltage drops on other unselected cells. As a result, more than 10<sup>8</sup> bits array size could be achieved.

**Figure 7. 3D RRAM array performance with Pt, graphene (GR) and CNT edge electrode.** (a) The write access voltage of selected cell. (b) The read sense margin with a criterion of 80 mV.

.....

The simulation results show graphene/CNT edge electrode based 3D RRAM have better performance at array level, comparing with metal edge electrode based 3D RRAM. In addition, some non-ideal effects, such as non-uniformity, device imperfection, RTN noise, etc. are not included in the simulation. Although these effects will not affect the comparison results, they still need to be investigated in the future. The excellent vertical and horizontal scaling limits give 3D RRAM technology great potential in high density memory applications.

#### Conclusions

In this work, 3D RRAMs with graphene or CNT edge electrodes are demonstrated, to explore the vertical and horizontal scalability. In vertical direction, two-layer 3D  $Ta_2O_{5-x}/TaO_y$  RRAM cells with monolayer graphene as edge electrode are fabricated. 3D RRAM cells could switch normally with sub-nanometer electrode thickness. In horizontal direction, selector-layer free is realized by using 3D  $Ta_2O_{5-x}/TaO_y$  RRAM with semiconducting CNT edge electrode. In such case, the Schottky barriers formed at CNT/ Sc and CNT/TaO<sub>y</sub> contacts are served as the built-in selector. Based on the experimental and simulation results, different edge electrode material options are evaluated for high density application potential.

#### Methods Device Fabrication.

- (1) 3D Ta<sub>2</sub>O<sub>5-x</sub>/TaO<sub>y</sub> RRAM with graphene edge electrode: 1) Synthesize and transfer the first layer graphene to SiO<sub>2</sub> substrate. 2) Deposit 100 nm SiO<sub>2</sub> insulating layer by RF sputtering. 3) Synthesize and transfer the second layer graphene to SiO<sub>2</sub> substrate. 4) Deposit second SiO<sub>2</sub> insulating layer. 5) Pattern by lithography and ICP dry etch with C<sub>4</sub>F<sub>8</sub>/Ar to form the drilled holes. 6) Deposit the Ta<sub>2</sub>O<sub>5-x</sub>/TaO<sub>y</sub> TMO layer by RF reactive sputtering. 7) Pattern by lithography and deposit 30 nm Pt as the pillar electrode. 8) Pattern by lithography and deposit the 40 nm Pd as the contact metal on graphene.

- (2) 3D Ta<sub>2</sub>O<sub>5-x</sub>/TaO<sub>y</sub> RRAM with CNT edge electrode: 1) Synthesize CNT on SiO<sub>2</sub> substrate using CVD method. 2) Deposit 100 nm SiO<sub>2</sub> insulating layer by sputtering. 3) Pattern by lithography and wet etch the drilled hole without damaging the CNT. 4) Etch the CNT using oxygen plasma in the drilled hole. 5) Deposit the Ta<sub>2</sub>O<sub>5-x</sub>/TaO<sub>y</sub> TMO layer by reactive sputtering. 6) Pattern by lithography and deposit 30 nm Pt as the pillar electrode. 7) Pattern by lithography and deposit the 40 nm Sc as the contact metal on CNT.

### Material Synthesis.

- (1) Synthesize and transfer the graphene edge electrode. Pt foils were heated to  $1050 \,^{\circ}$ C in H<sub>2</sub> ambience. Then the reaction gases composed by CH<sub>4</sub> and H<sub>2</sub> were introduced into the growth quartz chamber with a total gas flow rate of 800sccm. The ratio of CH<sub>4</sub>:H<sub>2</sub> is 0.0078:1 and the substrates were soaked in the reaction gas mixture for 60 minutes before cooling down step. The synthesized graphene films were transferred to SiO<sub>2</sub> substrates by an electrochemical method<sup>23</sup>.

- (2) Synthesize the CNT edge electrode: The CNTs were synthesized by a CVD method<sup>26</sup>. Using ethanol and water as feed gases and Fe-Mo catalysts which were suspended in the air, the ultra-long CNT were grown directly on the SiO<sub>2</sub> substrates. After the growth of CNTs, the samples were annealed at 80 °C in a low pressure environment for 5 min to make the substrates more hydrophobic.

**Characterization Techniques.** The quality of graphene was characterized by Raman spectra (RENISHAW RM2000). The CNTs were observed using TEM (FEI Tecnai TF20) and SEM (QUANTA FEG450). The 3D RRAM cross-section structures were investigated by TEM, EELS (FEI Tecnai G2 F20) and FIB (FEI Nova600). The electrical characteristics were tested by Agilent B1500A semiconductor parameter analyzer and Agilent 81110A pulse generator with Cascade Summit 11000 probe station.

#### References

- Lee, M.-J. et al. A fast, high-endurance and scalable non-volatile memory device made from asymmetric Ta<sub>2</sub>O<sub>5-x</sub>/TaO<sub>2-x</sub> bilayer structures. Nat. Mater. 10, 625–630 (2011).

- Lee, H. Y. et al. Evidence and solution of over-RESET problem for HfOX based resistive memory with sub-ns switching speed and high endurance. in *Electron Devices Meeting (IEDM), 2010 IEEE International* 19.7.1–19.7.4 (2010), doi: 10.1109/ IEDM.2010.5703395.

- Tsai, C.-L., Xiong, F., Pop, E. & Shim, M. Resistive Random Access Memory Enabled by Carbon Nanotube Crossbar Electrodes. ACS Nano 7, 5360–5366 (2013).

- 4. Jo, S. H. & Lu, W. CMOS Compatible Nanoscale Nonvolatile Resistance Switching Memory. Nano Lett. 8, 392–397 (2008).

- Lv, H. et al. Evolution of conductive filament and its impact on reliability issues in oxide-electrolyte based resistive random access memory. Sci. Rep. 5, (2015), doi: 10.1038/srep07764.

- 6. Kim, K. M., Park, T. H. & Hwang, C. S. Dual Conical Conducting Filament Model in Resistance Switching TiO2 Thin Films. Sci. Rep. 5, (2015), doi: 10.1038/srep07844.

- 7. Pan, F., Gao, S., Chen, C., Song, C. & Zeng, F. Recent progress in resistive random access memories: Materials, switching mechanisms, and performance. *Mater. Sci. Eng. R Rep.* 83, 1–59 (2014).

- Choi, E.-S. & Park, S.-K. Device considerations for high density and highly reliable 3D NAND flash cell in near future. in *Electron Devices Meeting (IEDM), 2012 IEEE International* 9.4.1–9.4.4 (2012), doi: 10.1109/IEDM.2012.6479011.

- Lue, H.-T. et al. A novel dual-channel 3D NAND flash featuring both N-channel and P-channel NAND characteristics for bitalterable Flash memory and a new opportunity in sensing the stored charge in the WL space. in *Electron Devices Meeting (IEDM)*, 2013 IEEE International 3.7.1–3.7.4 (2013), doi: 10.1109/IEDM.2013.6724555.

- Hsu, C.-W. et al. 3D vertical TaO<sub>x</sub>/TiO<sub>2</sub> RRAM with over 103 self-rectifying ratio and sub-#x003BC;A operating current. in Electron Devices Meeting (IEDM), 2013 IEEE International 10.4.1–10.4.4 (2013), doi: 10.1109/IEDM.2013.6724601.

- 11. Bai, Y. et al. Study of Multi-level Characteristics for 3D Vertical Resistive Switching Memory. Sci. Rep. 4, (2014), doi: 10.1038/ srep05780.

- Gao, B. et al. Ultra-Low-Energy Three-Dimensional Oxide-Based Electronic Synapses for Implementation of Robust High-Accuracy Neuromorphic Computation Systems. ACS Nano 8, 6998–7004 (2014).

- Govoreanu, B. et al. Performance and reliability of Ultra-Thin HfO<sub>2</sub>-based RRAM (UTO-RRAM). in Memory Workshop (IMW), 2013 5th IEEE International 48–51 (2013), doi: 10.1109/IMW.2013.6582095.

- 14. Yu, S. et al. 3D vertical RRAM-Scaling limit analysis and demonstration of 3D array operation. in VLSI Technology (VLSIT), 2013 Symposium on, T158-T159, Kyoto, IEEE (2013).

- 15. Chen, H.-Y. et al. Experimental study of plane electrode thickness scaling for 3D vertical resistive random access memory. Nanotechnology 24, 465201 (2013).

- Lee, W. *et al.* High Current Density and Nonlinearity Combination of Selection Device Based on TaO<sub>x</sub>/TiO<sub>2</sub>/TaO<sub>x</sub> Structure for One Selector–One Resistor Arrays. ACS Nano 6, 8166–8172 (2012).

- 17. Cha, E. et al. Nanoscale (~10nm) 3D vertical ReRAM and NbO2 threshold selector with TiN electrode. in 10.5.1–10.5.4 (IEEE, 2013), doi: 10.1109/IEDM.2013.6724602.

- Smith, J. T., Franklin, A. D., Farmer, D. B. & Dimitrakopoulos, C. D. Reducing Contact Resistance in Graphene Devices through Contact Area Patterning. ACS Nano 7, 3661–3667 (2013).

- 19. Rao, R. *et al.* Graphene as an atomically thin interface for growth of vertically aligned carbon nanotubes. *Sci. Rep.* **3**, (2013), doi: 10.1038/srep01891.

- 20. Wang, L. et al. One-Dimensional Electrical Contact to a Two-Dimensional Material. Science 342, 614-617 (2013).

- Liao, A. D., Araujo, P. T., Xu, R. & Dresselhaus, M. S. Carbon nanotube network-silicon oxide non-volatile switches. *Nat. Commun.* 5, (2014), doi: 10.1038/ncomms6673.

- Chai, Y. et al. Resistive switching of carbon-based RRAM with CNT electrodes for ultra-dense memory. in Electron Devices Meeting (IEDM), 2010 IEEE International 9.3.1–9.3.4 (2010), doi: 10.1109/IEDM.2010.5703328.

- 23. Gao, L. *et al.* Repeated growth and bubbling transfer of graphene with millimetre-size single-crystal grains using platinum. *Nat. Commun.* **3**, 699 (2012).

- 24. Yang, Y. et al. Oxide Resistive Memory with Functionalized Graphene as Built-in Selector Element. Adv. Mater. 26, 3693–3699 (2014).

- Lee, D. et al. BEOL compatible (300 °C) TiN/TiOX/Ta/TiN 3D nanoscale (~10nm) IMT selector. in Electron Devices Meeting (IEDM), 2013 IEEE International 10–7 (2013), doi: 10.1109/IEDM.2013.6724604.

- Wang, X. et al. Fabrication of Ultralong and Electrically Uniform Single-Walled Carbon Nanotubes on Clean Substrates. Nano Lett. 9, 3137–3141 (2009).

- 27. Wang, S. et al. A Doping-Free Carbon Nanotube CMOS Inverter-Based Bipolar Diode and Ambipolar Transistor. Adv. Mater. 20, 3258–3262 (2008).

- Chen, H.-Y. et al. HfOx based vertical resistive random access memory for cost-effective 3D cross-point architecture without cell selector. in *Electron Devices Meeting (IEDM), 2012 IEEE International* 20.7.1–20.7.4 (2012), doi: 10.1109/IEDM.2012.6479083.

- Umemoto, Y. et al. 28 nm 50% Power-Reducing Contacted Mask Read Only Memory Macro With 0.72-ns Read Access Time Using 2T Pair Bitcell and Dynamic Column Source Bias Control Technique. IEEE Trans. Very Large Scale Integr. VLSI Syst. 22, 575–584 (2014).

#### Acknowledgement

This research was supported by the National Basic Research Program (2011CBA00600), the Hi-Tech Research and Development Program (2011AA010401) and the National Natural Science Foundation (61076115, 61006067).

#### **Author Contributions**

Y.B. and H.W. planned the project and wrote the manuscript; Y.B., K.W. and R.W. fabricated the device and made electrical measurement; Y.B. and L.S. contributed to RRAM array circuit model and made the simulation; T.L. and J.W. synthesize the carbon nanotube; Y.B., H.W., Z.Y. and H.Q. contributed to the conception of the experiment. All authors discussed the results and commented on the manuscript.

#### Additional Information

Supplementary information accompanies this paper at http://www.nature.com/srep

Competing financial interests: The authors declare no competing financial interests.

How to cite this article: Bai, Y. *et al.* Stacked 3D RRAM Array with Graphene/CNT as Edge Electrodes. *Sci. Rep.* **5**, 13785; doi: 10.1038/srep13785 (2015).

This work is licensed under a Creative Commons Attribution 4.0 International License. The images or other third party material in this article are included in the article's Creative Commons license, unless indicated otherwise in the credit line; if the material is not included under the Creative Commons license, users will need to obtain permission from the license holder to reproduce the material. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/