Abstract

We have demonstrated a printed electronic tag that monitors time-integrated sensor signals and writes to nonvolatile memories for later readout. The tag is additively fabricated on flexible plastic foil and comprises a thermistor divider, complementary organic circuits and two nonvolatile memory cells. With a supply voltage below 30 V, the threshold temperatures can be tuned between 0 °C and 80 °C. The time-temperature dose measurement is calibrated for minute-scale integration. The two memory bits are sequentially written in a thermometer code to provide an accumulated dose record.

Similar content being viewed by others

Introduction

Solution printing processes are well-suited for high-throughput, low-cost fabrication on flexible substrates. While tiny discrete CMOS chips have been incorporated into electronics systems on flexible substrates, the conventional solder-reflow bonding process for discrete chips typically requires high temperatures incompatible with polyethylene-based substrates. Print fabrication can be performed at lower temperatures, enabling the use of these lower-cost materials. Printing is also capable of covering large areas economically. Thus printed electronics are compelling for internet-of-things applications that require a large volume of devices, such as sensor networks and smart packaging. Recent advances in organic electronic circuits have demonstrated that sensing1,2,3,4, signal processing and conditioning5,6,7,8 and communications9,10 functionalities can be realized with solution-processed materials. Here we report on the development of an additively-printed organic circuit platform capable of processing sensor data and recording dose measurements to nonvolatile memories11,12,13 in an integrated tag. The tag demonstrates a system application for the case of time-temperature dose measurement, which can be used to track hazardous conditions or quantify spoilage in perishables. While previous examples of organic temperature sensing systems14,15 have focused on detecting a critical temperature threshold, there is a need to sense time-temperature dose (TTD) values to account for both critical temperature and exposure time limits. A TTD is a temperature-dependent time interval and can be measured, for example, to monitor spoilage affected by incubation temperature and duration. Moreover, the circuit platform can be generalized to measure other time-integrated sensor signal “doses”, for example, by replacing the thermistor with other resistive sensors such as strain gauges or chemical sensors, the printed circuits are potentially applicable to a variety of sensing applications.

One of the key features of this demonstration is the integration of multiple printing technologies and device types, including circuitry designed according to the constraints of an all-additive inkjet organic thin-film-transistor (OTFT) process, including the use of as few OTFTs as possible to maximize yield. Moreover, the limitations of organic circuits call for a design approach that focuses on utilizing the simplest circuit possible for a given application. For example, in this design, the tight matching tolerance required by a differential comparator would make it difficult to implement. In contrast the chosen inverter-based threshold circuit allows larger tolerance and is more suitable for this system. A significant challenge in the design is to achieve minute-scale integration times. Approaches such as multiplying integration time with a digital counter are not desirable because they require a substantial increase in the number of OTFTs. It is preferable to directly integrate charge for the full target interval, as is done here. A current signal generated by the sensor is integrated on a capacitor. When the integrated charge reaches a threshold, the circuit writes to a memory cell. The memory bits are sequentially written to form a thermometer-coded output. Each bit in the memory array represents a certain amount of charge, Q and the total number of bits written, m, indicates the total amount m*Q of integrated charge and the corresponding dose.

Methods

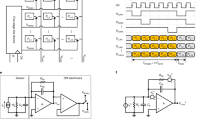

In comparison to conventional circuits, the variance and bias-stress stability of OTFT circuits are major concerns. Device-to-device variability is incorporated into SPICE simulation models using process corners16, to model the typical, minimum and maximum values of device current, which range from 0.33 to 2.0 times the typical value. Simulations are performed under each process corner to optimize sizing in OTFTs, resulting in the choices shown in the circuit schematic in Supplemental Figure S1. The changes in current and threshold voltage due to bias stress in operation are smaller than those associated with device-to-device variation in the existing OTFT process (Supplemental Figure S3). Hence the process corners are sufficient to account for the temporal variation due to bias stress.

In this prototype the components are fabricated on discrete plastic polyethylene naphthalate foils, which are bonded to a screen-printed silver interconnect substrate and connected by conductive silver ink. The transistor circuits are printed in sections to facilitate iteration, testing and integration as shown by the dashes in the circuit schematic of Supplemental Figure S1. In production, these circuit blocks could be combined, for example, in a roll-to-roll process. The screen-printed thermistor divider, provided by PST Sensors, comprises a silicon-nanoparticle thermistor and carbon resistor, both with nominal resistances of 50 MΩ at 25 °C. The nonvolatile memories are 80 μm × 80 μm ferroelectric capacitors patterned by gravure printing on polyethylene terephthalate foils. The memory dielectric is a PVDF copolymer thin film. For the Ta2O5 capacitors, the dielectric film is processed in ambient conditions by anodization of Ta gate metal at 75 V in a boric acid solution (0.4% by weight, adjusted to pH = 7 with NaOH) resulting in 400 nm Ta2O5 film. The complementary OTFT process is chosen from among available design styles, because complementary circuits17,18,19 consume less power than unipolar circuits, use fewer OTFTs than pseudo-CMOS circuits20 and require fewer process steps than dual-gate circuits21. Both p-channel22,23 and n-channel24,25,26 OTFTs are top-gate devices fabricated by inkjet printing, with average mobility of 0.1 cm2 V−1 s−1. The circuit design is based on a transistor channel length of 35 ± 5 μm. The materials, structure, typical current-voltage characteristics of the printed OTFTs are shown in supplemental Figures S2 and S3.

Results

The printed TTD measurement tag comprises a thermistor divider, complementary circuits (44 OTFTs in total) and two nonvolatile memory cells. The integrated sensor current triggers the sequential writing of the memory cells, which store a thermometer-coded record of zero, one, or two TTDs. The integrator circuit is reset between measurements. The block diagram and the photograph of the integrated tag are shown in Fig. 1.

The thermistor divider provided by PST Sensors consists of a silicon-nanoparticle thermistor and a carbon resistor. The thermistor shows a temperature coefficient of −1 MΩ/°C. As the thermistor resistance falls with increasing temperature, the divider output voltage Vin rises as is shown in Fig. 2. Due to the large variability in devices fabricated with printing processes, the sensor and OTFT circuits require calibration to adjust the bias voltage Vbias on the sensor to match the trigger threshold in the signal processing circuit. The temperature threshold of the tag can range from 0 °C to 80 °C and is calibrated by changing Vbias such that Vin matches the trip voltage of the gain stage at the desired minimum trigger temperature. For example, a bias of 20 V corresponds to a 40 °C threshold. With a 30 V bias, the thermistor divider output changes by approximately 0.1 V/°C and is linear near room temperature. The printed trigger circuits are stable to within 0.1 V during 10 minutes of continuous operation in laboratory conditions. Thus the tag has the potential to achieve ±1 °C accuracy after calibration and with intermittent recovery periods to reduce bias drift. This calibration accounts for the change in transistor characteristics with temperature during the measurement. However, additional studies are needed to determine the circuit’s long-term temperature stability.

For TTD measurements, the thermistor divider is combined with the integrating RC stage. To first order, the integration time is determined by the capacitor CTimer and the off-resistance Roff of OTFT MR. With a typical Roff value of 2 GΩ, the capacitor must have high capacitance value (>30 nF) and low leakage (<10 nA) to realize an RC delay of one minute. To meet these requirements, a 400-nm anodized Ta2O5 high-k dielectric film with a measured capacitance of 50 nF cm−1 is used for the capacitors. The tag has been operated with integration times ranging from 10 s (with Roff = 0.25 GΩ) to 400 s (Roff = 10 GΩ) by varying the gate bias on MR, with CTimer = 40 nF. For an alternative TTD circuit, the thermistor RT can be directly connected to CTimer for the integrating stage. However, this option is not implemented for minute-scale integration, because such a solution would require extremely high thermistor resistance values on the order of 1 GΩ and would be more sensitive to their accuracy.

As the integration capacitor is charged (Fig. 3), the voltage at node VA rises faster with higher

(a) Signals at node VA and WL1 as a function of time and Vin, where Vin varies from 7.2 V to 18.0 V in increments of 1.8 V. The dotted lines are based on double exponential fits. (b) The circuit integration time as a function of Vin. The Vin axis is converted to a temperature scale (inset), for an instance with thermistor divider calibrated to Vbias = 30 V.

Vin = Vbias*R/(RT + R). As Vin is increased, it takes less time to reach the trip voltage of the circuit set at 8 V, as indicated by the timing of the output pulses on memory wordline WL. With an input below the set point, for example Vin = 7.2 V, the output pulse will not be triggered. Above the set point, the trigger time is a function of Vin. With Vin = 18 V, a pulse is generated at time t = 40, whereas with Vin = 9 V, the pulse is at t = 130 s. This characteristic allows setting a dose threshold that is dependent on both the duration and the magnitude of an input signal. The VA voltage does not have a pure RC exponential characteristic, but can be fit with a double-exponential time dependence, according to  , with t0,a = 10 s and t0,b = 150 s. This is the result of non-linear channel resistances of MReset and MR, as well as electrical bias stress. The integration time tintegration with respect to Vin is shown in Fig. 3(b) and this data fits the natural logarithmic equation tintegration = 36.2 ln (Vin−8) +124.8. The inset axis of Fig. 3(b) shows the temperature correspondence of Vin with the thermistor divider at Vbias = 30 V. From this calibration, one can infer that, for example, if the sample is held at 37 °C for longer than 70 s, or at 66 °C for longer than 50 s, the circuit will trigger and record the TTD into a memory cell.

, with t0,a = 10 s and t0,b = 150 s. This is the result of non-linear channel resistances of MReset and MR, as well as electrical bias stress. The integration time tintegration with respect to Vin is shown in Fig. 3(b) and this data fits the natural logarithmic equation tintegration = 36.2 ln (Vin−8) +124.8. The inset axis of Fig. 3(b) shows the temperature correspondence of Vin with the thermistor divider at Vbias = 30 V. From this calibration, one can infer that, for example, if the sample is held at 37 °C for longer than 70 s, or at 66 °C for longer than 50 s, the circuit will trigger and record the TTD into a memory cell.

Figure 4 shows an overview of the tag signals during operation with a supply voltage of Vdd = 28 V and the circuit nodes as labeled in Supplemental Figure S1. When VA reaches the trip point of the gain stage at t = 20 s, the gain stage sends a falling edge to node VB. This node is connected to two pulse-generator circuits, one for writing to the memory word lines (WL1, WL2) and the other for generating pulses at VC to reset the integrator and at VD to set the RS latch, which addresses the memory and is reset at start-up. With a larger memory array, a shift register and a demultiplexor could be used instead of the RS latch. The pulse generators are NOR-based monostable multivibrators. Two pulse generators with a delay between the respective signals are used to accommodate the required delay of the control signals, ensuring that the first memory cell is fully written before the RS latch is set, as well as to satisfy the different requirements of the reset and memory-write pulses. Even with the augmented on/off ratio provided by the inverter in the reset circuit, a wide pulse (realized by the addition of CSlow = 6 nF) is needed to ensure discharge of the CTimer capacitor to ground and reset the integrator. The pulse widths are also dependent on the slope of the input edge, which is shallow enough that the average pulse width is on the order of 1 s. The pulse waveform generated by the write-pulse generator is used to write memory cells; for data retrieval, the nonvolatile memory cells are read with an external charge amplifier reader unit, following the procedure in Ref. 16. If a pulse with voltage magnitude above 17 V is applied to a memory cell, it is written to state “0”, which appears at the reader output as the large amplitude waveform in supplemental Figure S4(c). However, if there is no pulse or if the pulse amplitude is below 5 V as in the case of a disabled word line (e.g., WL2 in Fig. 4), the memory bit remains in its default state “1”, corresponding to the relatively lower amplitude waveform in supplemental Figure S4(d).

Measured signals at the circuit nodes indicated in Supplemental Figure S1 with input voltage Vin = 20 V and supply voltage VDD = 28 V.

In Fig. 4 while a pulse is passed to WL1, WL2 is maintained below 3 V and the second memory cell is not written. When the RS latch is set after the first memory bit has been written, WL1 is disabled and WL2 is enabled to address the second memory cell. Figure 5 shows the WL1 and WL2 waveforms during a long exposure event equivalent to two doses. The sequential writing of memory cells demonstrates that the thermometer-code recording method is successfully implemented. During initialization, the memory cells are set to state “1”. In the inverted thermometer encoding used, when there is no threshold event, the two memory cells remain in the default state and the readout result is “11”. Upon the first dose event, the first cell switches state and the 2-bit readout will be “01”. After the second dose, the readout will be “00”. Thus, three combinations of the two-bit memory are possible. The combination “10” is not valid as the second cell is never written without the first cell having been previously written. The two written memory cells provide an accumulated record of events of exposure of the sample to conditions above the dose limit. Moreover, if Vin decreases during the course of a measurement, as by a reduction in temperature, the duration of this disruption is accounted for in the total integration time (supplemental Figure S5). High supply voltage was used in this demonstration, but recent results in using high-k dielectrics19 for printed OTFTs will enable the dose tag to operate at a decreased supply voltage in the future.

Conclusions

We have demonstrated a printed sensor platform that monitors minute-scale-duration temperature doses and records the dose events in two thermometer-coded nonvolatile memory cells. This integrated organic electronic system uses a low-transistor-count design to boost yield for practical print fabrication on flexible plastic foils. If integrated with an appropriate power supply, the tag could operate as a standalone system, with nonvolatile memory for later readout. Threshold temperatures can be calibrated between 0 °C and 80 °C, covering a wide range of applications in food and medicine spoilage. In addition to temperature sensing, the system is compatible with other current-based sensors, and, by scaling up the memory addressing circuit, it can be readily extended larger memory arrays to store more data. The development of this tag is a promising step towards economical printed sensor systems.

Additional Information

How to cite this article: Ng, T. N. et al. Printed dose-recording tag based on organic complementary circuits and ferroelectric nonvolatile memories. Sci. Rep. 5, 13457; doi: 10.1038/srep13457 (2015).

References

Arias, A. C., MacKenzie, J. D., McCulloch, I., Rivnay, J. & Salleo, A. Materials and Applications for Large Area Electronics: Solution-Based Approaches. Chem. Rev. 110, 3–24 (2010).

Ishida, K. et al. Insole Pedometer with Piezoelectric Energy Harvester and 2V Organic Circuits. IEEE J. Solid-State Circuits. 48, 255–264 (2013).

Hammock, M. L., Chortos, A., Tee, B. C.-K., Tok, J. B.-H. & Bao, Z. 25th Anniversary Article: The Evolution of Electronic Skin (E-Skin): A Brief History, Design Considerations and Recent Progress. Adv. Mater. 25, 5997–6038 (2013).

Mabeck, J. T. & Malliaras, G. G. Chemical and Biological Sensors Based on Organic Thin-Film Transistors. Anal. Bioanal. Chem. 384, 343–353 (2006).

Myny, K., Veenendaal, E. Van, Gelinck, G. H. & Genoe, J. An 8-Bit, 40-Instructions-Per-Second Organic Microprocessor on Plastic Foil. IEEE J. Solid-State Circuits. 47, 284–291 (2012).

Li, F., Nathan, A., Wu, Y. & Ong, B. S. Organic Thin Film Transistor Integration: A Hybrid Approach. (Wiley-V C H Verlag Gmbh, 2011).

Zaki, T. et al. Digital-to-Analog Converter Using Organic P-Type Thin-Film Transistors on Glass. IEEE J. Solid-State Circuits 47, 292–300 (2012).

Maiellaro, G. et al. High-Gain Operational Transconductance Amplifiers in a Printed Complementary Organic TFT Technology on Flexible Foil. IEEE Trans. Circuits Syst. 60, 3117–3125 (2013).

Jung, M. et al. All-Printed and Roll-to-Roll-Printable Tag on Plastic Foils. IEEE Trans. Electron Devices 57, 571–580 (2010).

Cantatore, E. et al. A 13 . 56-MHz RFID System Based on Organic Transponders. IEEE J. Solid-State Circuits 42, 84–92 (2007).

Sekitani, T. et al. Organic Nonvolatile Memory Transistors for Flexible Sensor Arrays. Science (80-.). 326, 1516–1519 (2009).

Naber, R. C. G., Asadi, K., Blom, P. W. M., de Leeuw, D. M. & de Boer, B. Organic Nonvolatile Memory Devices Based on Ferroelectricity. Adv. Mater. 22, 933–945 (2010).

Baeg, K.-J. et al. High-Performance Top-Gated Organic Field-Effect Transistor Memory using Electrets for Monolithic Printed Flexible NAND Flash Memory. Adv. Funct. Mater. 22, 2915–2926 (2012).

He, D. D. et al. An Integrated Organic Circuit Array for Flexible Large-Area Temperature Sensing. Proc. Int. Solid-State Circuits Conf. San Francisco,: USA. IEEE,. 10.1109/ISSCC.2010.5434013. 142–143 (2010 Feb 7–11).

Ganesan, R., Pankalla, S., Ludwig, K. & Glesner, M. Design of an Organic Electronic Label on a Flexible Substrate for Temperature Sensing. Proc. Eur. Solid-State Circuit Conf. Bucharest, Romania. 10.1109/ESSCIRC.2013.6649163. 423–426 (2013 Sep 16–20).

Ng, T. N. et al. Scalable Printed Electronics: an Organic Decoder Addressing Ferroelectric Non-Volatile Memory. Sci. Rep. 2, 585 (2012).

Bode, D. et al. Noise-Margin Analysis for Organic Thin-Film Complementary Technology. IEEE Trans. Electron Devices 57, 201–208 (2010).

Schwartz, D. E. & Ng, T. N. Comparison of Static and Dynamic Printed Organic Shift Registers. IEEE Electron Device Lett. 34, 271–273 (2013).

Mei, P. et al. Utilizing High Resolution and Reconfigurable Patterns in Combination with Inkjet Printing to Produce High Performance Circuits. Appl. Phys. Lett. 105, 123301 (2014).

Huang, T.-C. et al. Pseudo-CMOS: A Design Style for Low-Cost and Robust Flexible Electronics. IEEE Trans. Electron Devices 58, 141–150 (2011).

Spijkman, M. et al. Increasing the Noise Margin in Organic Circuits Using Dual Gate Field-Effect Transistors. Appl. Phys. Lett. 92, 143304 (2008).

Smith, J. et al. Solution-Processed Small Molecule-Polymer Blend Organic Thin-Film Transistors with Hole Mobility Greater than 5 cm2/Vs. Adv. Mater. 24, 2441–2446 (2012).

Mei, Y. et al. High Mobility Field-Effect Transistors with Versatile Processing from a Small-Molecule Organic Semiconductor. Adv. Mater. 25, 4352–4357 (2013).

Anthony, J. E., Facchetti, A., Heeney, M., Marder, S. R. & Zhan, X. N-Type Organic Semiconductors in Organic Electronics. Adv. Mater. 22, 3876–3892 (2010).

Caironi, M. et al. Very Low Degree of Energetic Disorder as the Origin of High Mobility in an n-channel Polymer Semiconductor. Adv. Funct. Mater. 21, 3371–3381 (2011).

Rivnay, J. et al. Large Modulation of Carrier Transport by Grain-Boundary Molecular Packing and Microstructure in Organic Thin Films. Nat. Mater. 8, 952–958 (2009).

Acknowledgements

This work was partially funded by the FlexTech Consortium.

Author information

Authors and Affiliations

Contributions

T.N.N., D.E.S., J.V., P.B. and C.K. contributed to the overall system design. D.E.S. designed the OTFT circuits. T.N.N., P.M., B.K. and S.K. carried out circuit fabrication and system integration process at PARC. P.B., T.E., Y.W. and O.H. are responsible for memory fabrication and memory readout electronics at Thin Film Electronics. T.N.N., D.E.S., P.M. and P.B. carried out system testing and T.N.N., D.E.S., P.M., J.V., P.B. and C.K. did data analysis. T.N.N. and D.E.S. wrote the paper, with editing contributions from all the co-authors.

Ethics declarations

Competing interests

The authors declare no competing financial interests.

Electronic supplementary material

Rights and permissions

This work is licensed under a Creative Commons Attribution 4.0 International License. The images or other third party material in this article are included in the article’s Creative Commons license, unless indicated otherwise in the credit line; if the material is not included under the Creative Commons license, users will need to obtain permission from the license holder to reproduce the material. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/

About this article

Cite this article

Nga Ng, T., Schwartz, D., Mei, P. et al. Printed dose-recording tag based on organic complementary circuits and ferroelectric nonvolatile memories. Sci Rep 5, 13457 (2015). https://doi.org/10.1038/srep13457

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/srep13457

This article is cited by

-

Three-dimensional monolithic integration in flexible printed organic transistors

Nature Communications (2019)

Comments

By submitting a comment you agree to abide by our Terms and Community Guidelines. If you find something abusive or that does not comply with our terms or guidelines please flag it as inappropriate.