Abstract

The quest for solid state non-volatility memory devices on silicon with high storage density, high speed, low power consumption has attracted intense research on new materials and novel device architectures. Although flash memory dominates in the non-volatile memory market currently, it has drawbacks, such as low operation speed and limited cycle endurance, which prevents it from becoming the “universal memory”. In this report, we demonstrate ferroelectric tunnel junctions (Pt/BaTiO3/La0.67Sr0.33MnO3) epitaxially grown on silicon substrates. X-ray diffraction spectra and high resolution transmission electron microscope images prove the high epitaxial quality of the single crystal perovskite films grown on silicon. Furthermore, the write speed, data retention and fatigue properties of the device compare favorably with flash memories. The results prove that the silicon-based ferroelectric tunnel junction is a very promising candidate for application in future non-volatile memories.

Similar content being viewed by others

Introduction

Over the past two decades, information technologies (ITs) have evolved from the PC era, to mobile era and now to the consumer-mobile era. Different eras have emphasized different requirements for memories, which stimulated research along the directions of non-volatile, high density, high speed and low power consumption. Especially, energy efficient non-volatile memory based on voltage (electric field) induced/assisted writing has recently received intensive attention1,2. Ferroelectric random-access memories (FeRAM) have characteristics such as non-volatility, high speed and low writing energy since the spontaneous polarization is switched by an external electric field3,4. However, the capacitive readout of the information is destructive and a re-write process is required after the readout. Recent experimental and theoretical studies of ferroelectric oxide thin films showed that ferroelectricity can persist down to a few unit cells5,6, which opened a new paradigm for non-destructive FeRAM which utilizes an ultrathin ferroelectric layer as the tunnel barrier in metal/ferroelectric/metal junctions. The asymmetry of screening length of two electrodes leads to the change of the electric resistance when the ferroelectric polarization is switched. This device concept is called ferroelectric tunnel junction (FTJ) and the phenomenon that the electric resistance is modulated by the ferroelectric polarization switching is called tunnelling electroresistance (TER) effect7,8,9. Very large TER effects have been reported in FTJs with BaTiO3 (BTO)10,11,12,13,14,15,16 and Pb1-xZrxTiO317,18,19 ferroelectric tunnel barrier. Writing time as fast as 10 ns and writing energy smaller than 10 fJ/bit were achieved in FTJs14. However, those FTJ devices were demonstrated on perovskite heterostructures with cubic SrTiO3 (STO) (001)11,15,17,18,19 or orthorhombic NdGaO3 (110)10,12,13,14 single crystal substrates, which provide the compressive strain to BTO/PZT layer to maintain the ferroelectricity of the ultra-thin ferroelectric tunnel barrier. The usage of perovskite single crystal substrates is incompatible with the current memory fabrication process which is based on silicon substrates. The capability of fabricating FTJs on silicon substrates therefore becomes essential for the practical application of FTJs as memories. Recently, the non-volatile memory function of FTJs on silicon substrate was demonstrated by using conductive atomic force microscopy (c-AFM)20. However, a real FTJ device demonstration as well as the performances of FTJ devices on silicon substrate such as the writing speed, endurance and fatigue are still lacking and warrant investigation.

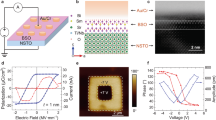

Motivated by practical application, in this work, we demonstrate epitaxial FTJ devices on Si substrates with BTO tunnel barrier with thickness varying from 1.5 to 4 nm. The dependence of TER on BTO thickness, the writing time, the endurance and fatigue of the FTJs device were investigated. The structure of the device is Pt/BTO/La0.67Sr0.33MnO3 (LSMO)/STO/Si, as shown in Fig. 1 (a). An epitaxial layer of STO was deposited on Si (001) substrate as a template (see Methods for details). We use LSMO as the bottom electrode. After the deposition of LSMO, an ultrathin layer of BTO was grown as the ferroelectric tunnelling barrier layer. Following the BTO deposition, an array of 5 μm × 5 μm Pt electrodes (25 nm thick) was patterned on top for subsequent electrical characterizations.

(a) Schematic drawing of the tunnel junction structure. (b) Topography of the BTO thin film. (c) Out-of-plane PFM phase image of BTO thin film. A 2-μm × 2-μm square region with opposite polarization direction was written by scanning the area with a DC bias (−4 V) applied to the AFM tip. (d) Local PFM hysteresis loops of BTO thin film.

Results

Microstructure Analysis of the Tunnel Junctions

Piezoelectric force microscopy (PFM) was performed to characterize the ferroelectric domain structure of BTO films in a separate FTJ device without Pt electrode. Figure 1 (b) show the topography and out-of-plane (OOP) PFM phase images of BTO film with the thickness of 2 nm grown on LSMO/STO/Si heterostructure. The OOP PFM phase image showed uniform contrast; while there was no signal in in-plane PFM images (thus were not shown here). In our PFM system, the yellow contrast in OOP image means the polarization points up (upward), while the purple contrast means the polarization points down (downward). So the PFM result indicates a single downward domain structure in BTO films. To switch the downward polarization, a negative DC bias of −4 V was applied to a selected area through the tip. After the switching, the downward domain changed into upward domain, which reveals a 180° switching path as shown in Fig. 1 (c). Figure 1 (d) shows the PFM hysteresis loops of the 2 nm thick BTO film, indicating its ferroelectric nature. According to the basic quantum mechanism, the tunneling transmittance depends exponentially on the barrier width as well as the barrier height. It has already been reported that a giant TER was achieved by modulating the barrier width using n-type doped Nb:SrTiO3 as bottom electrode through ferroelectric field effect16. In this work, hole doped LSMO is used as the bottom electrode. Therefore, in our case, ON state of the tunnel junction is achieved by a narrower barrier width when the polarization of BTO points up (hole accumulation state at LSMO interface), while OFF state is realized by a wider barrier width when the polarization points downward (hole depletion state at LSMO interface).

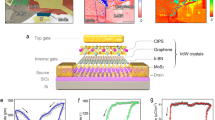

The high-resolution X-ray diffraction (XRD) spectra of the heterostructures (STO/Si and LSMO/STO/Si) are shown in Fig. 2 (a). The calculated average c lattice constant of STO is about 0.4 nm. The elongated c lattice is due to the large compressive strain of about 1.7% between STO and Si with the STO unit cell rotated by 45° relative to the Si conventional unit cell. The full width at half maximum (FWHM) of the rocking curve of STO/Si XRD (002) peak (Supplementary figure S1) is about 0.37°. These XRD spectra suggest a good epitaxial growth of the perovskite film on Si. Figure 2 (b–d) shows the schematic drawing of the cross-sectional structure and the cross-sectional high resolution transmission electron microscope (HRTEM) images of the tunneling device. The thickness of BTO tunnel barrier, LSMO bottom electrode and STO template layer is about 2, 12.3 and 28 nm, respectively. Between the crystalline Si substrate and the crystalline STO layer, there is an amorphous layer of SiOx with the thickness around 8–9 nm. This amorphous layer forms during the oxide films deposition process21,22. To be specific, there are two processes during the growth that may lead to the formation of the amorphous layer. Firstly, during the growth of STO template layer, the oxygen might diffuse into the STO/Si interface and oxidize the Si substrate as the STO layer grew thicker, although the STO layer preserves the original epitaxial registry during the subsequent growth. Secondly, the following LSMO and BTO layers were deposited at 650 °C with an oxygen pressure of 300 mTorr and 5 mTorr, respectively. Under these growth conditions, the oxygen could diffuse through the STO layer and further oxidize the Si substrate. The interfaces between amorphous SrOx layers and crystalline Si and STO layers are shown in Fig. 2 (c). The transitions between crystalline and amorphous phases can be clearly observed. Figure 2 (d) shows the interfaces of LSMO/STO and BTO/LSMO heterostructures. These interfaces are almost atomically sharp, which proves the high epitaxial quality of the perovskite films. The Fast Fourier Transformation (FFT) patterns of BTO, LSMO, STO and Si TEM images are shown in Supplementary figure S2. The calculated average lattice parameter ratio c/a of STO layer is about 1.02. The elongated c lattice is due to the compressive strain between the film and Si substrate, which is consistent with the XRD result. The in-plane lattice constant a of LSMO is around 0.383 nm, which will cause a compressive strain to BTO (the in-plane lattice constant of bulk BTO is 0.399 nm) layer due to the lattice mismatch. The calculated tetragonality (c/a ratio) of BTO is about 1.07, which is much larger than the bulk value of 1.01. The increased tetragonality can greatly enhance the polarization of BTO thin film and favors the maintenance of ferroelectricity for an ultra-thin BTO layer23.

(a) XRD patterns of STO/Si and LSMO/STO/Si structures. (b) HRTEM image of the whole structure of the device. The thin write layer between Pt and LSMO is BTO thin film and a layer of amorphous SiOx is between Si and crystalline STO. (c) HRTEM image of STO/SiOx/Si. The interfaces between the amorphous SiOx layer and crystalline Si and STO layers are clearly shown. (d) HRTEM image of Pt/BTO/LSMO/STO. The dashed lines show the interface of PT/BTO, BTO/LSMO and LSMO/STO, respectively.

Basic Properties of the Tunnel Junctions

The current-voltage (I–V) curves for both upward and downward polarization states of the tunneling device with 2 nm BTO are shown in Fig. 3 (a). The applied voltage is termed as positive (negative) if a positive (negative) bias is applied to the top Pt electrode. After poling the polarization up (down) by applying a voltage pulse of −3 V (+3 V), the tunneling currents are measured at room temperature within low dc range, from −0.3 V to 0.3 V, which is certainly lower than the coercive voltage (VC). For both on and off states, the I–V curves are nonlinear, which is an indication of elastic electron tunneling. With a reading voltage of 0.3 V, the currents for the ON and OFF states of this device with 2 nm BTO layer reach 1.28E-6 A and 8.03E-9 A, respectively, giving a TER ratio of 15800%. To reveal the influence of the ferroelectric thin film thickness on the tunneling effect, the dependence of the TER ratio on the BTO film thickness was studied and the results are shown in Fig. 3 (b). The largest TER ratio was achieved when the BTO thickness is 2 nm. In this work, five devices were measured, the average TER ratio being around 12000%. When the BTO thickness decreases to 1.5 nm, the TER ratio drops rapidly and almost disappears. This may be due to the fact that the ferroelectricity of BTO film becomes very weak or even disappears when its thickness approaches 1.5 nm. This result is consistent with the report that the critical thickness for ferroelectricity of BTO film on STO substrate is around 1.6 nm24. However, we believe this may also be due to the increased leakage probability for thinner BTO layers where by reducing the device size significant TER was seen even with BTO layer thicknesses of 0.8 nm (2 unit cells)25. When the thickness of BTO goes up to 3 and 4 nm, the TER ratio also decreases drastically. This may be because with the increased barrier width, the tunneling effect would no long dominate and other mechanisms start to play a role. In the following discussions, we focus on the FTJ device with BTO thickness of 2 nm.

(a) I–V curves of the tunnel junction (2 nm BTO) with different BTO polarizations. The inset shows the I-V curve of the OFF state (P down). (b) R-V switching curve of the junction (2 nm BTO). (c) TER ratios of the tunnel junctions as the function of BTO thickness. (d) Electrical resistance as functions of switching time for both upward and downward polarization states of the junctions (switching pulse ±3 V). The two points on the y-axis which correspond to 100 of x-axis represent the original OFF and ON states, respectively.

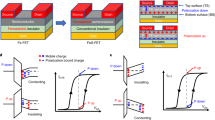

The non-volatile electrical resistance switching (R-V loop) of Pt/BTO/LSMO/STO/Si device with BTO thickness of 2 nm is illustrated in Fig. 3 (c). Similar to the PFM hysteresis loop of ferroelectric in Fig. 1 (d), a clear hysteretic variation of the tunneling resistance is observed. This proves that it is the polarization that causes the change of the resistance. The coercive voltage is below 2 V. It is shown that with the positive and negative voltage pulse switching the device shows the high and low resistance states, respectively. A positive pulse above coercive voltage switches the polarization of BTO to downward direction towards the bottom electrode and vice versa. The high (low) resistance at the positive (negative) voltage can be explained by the change of tunnel barrier width through the depletion (accumulation) of the hole concentration in LSMO bottom electrodes.

Writing Speed, Data Retention and Fatigue Performance of the Tunnel Junctions

To evaluate the writing speed of the ferroelectric tunnel junction on silicon substrate, the dependence of the switching pulse width on the electrical resistance of the FTJ device were measured and the results are shown in Fig. 3(d). Square pulses with the width from 10 ns (the limit of our pulse generator) to 1 μs are used to control the polarization direction of the BTO tunnel barrier and the I–V curves were measured subsequently to detect the electrical resistance of the device (Supplementary figure S3). After applying ±3 V pulses, the spontaneous polarization starts to switch at 10 ns. At 50 ns, the polarization is fully reversed and the ON and OFF electrical resistances saturate at the expected values. The results demonstrate that the ferroelectric tunnel junctions can be written within 50 ns. However, this is by no means the limit. Shorter writing time is expected if higher pulse voltage is used26. In fact, it has already been reported that polarization switching of ferroelectric Pb(Nb0.04Zr0.28Ti0.68)O3 thin film can be realized with a voltage pulse less than 1 ns generated by a semiconductor photoconductive switch27. To read the ON and OFF states of the tunnel junctions, we can detect the electrical resistance by simply measuring the I–V curves. Therefore the reading process is non-destructive since it does not require the switching of the ferroelectric polarization.

Long data retention and superior fatigue performance are two critical requirements for the application of non-volatile memory devices. We have monitored the resistance of several tunnel junctions for one week and no deterioration in the signal has been observed (Fig. 4 (a)). The junctions were under open boundary condition during the periods between the read-out measurements. By extrapolation, we can estimate that the TER ratio of the junctions could be maintained over 10000% for more than 10 years. Furthermore, the tunnel junctions have been subjected to bipolar switching for up to 105 cycles, as shown in Fig. 4 (b). The fatigue properties were measured by applying bipolar electrical pulses of ±3 V (pulse width of 0.05 ms) with different durations to the devices. After each cycling, the devices were set to ON and OFF states again and I–V curves were measured accordingly to test the corresponding resistance state (Supplementary figure S4). As shown in Fig. 4 (b), after 105 cycles, the tunnel junctions can still be switched to the original ON and OFF states, with only a slightly decreased TER ratio. This proves that the polarization of BTO thin film is still switchable after 105 cycles. With further electrical cycling, the tunnel junctions could not function any more, which might be due to domain wall pinning of the BTO thin film. It is well known that oxide electrodes can mitigate the fatigue problem in ferroelectric oxide, because they can reduce the oxygen vacancy concentration at the film/electrode interface, leading to less domain pinning28. This suggests that fatigue properties of tunnel junctions might be improved further by fine tuning the interfaces between the electrodes and tunnel barrier. The endurance of current FTJ device in this work is larger than that of the NAND flash memory (around 104 cycles).

Discussion

In summary, we report here a functional non-volatile FTJ grown directly on Si substrate, with a TER ratio over 10000%. The fast writing speed (within 50 ns by ±3 voltage pulses), long data retention and good fatigue performance of the tunneling devices compare favorably with flash memories which dominate in the current non-volatile memory market. All our results show that ferroelectric tunnel junction is a very promising candidate for future silicon-based non-volatile resistive memories with high speed and low power consumption.

Methods

Device preparation

STO template layer was fabricated using a two-step growth method by molecular beam epitaxy (MBE) technique. Before the growth, SiO2 layer on top of the Si substrate was deoxidized. This was achieved by using a Sr-assisted deoxidization process29. After heating the Si substrate to 600 °C, 2 monolayers of metal Sr was deposited. Afterwards, Si was heated up to 800 °C with ~10 min wait until a clear RHEED pattern of crystalline Si (100) surface was seen. After cooling the Si substrate to 600 °C, more Sr was deposited until a clear 2x reconstruction pattern was observed from RHEED. Following the deoxidization process, 2.5 u.c. of STO was grown at 350 °C with the oxygen partial pressure in the mid to upper 10E-8 Torr range. The as-grown 2.5 u.c. of STO was annealed at 600 °C in vacuum for ~10 min for recrystallization. This process was repeated three times until we got a 7.5 u.c. STO film on Si (1st step)30. With the 7.5 u.c. of epitaxially grown STO, another 25 nm STO was grown at ~550 °C using the same oxygen partial pressure without annealing (2nd step).

The following LSMO and BTO layer were deposited by pulsed laser deposition (PLD) technique. LSMO was deposited at a substrate temperature of 600 °C with an oxygen partial pressure of 300 mTorr and BTO films were deposited subsequently at 650 °C with an oxygen partial pressure of 5 mTorr. The laser energy density was fixed at 1 J/cm2 for all depositions with a frequency of 3 Hz. After the deposition, the films were cooled down to room temperature at an oxygen pressure of 100 Torr. The cooling rate was 5 °C/min till 300 °C and then 15 °C/min to room temperature.

After the deposition of BTO, 5 μm × 5 μm top electrodes were prepared by photolithography. After the photolithography, Pt electrodes were deposited by PLD at room temperature. The remaining photoresist was stripped by a remover solution (MicroChem).

Electrical characterizations

Piezoelectric force microscopy (PFM) measurement was carried out on a commercial atomic force microscope (Asylum Research MFP-3D) using Pt/Ti-coated tip. The measurement was performed under contact mode with an AC voltage applied to the probe tip. The scan rate was kept at 0.5 μm/s. I–V curves were measured using a metre/direct current (DC) voltage source (Keithley 2635B) on a low noise probe station. Fatigue properties and switching experiments were carried out using a commercial ferroelectric tester (Radiant Technologies, Inc.) and a pulse generator (Genetron PSPL Model 10, 700 A pulse generator).

Additional Information

How to cite this article: Guo, R. et al. Functional ferroelectric tunnel junctions on silicon. Sci. Rep. 5, 12576; doi: 10.1038/srep12576 (2015).

References

Wang, W. G. et al. Electric-field-assisted switching in magnetic tunnel junctions. Nat. Mater. 11, 64–68 (2012).

Vaz, C. A. F. Electric field control of magnetism in multiferroic heterostructures. J. Phys. Condens. Mater. 24, 333201 (2012).

Scott, J. F. Application of modern ferroelectrics. Science 315, 954–959 (2007).

Kato, Y. et al. Overview and future challenge of ferroelectric random access memory technologies. Jpn. J. Appl. Phys. 46, 2157 (2007).

Streiffer, S. K. et al. Observation of nanoscale 180° stripe domains in ferroelectric PbTiO3 thin films. Phys. Rev. Lett. 89, 067601 (2002).

Fong, D. D. et al. Ferroelectricity in ultrathin perovskite films. Science 304, 1650–1653 (2004).

Ye, M. et al. Giant electroresistance in ferroelectric tunnel junctions. Phys. Rev. Lett. 102, 169901 (2009).

Tsymbal, E. Y. et al. Tunneling across a ferroelectric. Science 313, 181–183 (2006).

Garcia, V. et al. Giant tunnel electroresistance for non-destructive readout of ferroelectric states. Nature 460, 81–84 (2009).

Garcia. V. et al. Ferroelectric tunnel junctions for information storage and processing. Nat. Commun. 5, 4289 (2014).

Gruverman, A. et al. Tunneling electroresistance effect in ferroelectric tunnel junctions at the nanoscale. Nano Lett. 9(10), 3539–3543 (2009).

Chanthbouala, A. et al. A ferroelectric memristor. Nat. Mater. 11, 860–864 (2012).

Kim, D. J. et al. Ferroelectric tunnel memristor. Nano Lett. 12(11), 5697–5702 (2012).

Chanthbouala, A. et al. Solid-state memories based on ferroelectric tunnel junctions. Nat. Nano. 7, 101–104 (2012).

Yin, Y. W. et al. Enhanced tunnelling electroresistance effect due to a ferroelectrically induced phase transition at a magnetic complex oxide interface. Nat. Mater. 12, 397–402 (2013).

Wen, Z. et al. Ferroelectric-field-effect-enhanced electroresistance in metal-ferroelectric-semiconductor tunnel junction. Nat. Mater. 12, 617–621 (2013).

Maksymovych, P. et al. Polarization control of electron tunneling into ferroelectric surfaces. Science 324, 1421–1425 (2009).

Pantel. D. et al. Tunnel electroresistance in junctions with ultrathin ferroelectric Pb(Zr0.2Ti0.8)O3 barriers. Appl. Phys. Lett. 100, 232902 (2012).

Jiang, L. et al. Tunneling electroresistance induced by interfacial phase transitions in ultrathin oxide heterostructures. Nano Lett. 13(12), 5837–5843 (2013).

Li, Z. et al. An epitaxial ferroelectric tunnel function on silicon. Adv. Mater. 26(42), 7185–7189 (2014).

Gu, X. et al. Commercial molecular beam epitaxy production of high quality SrTiO3 on large diameter Si substrates. J. Vac. Sci. Tech. B 27 (3) 1195 (2009).

Abel, S. et al. A strong electro-optically active lead-free ferroelectric integrated on silicon. Nat. Commun. 4, 1671 (2013).

Choi, K. J. et al. Enhancement of ferroelectricity in strained BaTiO3 thin films. Science 306, 1005–1009 (2004).

Tenne, D. A. et al. Ferroelectricity in ultrathin BaTiO3 Films: Probing the size effect by ultraviolet raman spectroscopy. Phys. Rev. Lett. 103, 177601 (2009).

Li, C. et al. Ultrathin BaTiO3-based ferroelectric tunnel junctions through interface engineering. Nano. Lett. 15 (4), 2568 (2015).

Guo, R. et al. Non-volatile memory based on ferroelectric photovoltaic effect. Nat. Commun. 4, 1990 (2013).

Li, J. et al. Ultrafast polarization switching in thin-film ferroelectrics. Appl. Phys. Lett. 84, 1174–1176 (2004).

Ramesh, R. et al. Fatigue and retention in ferroelectric Y-Ba-Cu-O/Pb-Zr-Ti-O/Y-Ba-Cu-O heterostructures. Appl. Phys. Lett. 61, 1537–1539 (1992).

Wei, Y. et al. Mechanism of cleaning Si(100) surface using Sr or SrO for the growth of crystalline SrTiO3 films. J. Vac. Sci. Technol. B 20, 1402–1405 (2002).

Li, H. et al. Two-dimensional growth of high-quality strontium titanate thin films on Si. J. Appl. Phys. 93, 4521–4525 (2003).

Acknowledgements

The research is supported by the Singapore National Research Foundation under CRP Award No. NRF-CRP10-2012-02.

Author information

Authors and Affiliations

Contributions

R.G. and J.C. conceived the experiments. R.G., Z.W., S.Z., K.H. and L.H. conducted the experiments. R.G., J.C., A.A, T.V. and D.S. discussed about the results. R.G. and J.C. wrote the manuscript. J.C. supervised the project. All authors reviewed the manuscript.

Ethics declarations

Competing interests

The authors declare no competing financial interests.

Electronic supplementary material

Rights and permissions

This work is licensed under a Creative Commons Attribution 4.0 International License. The images or other third party material in this article are included in the article’s Creative Commons license, unless indicated otherwise in the credit line; if the material is not included under the Creative Commons license, users will need to obtain permission from the license holder to reproduce the material. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/

About this article

Cite this article

Guo, R., Wang, Z., Zeng, S. et al. Functional ferroelectric tunnel junctions on silicon. Sci Rep 5, 12576 (2015). https://doi.org/10.1038/srep12576

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/srep12576

This article is cited by

-

HfAlO-based ferroelectric memristors for artificial synaptic plasticity

Frontiers of Physics (2023)

-

Integration of c-axis oriented Bi3.15Nd0.85Ti2.95Hf0.05O12/La0.67Sr0.33MnO3 ferromagnetic-ferroelectric composite film on Si substrate

Scientific Reports (2017)

-

Investigation of multilevel data storage in silicon-based polycrystalline ferroelectric tunnel junction

Scientific Reports (2017)

-

Monolithic integration of room-temperature multifunctional BaTiO3-CoFe2O4 epitaxial heterostructures on Si(001)

Scientific Reports (2016)

-

First-principles study of interface doping in ferroelectric junctions

Scientific Reports (2016)

Comments

By submitting a comment you agree to abide by our Terms and Community Guidelines. If you find something abusive or that does not comply with our terms or guidelines please flag it as inappropriate.