Abstract

Single-walled carbon nanotube (SWNT) is expected to be a very promising material for flexible and transparent driver circuits for active matrix organic light emitting diode (AM OLED) displays due to its high field-effect mobility, excellent current carrying capacity, optical transparency and mechanical flexibility. Although there have been several publications about SWNT driver circuits, none of them have shown static and dynamic images with the AM OLED displays. Here we report on the first successful chemical vapor deposition (CVD)-grown SWNT network thin film transistor (TFT) driver circuits for static and dynamic AM OLED displays with 6 × 6 pixels. The high device mobility of ~45 cm2V−1s−1 and the high channel current on/off ratio of ~105 of the SWNT-TFTs fully guarantee the control capability to the OLED pixels. Our results suggest that SWNT-TFTs are promising backplane building blocks for future OLED displays.

Similar content being viewed by others

Introduction

With increasing demands for a variety of robust, light-weighted and wearable electronic devices, the flexibility and transparency of the devices are required for next generation electronics such as flexible displays, sensors and photovoltaic systems, etc1,2,3. Recently, organic light-emitting diode (OLED) flexible displays have attracted a lot of attention. OLED displays possess many advantages over traditional liquid crystal displays (LCD), such as self-emission, high light efficiency, high brightness and contrast, wide viewing angle, low power consumption and excellent flexibility, etc4,5. They have been used in curved televisions, cell phones, digital cameras and other mobile devices. These displays are driven by thin-film transistors (TFTs) whose channel materials are typically amorphous silicon, polycrystalline silicon, organic and metal oxide semiconductors, nanowires, etc. Amorphous silicon TFTs suffer from a low mobility ( <1 cm2V−1s−1) and relatively low driving capacity6,7. As a replacement, polycrystalline silicon TFTs can provide a bit higher mobility and driving capacity8, but their relatively high cost, high-temperature processing and optical opacity are not compatible with the requirements of future display electronics. In comparison, organic and metal oxide semiconductor TFTs have high optical transparency and can be processed at low-temperatures. But, similar to amorphous silicon TFTs, they have a relatively low device mobility9,10,11,12,13. Although OLED displays driven by In2O3 nanowire-based transistors have been reported14,15, relatively poor device uniformity, low reliability and processing challenges still need to be overcome for good performances.

<1 cm2V−1s−1) and relatively low driving capacity6,7. As a replacement, polycrystalline silicon TFTs can provide a bit higher mobility and driving capacity8, but their relatively high cost, high-temperature processing and optical opacity are not compatible with the requirements of future display electronics. In comparison, organic and metal oxide semiconductor TFTs have high optical transparency and can be processed at low-temperatures. But, similar to amorphous silicon TFTs, they have a relatively low device mobility9,10,11,12,13. Although OLED displays driven by In2O3 nanowire-based transistors have been reported14,15, relatively poor device uniformity, low reliability and processing challenges still need to be overcome for good performances.

A single-walled carbon nanotube (SWNT) network inherits the unique properties of SWNTs16,17,18 and causes a high device uniformity due to the statistical averaging of multipath transports in the network. In addition, easy accessible fabrication process of SWNT network makes it more suitable to be integrated with scalable OLED pixels on a large-area substrate. Recently, SWNT-TFT based flexible devices19,20, integrated logic circuits19,21,22,23,24 and even a prototype of carbon nanotube-based computer25 have shown the outstanding electrical properties and excellent performance. SWNT-TFTs driver circuits for OLED displays have also been demonstrated on both flexible and hard substrates1,26,27,28,29,30. Due to the developments of high-performance TFTs using sorted semiconducting (sc)-SWNTs27,31,32,33, the most reported SWNT-TFTs driver circuits were made from sorted high-purity sc-SWNTs to achieve high on/off ratios1,27,28,29,30. Zhang et al. (Ref. 30) firstly demonstrated sorted sc-SWNTs driver circuits for an active matrix (AM) OLED display (20 × 25 pixels). As they employed the bottom gate structure and coated solution-based highly pure SWNTs onto the gate dielectric layer, they did encounter several technical challenges, say coating SWNTs uniformly in the channel regions and reducing the dielectric layer roughness, etc. In fact, they did not demonstrate the static and dynamic images of the display and ~30% of the pixels were not turned on. In addition, adoption of solution-based sorted sc-SWNTs is usually concomitant with several other problems, like contaminants of the surfactants and shortening of the nanotubes in the sorting and/or coating processes22,34. The local bottom-gate structure is usually employed in TFTs fabrication with solution-based separated SWNTs27,29. However, in the local bottom-gate configuration, the SWNTs channel is exposed to its environment. The conduction characteristics of the SWNT-TFTs are usually changed after passivation process. All these problems/challenges should be ticketed in order to develop high performance SWNT driver circuits for real static and dynamic AM OLED displays. However, to our knowledge, such SWNT driver circuits have not been reported yet.

In this paper, we demonstrate, for the first time, chemical vapor deposition (CVD)-grown random SWNT network based driver circuits for static and dynamic AM OLED (6 × 6 pixels) displays. The random SWNT network used here has very low contamination and very few short defective SWNTs (see Supplementary Fig. S1 online). With a top-gate structure, our SWNT-TFTs show an excellent uniform performance with the device mobility of ~45 cm2V−1s−1 and channel current on/off ratio of ~105. These key parameters ensure a good control capability of the driver circuit to the large-scale OLED display.

Here, each AM OLED display pixel is integrated with two SWNT-TFTs and one capacitor (2T1C), as shown in Fig. 1a. The blue dashed box highlights a single unit 2T1C circuit which consists of one switching transistor (ST), one driving transistor (DT), one charge storage capacitor (CS) and one OLED pixel35. When the scan line (VSCAN) is selected, the ST is switched on so that the image information from the data line (VDATA) is written to the gate of the DT. Meanwhile, the image information, i. e. the voltage from the data line, is also stored and stabilized on CS in one frame time, which is essential for the dynamic row-by-row scanning mode of present display technology. The DT is needed to drive each OLED pixel with the current from VDD. Figure 1b shows the optical image of the 2T1C structure. The total area of the single unit is 820 × 820 μm2, within which the OLED pixel occupies an area of 480 × 480 μm2, with an aperture ratio (defined as the ratio of the OLED pixel area to the single unit area) of 34 . In principle, the aperture ratio could be further increased by optimizing layout designs and processing flows. Figure 1c shows a schematic cross-sectional perspective view of the single unit device structure fabricated on a quartz substrate with CVD-grown SWNT network channel, patterned Ti/Au (5 nm/30 nm) source and drain electrodes, Si3N4 (100 nm) gate dielectric, Ti/Au (10 nm/100 nm) top-gate electrodes, integrated green OLED and a 300 nm SiO2 passivation layer.

. In principle, the aperture ratio could be further increased by optimizing layout designs and processing flows. Figure 1c shows a schematic cross-sectional perspective view of the single unit device structure fabricated on a quartz substrate with CVD-grown SWNT network channel, patterned Ti/Au (5 nm/30 nm) source and drain electrodes, Si3N4 (100 nm) gate dielectric, Ti/Au (10 nm/100 nm) top-gate electrodes, integrated green OLED and a 300 nm SiO2 passivation layer.

Structure of the AM OLED driver circuit design and layout.

(a) Schematic diagram of AM OLED display design based on a 2T1C single unit circuit, consisting of one ST, one DT, one CS and one OLED pixel. (b) Optical image of a single AM OLED display unit. The total area of the single unit is 820 × 820 μm2 including an OLED pixel area of 480 × 480 μm2. (c) A schematic cross-sectional perspective view of the single AM OLED display unit fabricated on a quartz substrate with CVD-grown SWNT network as the active channel, patterned Ti/Au source and drain electrodes, Si3N4 gate dielectric, Ti/Au top-gate electrode, integrated green OLED and a SiO2 passivation layer.

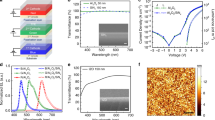

To begin with, a uniform random SWNT network is grown on a quartz substrate on which ferritin has been deposited as catalyst21,24. Carbon feed stock into the thermal CVD is provided by flowing a mixture of H2 and Ar through an ethanol bubbler. The density of the SWNTs can be controlled through the density of ferritin and the flow rates of H2 and Ar gases. A field-emission scanning electron microscope (FE-SEM) image (Fig. 2a) of a randomly grown SWNT network suggests that, the average length of the as-grown SWNTs is more than 10 μm, far larger than the length ( 2 μm) of solution-based pre-separated SWNTs27,28. Probably because of the long SWNTs and small number of SWNT-SWNT contact junctions, the device mobility is larger than those reported TFTs made with solution-based separated SWNTs in Refs. 27 and 28. To reduce metallic SWNTs percolating pathways between the source and drain, the conventional striping technique21,26,36 is applied to pattern the random SWNT network into parallel strips with a width of 5 μm and a spacing of 4 μm, as shown in Fig. 2b. After the striping process, the SWNT-TFTs’ current on/off ratio is typically 105.

2 μm) of solution-based pre-separated SWNTs27,28. Probably because of the long SWNTs and small number of SWNT-SWNT contact junctions, the device mobility is larger than those reported TFTs made with solution-based separated SWNTs in Refs. 27 and 28. To reduce metallic SWNTs percolating pathways between the source and drain, the conventional striping technique21,26,36 is applied to pattern the random SWNT network into parallel strips with a width of 5 μm and a spacing of 4 μm, as shown in Fig. 2b. After the striping process, the SWNT-TFTs’ current on/off ratio is typically 105.

Figure 3a shows the top-gate configuration of the SWNT-TFTs. On the quartz substrate with CVD-grown random SWNT network, 5 nm Ti/30 nm Au are deposited using an electron-beam (e-beam) evaporator as the source and drain electrodes. After the striping process, 100 nm Si3N4 gate dielectric is deposited by plasma enhanced chemical vapor deposition (PECVD), followed by patterning of the top-gate electrode (10 nm Ti/100 nm Au). The SWNTs outside the channel region are removed by oxygen plasma etching. Figure 3b shows the transfer (ID-VG) characteristics (the red curve is plotted in the log scale and the blue curve is in the linear scale) and transconductance (gm-VG) characteristics (the black curve) of a typical ST with a channel length of L = 80 μm and a channel width of W = 200 μm. The device shows a typical n-type behavior and the on-current of 11.7 μA at VD = 1 V and VG = 10 V. An on/off ratio greater than 105 and the peak transconductance of 2.9 μS are obtained. It is known that SWNT-TFTs are typically p-type in ambient air, because of oxygen molecules or moisture adsorbed on the sidewalls of the SWNTs and/or SWNT-metal contacts37,38. However, in our top-gate configuration, n-type characteristics are generally observed mainly due to the desorption of oxygen molecules or moisture during deposition of Si3N4 gate dielectric24. Taking the electrostatic coupling between SWNTs27,39 into consideration, the device mobility can be determined to be ~45 cm2V−1s−1, far superior to that of conventional organic TFTs9 (~4 cm2V−1s−1) and amorphous silicon TFTs6 (<1 cm2V−1s−1). The output characteristics of a typical TFT are plotted in Fig. 3c with VG varying from 10 to −10 V in steps of −5 V. As the transistor is fully turned off when VG ≤ 0 V, the curves for VG = 0, −5 and −10 V are not distinguishable. Figure 3d summarizes the current on/off ratios and on-current values measured from all 36 STs in the driver circuit. The average values of the on-current and the on/off ratio are 11.83 μA and 4.9 orders of magnitude, with the standard deviations of 4.27 μA and 0.1 orders of magnitude, respectively. The small fluctuations suggest a highly uniform device performance among the 36 SWNT-TFTs.

Electrical properties of top-gated SWNT-TFTs used in the AM OLED driver circuit.

(a) Schematic diagram of the top-gated SWNT-TFT fabricated on a quartz substrate with Ti/Au source and drain electrodes, Si3N4 gate dielectric and Ti/Au top gate. (b) Transfer (ID-VG) characteristics (the red curve is plotted in the log scale and the blue curve is in the linear scale) and transconductance (gm-VG) characteristics (the black curve) of a typical ST (channel length L = 80 μm, channel width W = 200 μm) with VD = 1 V. (c) Output (ID-VD) characteristics of the same transistor with VG varying from 10 to −10 V with −5 V steps. (d) The current on/off ratios and on-current values of 36 STs (L = 80 μm, W = 200 μm).

After the driver circuit is fabricated, a 6 × 6 AM OLED pixel array is introduced. A single unit of the 2T1C layout is shown in Fig. 1a and Fig. 1b. Before introduction of the OLED pixels, a layer of 300 nm SiO2 is deposited to passivate and isolate the driver circuit from the OLED pixels, only leaving the pre-patterned ITO (used as the OLED anode) open in order to connect with the green OLED that is fabricated using the thermal evaporation technique. Figure 4a shows the optical image of a 6 × 6 driver circuit array before introduction of the OLED pixels. In order to confirm the control capability of each single unit circuit, the transfer (IDD-VDATA) characteristics are measured and shown in Fig. 4b. The scan line (VSCAN) is biased at 10 V to turn on the ST so that the DT can be controlled by the signal (VDATA) from the data line. An excellent on/off ratio (~105) can be obtained. An on-current of 10 μA can be achieved when VDD = 1 V, VDATA = 10 V and VSCAN = 10 V. This on-current is sufficient to power on an OLED pixel with the size of 480 μm × 480 μm. The current driving capability of the driver circuit is a very important factor for the OLED display.

The SWNT-TFTs driver array with 2T1C configuration in each unit.

(a) Photograph of the 6 × 6 driver array (0.5 × 0.5 cm2) before introduction of OLED pixels. (b) Typical transfer (IDD-VDATA) characteristics of a single unit 2T1C circuit when VSCAN = 10 V, VDD = 1 V. Inset: schematic diagram of the single unit 2T1C circuit.

The performance of the OLED pixel is evaluated after a standard Tris(8-hydroxy-quinolinato) aluminum (Alq3) green OLED with multilayer configuration is fabricated. The OLED is of a layered structure of ITO/MoO3/N,N’-Bis(naphthalen-1-yl)-N,N’-bis(phenyl)-benzidine (NPB)/Alq3/LiF/Al, as illustrated in Fig. 5a. The OLED shows an ideal diode-like characteristic with turn-on voltage of 2.7 V, as shown in Fig. 5b. At the turn-on voltage, the turn-on current for a 480 μm × 480 μm OLED pixel is 0.1 μA (the current density of 4.7 × 10−4 mA/mm2), much smaller than the on-current (~10 μA) of the single unit driver circuit (see Fig. 4b), suggesting that the single unit 2T1C driver circuit can fully drive an OLED pixel.

Finally, the AM OLED display with 6 × 6 pixels driven by 72 SWNT-TFTs is demonstrated. An external microcontroller unit (MCU) is used to generate the controlling signals VSCAN and image signals VDATA. The controlling signals switch on the STs to enable the image signals to transfer to the gates of the DTs and turn on them to pass IDD to further drive the OLED pixels. Figure 6a is a photo showing all 36 pixels are turned on when VSCAN = 10 V, VDATA = 10 V and VDD = 5 V are applied for all scan, data and power lines. It can be seen that all pixels are turned on although some pixels emit relatively weak luminance. The weak luminance pixels are likely caused by the OLED quality degradation arising from surface roughness of the OLED anode (ITO)40. Another possible reason for the luminance difference could be the fluctuations of the on-current in the SWNT-TFTs (see Fig. 3d). To show the performance of this OLED display, program codes based on the row-by-row scanning mode which is widely employed in present display technology are developed and inputted into the external MCU to control the driver array. Figure 6b shows three letters “N”, “T” and “U” on this OLED display in sequence. A video showing three running letters “N”, “T” and “U” is provided in Supplementary online. To the best of our knowledge, this is the first demonstration of static and dynamic images implemented on an AM OLED display driven solely by a SWNT-TFT driver circuit.

Display demonstration of the 6 × 6 AM OLED pixels driven by 72 SWNT-TFTs.

(a) A photo showing the 36 pixels turned on under VSCAN = 10 V, VDATA = 10 V and VDD = 5 V. (b) The letters “N”, “T” and “U” are displayed sequentially on this OLED display. A video showing three running letters “N”, “T” and “U” can be found in Supplementary online.

In summary, we have successfully developed SWNT-TFT driver circuit for a 6 × 6 static and dynamic AM OLED display. CVD-grown random SWNT network is used as the channels of the top-gated TFTs to achieve a highly uniform performance, i. e. the channel current on/off ratio of ~105 and device mobility of ~45 cm2V−1s−1. Our results confirm that the SWNT-TFT driver circuit is capable of controlling the OLED display. This work suggests that SWNT-based driver circuits could be of a great potential for future OLED displays.

Methods

Synthesis of random SWNT networks

The random SWNT networks used here are grown using thermal chemical vapor deposition on quartz substrates. The process flow is as follows: (1) A quartz substrate is cleaned by ultrasonication in acetone and IPA to remove organic contaminants and then dipped into a piranha solution (a 3:1 volumetric mixture of concentrated sulphuric acid to 30 hydrogen peroxide solution) for 30 min to make the quartz surface extremely hydrophilic; (2) The catalyst solution of ferritin (Aldrich; diluted with de-ionized water at a volumetric ratio of 1:80) is spin-coated on the quartz substrate; (3) The quartz substrate is heated to 800 °C in a quartz tube to oxidize ferritin into iron oxide nanoparticles; (4) The quartz tube is then further heated to 925 °C in 100 s.c.c.m. hydrogen gas flow for 10 min to reduce the iron oxide to iron; (5) 30 s.c.c.m. argon gas and 15 s.c.c.m. hydrogen gas flow through an ethanol (carbon source) bubbler into the quartz tube while maintaining temperature (925 °C) for 15 min. The density of the random SWNTs is controllable through control of the concentration of ferritin solution and carrier gases (H2 and Ar) flow rates.

hydrogen peroxide solution) for 30 min to make the quartz surface extremely hydrophilic; (2) The catalyst solution of ferritin (Aldrich; diluted with de-ionized water at a volumetric ratio of 1:80) is spin-coated on the quartz substrate; (3) The quartz substrate is heated to 800 °C in a quartz tube to oxidize ferritin into iron oxide nanoparticles; (4) The quartz tube is then further heated to 925 °C in 100 s.c.c.m. hydrogen gas flow for 10 min to reduce the iron oxide to iron; (5) 30 s.c.c.m. argon gas and 15 s.c.c.m. hydrogen gas flow through an ethanol (carbon source) bubbler into the quartz tube while maintaining temperature (925 °C) for 15 min. The density of the random SWNTs is controllable through control of the concentration of ferritin solution and carrier gases (H2 and Ar) flow rates.

Fabrication of top-gated SWNT-TFT driver circuit

First, on the quartz substrate with randomly as-grown SWNT network, the windows for the source and drain electrodes of the SWNT-TFTs are defined using standard photolithography (AZ 5214 as photoresist) and then 5 nm Ti and 30 nm Au are deposited using an electron-beam evaporation system. After a lift-off process, another photolithography process and oxygen plasma reactive-ion etching (200 mTorr, 20 s.c.c.m. O2 flow, 100 W radio frequency power) are applied to pattern the SWNT network into parallel strips to achieve a high on/off ratio of the SWNT-TFTs. In order to isolate the SWNT-TFTs from each other, oxygen plasma reactive-ion etching with the same conditions is employed again to clean up any SWNTs outside the channel regions which are protected by a patterned photoresist layer. Then, a 100 nm Si3N4 gate dielectric layer is deposited on the whole substrate by plasma enhanced chemical vapor deposition (PECVD). SiH4, NH3 and N2 (at the flow rates of 100, 20, 600 s.c.c.m., respectively) are used as the reaction gases and the radio frequency power is set at a low value of 20 W to minimize damage to the SWNT channels. With a high pressure of 1 Torr and a large N2 flow, the resultant plasma is cold and mild and the low plasma density results in a low deposition rate of 0.4 nm/s. After the gate dielectric deposition, the vias for interlayer interconnects are defined by photolithography and hydrofluoric (HF) acid etching (8 s in a 1:20 volumetric mixture of concentrated HF acid to de-ionized water). After via etching, the interlayer interconnects (10 nm Ti/90 nm Au) are deposited into the vias, followed by a lift-off process. Finally, the gate electrodes (10 nm Ti/100 nm Au) and interconnects (between the STs and the DTs) are patterned.

6 × 6 OLED pixels integrated with the top-gated SWNT-TFT driver circuit

Before OLED fabrication, the top-gated SWNT-TFT driver circuit is passivated with a 300 nm SiO2 layer, leaving only the OLED anode area open in each unit. After passivation, 300 nm indium-tin oxide (ITO) is deposited as OLED anodes using a radio frequency sputtering system. Then, a standard Tris(8-hydroxy-quinolinato) aluminum (Alq3) green OLED with structure of ITO/MoO3 [5 nm]/NPB [80 nm]/Alq3 [60 nm]/LiF [1 nm]/Al [150 nm] is fabricated using a thermal evaporator.

Device and circuit characterizations

The morphology of random SWNT networks is characterized using a field-emission scanning electron microscopy (LEO 1550 Gemini SEM). The direct-current measurements of SWNT-TFTs and single unit driving circuit are carried out in air using a semiconductor parameter analyzer (Agilent, B1500A). The performances of OLED pixels are measured using LS-110 luminance meter (Konica Minolta). An external microcontroller unit (Arduino Duemilanove ATmega328) is used to input controlling and image signals to the SWNT-TFT driver circuit to create static and dynamic images on the OLED display.

Additional Information

How to cite this article: Zou, J. et al. Carbon Nanotube Driver Circuit for 6 × 6 Organic Light Emitting Diode Display. Sci. Rep. 5, 11755; doi: 10.1038/srep11755 (2015).

References

Chen, P. C. et al. Fully printed separated carbon nanotube thin film transistor circuits and its application in organic light emitting diode control. Nano Lett. 11, 5301–5308 (2011).

Schwartz, G. et al. Flexible polymer transistors with high pressure sensitivity for application in electronic skin and health monitoring. Nat. Commun. 4, 1859 (2013).

Kaltenbrunner, M. et al. Ultrathin and lightweight organic solar cells with high flexibility. Nat. Commun. 3, 770 (2012).

Forrest, S. R., Burrows, P. E. & Thompson, M. E. Organic emitters promise a new-generation of displays. Laser Focus World 31, 99–101 (1995).

Sheats, J. R. et al. Organic electroluminescent devices. Science 273, 884–888 (1996).

Powell, M. J. The physics of amorphous-silicon thin-film transistors. IEEE Transactions on Electron Devices 36, 2753–2763 (1989).

Snell, A. J., Spear, W. E., Le Comber, P. G. & Mackenzie, K. Application of amorphous silicon field effect transistors in integrated circuits. Appl. Phys. A 26, 83–86 (1981).

Chang, C.-P. & Wu, Y. S. Improved electrical performance and uniformity of MILC poly-Si TFTs manufactured using drive-in nickel-induced lateral crystallization. IEEE Electron Device Letters 30, 1176–1178 (2009).

Gelinck, G. H. et al. Flexible active-matrix displays and shift registers based on solution-processed organic transistors. Nature Mater. 3, 106–110 (2004).

Sekitani, T., Zschieschang, U., Klauk, H. & Someya, T. Flexible organic transistors and circuits with extreme bending stability. Nature Mater. 9, 1015–1022 (2010).

Chiang, H. Q. et al. Thin-film transistors with amorphous indium gallium oxide channel layers. Journal of Vacuum Science & Technology B 24, 2702–2705 (2006).

Hoffman, R. L., Norris, B. J. & Wager, J. F. ZnO-based transparent thin-film transistors. Appl. Phys. Lett. 82, 733–735 (2003).

Inoue, S.-I., Ueda, K., Hosono, H. & Hamada, N. Electronic structure of the transparent p-type semiconductor (LaO)CuS. Phys. Rev. B 64, 245211 (2001).

Chen, P. C. et al. High-performance single-crystalline arsenic-doped indium oxide nanowires for transparent thin-film transistors and active matrix organic light-emitting diode displays. Acs Nano 3, 3383–3390 (2009).

Ju, S. et al. Transparent active matrix organic light-emitting diode displays driven by nanowire transistor circuitry. Nano Lett. 8, 997–1004 (2008).

Bradley, K., Gabriel, J.-C. P. & Grüner, G. Flexible nanotube electronics. Nano Lett. 3, 1353–1355 (2003).

Snow, E. S., Campbell, P. M., Ancona, M. G. & Novak, J. P. High-mobility carbon-nanotube thin-film transistors on a polymeric substrate. Appl. Phys. Lett. 86, 033105 (2005).

Seidel, R. et al. High-current nanotube transistors. Nano Lett. 4, 831–834 (2004).

Artukovic, E., Kaempgen, M., Hecht, D. S., Roth, S. & GrUner, G. Transparent and flexible carbon nanotube transistors. Nano Lett. 5, 757–760 (2005).

Cao, Q. & Rogers, J. A. Ultrathin films of single-walled carbon nanotubes for electronics and sensors: a review of fundamental and applied aspects. Adv. Mater. 21, 29–53 (2009).

Cao, Q. et al. Medium-scale carbon nanotube thin-film integrated circuits on flexible plastic substrates. Nature 454, 495–500 (2008).

Sun, D. M. et al. Flexible high-performance carbon nanotube integrated circuits. Nature Nanotech. 6, 156–161 (2011).

Yu, W. J. et al. Small hysteresis nanocarbon-based integrated circuits on flexible and transparent plastic substrate. Nano Lett. 11, 1344–1350 (2011).

Gao, P. Q., Zou, J. P., Li, H., Zhang, K. & Zhang, Q. Complementary logic gate arrays based on carbon nanotube network transistors. Small 9, 813–819 (2013).

Shulaker, M. M. et al. Carbon nanotube computer. Nature 501, 526–530 (2013).

Kim, S., Kim, S., Park, J., Ju, S. & Mohammadi, S. Fully transparent pixel circuits driven by random network carbon nanotube transistor circuitry. Acs Nano 4, 2994–2998 (2010).

Wang, C. et al. Wafer-scale fabrication of separated carbon nanotube thin-film transistors for display applications. Nano Lett. 9, 4285–4291 (2009).

Xu, W. Y. et al. Sorting of large-diameter semiconducting carbon nanotube and printed flexible driving circuit for organic light emitting diode (OLED). Nanoscale 6, 1589–1595 (2014).

Zhang, J., Wang, C. & Zhou, C. Rigid/flexible transparent electronics based on separated carbon nanotube thin-film transistors and their application in display electronics. Acs Nano 6, 7412–7419 (2012).

Zhang, J. L. et al. Separated carbon nanotube macroelectronics for active matrix organic light-emitting diode displays. Nano Lett. 11, 4852–4858 (2011).

Cao, Q. et al. Arrays of single-walled carbon nanotubes with full surface coverage for high-performance electronics. Nature Nanotech. 8, 180–186, (2013).

Engel, M. et al. Thin film nanotube transistors based on self-assembled, aligned, semiconducting carbon nanotube arrays. Acs Nano 2, 2445–2452 (2008).

Zhang, J., Wang, C., Fu, Y., Che, Y. & Zhou, C. Air-stable conversion of separated carbon nanotube thin-film transistors from p-type to n-type using atomic layer deposition of high-κ oxide and its application in CMOS logic circuits. Acs Nano 5, 3284–3292 (2011).

Opatkiewicz, J., LeMieux, M. C. & Bao, Z. N. Nanotubes on display: how carbon nanotubes can be integrated into electronic displays. Acs Nano 4, 2975–2978 (2010).

Gu, G. & Forrest, S. R. Design of flat-panel displays based on organic light-emitting devices. IEEE Journal of Selected Topics in Quantum Electronics. 4, 83–99 (1998).

Pimparkar, N., Cao, Q., Rogers, J. A. & Alam, M. A. Theory and practice of “striping” for improved on/off ratio in carbon nanotube thin film transistors. Nano Res. 2, 167–175 (2009).

Heinze, S. et al. Carbon nanotubes as schottky barrier transistors. Physical Review Letters 89, 106801 (2002).

Martel, R. et al. Ambipolar electrical transport in semiconducting single-wall carbon nanotubes. Physical Review Letters 87, 256805 (2001).

Kang, S. J. et al. High-performance electronics using dense, perfectly aligned arrays of single-walled carbon nanotubes. Nature Nanotech. 2, 230–236 (2007).

Wu, C. C., Wu, C. I., Sturm, J. C. & Kahn, A. Surface modification of indium tin oxide by plasma treatment: An effective method to improve the efficiency, brightness and reliability of organic light emitting devices. Appl. Phys. Lett. 70, 1348–1350 (1997).

Acknowledgements

We acknowledge financial support from the Singapore National Research Foundation CRP funding (NRF-CRP2-2007-02) and Singapore MOE AcRF Tier2 Funding (MOE2011-T2-1-137).

Author information

Authors and Affiliations

Contributions

J.P.Z. did the layout designs, SWNT growth, all devices fabrication and SWNT driver circuit testing. J.P.Z. and Q.Z. co-wrote the paper. K.Z. performed SEM characterization and contributed to the SWNT driver circuit testing. J.Q.L. contributed to the initial layout designs and the SWNT growth. Y.B.Z. and X.W.S. contributed to the OLED fabrication and testing. Y.L.W., S.K.R.P. and M.B.C.P. contributed to SWNT preparations and device fabrication. H.V.D., X.W.S. and M.B.C.P. advised on all parts of the project. This project was led by Q.Z. (for SWNT driver circuits), M.B.C.P. (for CNT growth and characterization) and X.W.S. (for OLED fabrication and testing).

Ethics declarations

Competing interests

The authors declare no competing financial interests.

Electronic supplementary material

Rights and permissions

This work is licensed under a Creative Commons Attribution 4.0 International License. The images or other third party material in this article are included in the article’s Creative Commons license, unless indicated otherwise in the credit line; if the material is not included under the Creative Commons license, users will need to obtain permission from the license holder to reproduce the material. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/

About this article

Cite this article

Zou, J., Zhang, K., Li, J. et al. Carbon Nanotube Driver Circuit for 6 × 6 Organic Light Emitting Diode Display. Sci Rep 5, 11755 (2015). https://doi.org/10.1038/srep11755

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/srep11755

This article is cited by

-

Large-area and highly uniform carbon nanotube film for high-performance thin film transistors

Nano Research (2018)

-

Flexible organic heterostructures obtained by MAPLE

Applied Physics A (2018)

-

Review of Electronics Based on Single-Walled Carbon Nanotubes

Topics in Current Chemistry (2017)

-

Carbon Nanotube Thin Film Transistors for Flat Panel Display Application

Topics in Current Chemistry (2016)

Comments

By submitting a comment you agree to abide by our Terms and Community Guidelines. If you find something abusive or that does not comply with our terms or guidelines please flag it as inappropriate.