# SCIENTIFIC REPORTS

### **OPEN**

SUBJECT AREAS: SEMICONDUCTORS ELECTRONIC DEVICES APPLIED PHYSICS

Received 6 November 2014

> Accepted 9 March 2015

Published 20 April 2015

Correspondence and requests for materials should be addressed to H.N.A. (husam. alshareef@kaust.edu. sa)

## Low Temperature Processed Complementary Metal Oxide Semiconductor (CMOS) Device by Oxidation Effect from Capping Layer

Zhenwei Wang<sup>1</sup>, Hala A. Al-Jawhari<sup>2</sup>, Pradipta K. Nayak<sup>1</sup>, J. A. Caraveo-Frescas<sup>1</sup>, Nini Wei<sup>1</sup>, M. N. Hedhili<sup>1</sup> & H. N. Alshareef<sup>1</sup>

<sup>1</sup>Materials Science and Engineering, King Abdullah University of Science & Technology (KAUST), Thuwal 23955-6900, Saudi Arabia, <sup>2</sup>Department of Physics, King Abdulaziz University, Jeddah 21589, Saudi Arabia.

In this report, both p- and n-type tin oxide thin-film transistors (TFTs) were simultaneously achieved using single-step deposition of the tin oxide channel layer. The tuning of charge carrier polarity in the tin oxide channel is achieved by selectively depositing a copper oxide capping layer on top of tin oxide, which serves as an oxygen source, providing additional oxygen to form an n-type tin dioxide phase. The oxidation process can be realized by annealing at temperature as low as 190°C in air, which is significantly lower than the temperature generally required to form tin dioxide. Based on this approach, CMOS inverters based entirely on tin oxide TFTs were fabricated. Our method provides a solution to lower the process temperature for tin dioxide phase, which facilitates the application of this transparent oxide semiconductor in emerging electronic devices field.

omplementary metal oxide semiconductor (CMOS) architecture is the most fundamental building block in many integrated circuits (ICs) largely due to its low power consumption and efficient noise control<sup>1,2</sup>. In the field of transparent electronics, there is a need to develop CMOS devices using transparent oxide thin film transistors (TFTs)<sup>3,4</sup>. In the last decade, both *n*- and *p*-type transparent semiconducting oxides (TSOs) have been studied extensively<sup>5</sup>. Transparent *n*-type oxide based TFTs using tin dioxide (SnO<sub>2</sub>)<sup>6</sup>, indium oxide (In<sub>2</sub>O<sub>3</sub>)<sup>7</sup>, zinc oxide (ZnO)<sup>8</sup> and amorphous indium-gallium-zinc-oxides (IGZO)<sup>9</sup> as active layers have been demonstrated with good electrical properties. Similarly, *p*-type oxide TFTs, based on tin monoxide (SnO)<sup>10,11</sup> and copper-based oxides (CuO and Cu<sub>2</sub>O)<sup>12-15</sup> have been recently reported with encouraging *p*-type performance<sup>10,14,16-18</sup>. In spite of these progressive developments in oxide TFT field, however, the application of TFT-based CMOS in ICs is limited by the incompatible processing procedures required by the *n*- and *p*-type oxide TFTs<sup>19</sup>. Depending on the valence state of tin, semiconducting oxides of tin have been shown to be either *n*-type (for SnO<sub>2</sub>) or *p*-type (for SnO). Each of them exhibits decent electrical performance, and possesses a large optical band gap and, accordingly, good transparency in the visible range. Yet, different deposition parameters and post-deposition annealing (PDA) conditions lead to a complicated fabrication process to integrate these two oxides in the same device.

For both oxides of tin, the PDA process is always required in order to crystallize the amorphous as-deposited films. For *p*-type SnO phase, precisely controlling of the PDA process and maintaining it at moderate condition is of significant importance, since SnO is a thermodynamically metastable phase<sup>20,21</sup>. In particular, although PDA helps to crystallize the as-deposited amorphous SnO, it can also transform SnO to *n*-type SnO<sub>2</sub> phase if over oxidized for long duration or at a higher temperature. In contrast, for *n*-type SnO<sub>2</sub> phase, it is reported that PDA temperature above 300°C is required, which limits the application of SnO<sub>2</sub> on flexible substrates<sup>22</sup>. Thus, different PDA processes required by SnO and SnO<sub>2</sub> phase formation inhibit the integration of these two promising TSOs into the same device.

Recently, we reported that simultaneous growth of *n*-type  $\text{SnO}_2$  and *p*-type SnO films could be achieved by using solution-derived and atomic layer deposited (ALD) aluminum oxide (Al<sub>2</sub>O<sub>3</sub>) as the dielectric layers<sup>19</sup>. It was shown that the presence of large number of hydroxyl groups in the solution-derived Al<sub>2</sub>O<sub>3</sub> can be considered as an additional oxygen source, which contributed to the formation of  $\text{SnO}_2$  phase at low annealing temperature of 210°C. Here, we report a novel approach of transforming SnO to  $\text{SnO}_2$  phase at PDA temperature as low as 190°C,

which facilitates the fabrication of both *p*- and *n*-type TFTs on the same dielectric layer. Such low processing temperature was achieved by using a dual active layer structure (capping layer/SnO layer). We found previously<sup>21</sup> that using Cu<sub>2</sub>O as a capping layer on top of SnO could regulate oxidation of the exposed surface of the SnO *p*-channel, on one hand, and control oxygen diffusion into the underlying SnO<sub>x</sub> film, on the other. The Ellingham diagram for tin oxides and copper oxides is shown in Figure S1. In this type of diagram, oxides located in higher position could oxidize the ones below them. In this system, it is clear that copper oxides can oxidize the underlying tin oxides and would preferentially form SnO<sub>2</sub> over a large temperature range. In this work, we aim to manipulate the Cu<sub>2</sub>O/SnO bilayer scheme to oxidize the *p*-type SnO layer forming n-type SnO<sub>2</sub> at temperature much lower than normally required by annealing SnO in air. The performance of *n*-type bilayer TFT was optimized by controlling the thicknesses of both SnO layer and the capping layer. Finally, transparent CMOS inverters were fabricated by combining our *p*- and *n*type TFTs. Our method provides an alternative solution to lower the process temperature of high-temperature SnO<sub>2</sub> phase, which can enlarge the selection range of TSOs applied on the temperature sensitive flexible substrates.

#### Results

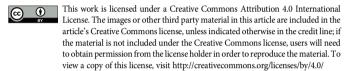

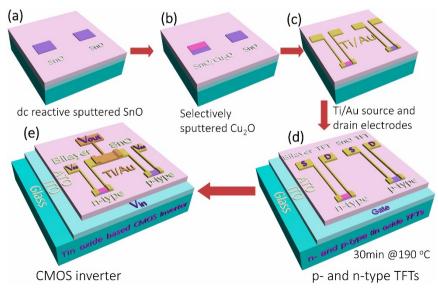

Devices performance. Fabrication process flow for both n- and ptype TFTs and tin oxide TFTs based CMOS inverter is shown in Figure 1. The capacitance and current-voltage curve for the ATO dielectric is presented in Figure S2, the average capacitance is found about 55 nFcm<sup>-2</sup>. For the *p*-type TFT, single SnO layer was used as active layer, while Cu<sub>2</sub>O/SnO bilayer was used for the *n*-type TFT, as depicted in Figure 1(d) and (e). The output and transfer characteristic curves of both TFTs are presented in Figure 2(a)-(d). The output characteristics of the single layer SnO TFT is shown in Figure 2(a), which exhibits p-type conductivity since the source to drain current  $(I_{DS})$  generated under a negative gate voltage  $(V_{GS})$ . The output characteristics of TFT with Cu<sub>2</sub>O/SnO bilayer channel is presented in Figure 2(b). In contrast to the single layer SnO TFT, the TFT with Cu<sub>2</sub>O/SnO bilayer shows an n-type conductivity, since the  $I_{DS}$  generated under a positive  $V_{GS}$ . In both cases, distinct linear and saturation regions can be identified. Current crowding was not observed in the linear region of either output characteristics, indicating Ohmic contact between titanium/gold electrodes and SnO or bilayer channel.

The transfer characteristics of *p*- and *n*-type TFTs are presented in Figure 2(c) and (d), which were measured in the linear operation region under a fixed  $V_{DS}$  of -1 V and +1 V, respectively. With reference to the TFT characterization procedure recommended by J. F. Wager<sup>23</sup>, linear-region field-effect mobility ( $\mu_{\rm FE}$ ) were calculated from the transfer characteristics measured with various W/L ratios ranging from 0.05 to 10. Multiple devices were evaluated for each W/ L ratio, the results are shown in Figure S3. The field-effect mobility,  $\mu_{\rm FE}$ , for *p*- and *n*-type TFTs are calculated to be 2.39  $\pm$  0.13 and 0.23  $\pm$  0.03 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>, respectively. Multiple cycles of dual-sweep scans were performed on each type of TFTs and the results are shown in Figure S3. Both types of TFTs exhibited retracable transfer curves under forward or backward sweep of gate voltage which indicates that both types of TFTs belong to type II: non-equilibrium, steadystate behavior, as suggested by J. F. Wager<sup>23</sup>. The performance of bilayer TFTs with various SnO layer thicknesses and Cu<sub>2</sub>O/SnO thickness ratios are presented in Figure S4. These results show that the device performance strongly depends on the thickness of Cu<sub>2</sub>O and SnO layers. The optimized bilayer TFT was chosen to build CMOS inverters.

The gate leakage current of both *n*- and *p*-channel devices are very low ( $\sim 10^{-11}$  A, Figure 2), which indicates that the effect of gate leakage current on mobility estimation can be ignored. For *p*-channel SnO TFT, the threshold voltage ( $V_{\rm th}$ ), sub-threshold swing (SS) and on-current to off-current ratio ( $I_{\rm on}/I_{\rm off}$ ) are 0.87 V, 7.5 V/dec and  $\sim 10^3$ , respectively. For n-channel device,  $V_{\rm th}$ , SS and  $I_{\rm on}/I_{\rm off}$  were estimated to be 0.58 V, 12 V/dec and  $\sim 10^3$ , respectively. We believe the TFTs performance can be further optimized by changing gate dielectric, tuning the oxygen partial pressure (Opp) when depositing the copper oxide, or by further optimizing the annealing temperature.

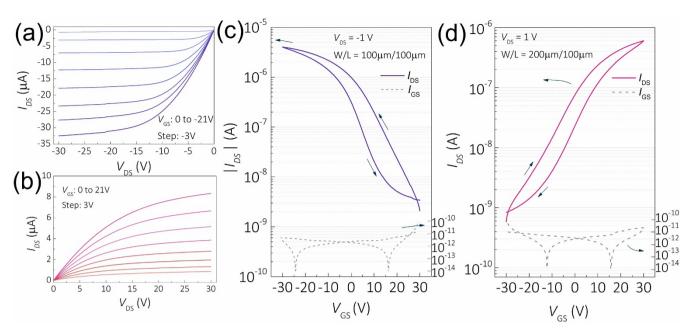

The schematic illustration of our CMOS inverter is presented in Figure 1(e). The ITO bottom gate layer was connected to the input terminal as  $V_{\rm in}$ . The source electrode of *p*-type TFT was used as the  $V_{\rm dd}$  terminal. The source electrode of *n*-type TFT was applied as the  $V_{\rm ss}$  terminal, which was connected to an Agilent high performance ground unit. Finally, the output terminal ( $V_{\rm out}$ ) was built by connecting the drain electrodes of both *p*- and *n*-type TFTs. In order to adjust the transition voltage ( $V_{\rm M}$ , maximum gain voltage) of CMOS inverter, load ratio ( $\beta = \mu \times W/L$ ) of each type TFT was accurately measured and calculated. Finally, by selecting large (W/L)<sub>n</sub>/(W/L)<sub>p</sub> ratio, compatible *p*- and *n*-type load ratios ( $\beta_n/\beta_p \sim 1$ ) were achieved and the  $V_{\rm M}$  was located at about  $V_{\rm dd}/2$ . The voltage transfer curves

Figure 1 | Flow diagram for TFTs and CMOS inverters fabrication. The detailed structures of TFTs and CMOS inverters are shown in (d) and (e).

Figure 2 | Output and transfer characteristics of *p*- and *n*-type TFTs. Output characteristics for (a) *p*-type SnO TFT and (b) *n*-type bilayer TFT; Transfer characteristics for (c) *p*-type SnO TFT and (d) *n*-type bilayer TFT.

(VTC) of the selected CMOS inverters are shown in Figure 3(a). The  $V_{\rm M}$  is sensitive to the  $\beta_n/\beta_p$  and the  $V_{\rm th}$  of each type oxide TFT. Gain of CMOS inverter was calculated by evaluating the negative slope  $(-dV_{\rm out}/dV_{\rm in})$  of each VTC curve and the results are shown in Figure 3(a), our CMOS inverters show a maximum gain of ~4. The VTC curve of the optimized CMOS inverter under linearly increased  $V_{\rm dd}$  is presented in Figure 3(b). We attribute the low gain value to the large SS and the low  $I_{on}/I_{off}$  of TFTs, which may be optimized by replacing the dielectric layer, stacking a passivation layer on top of device.

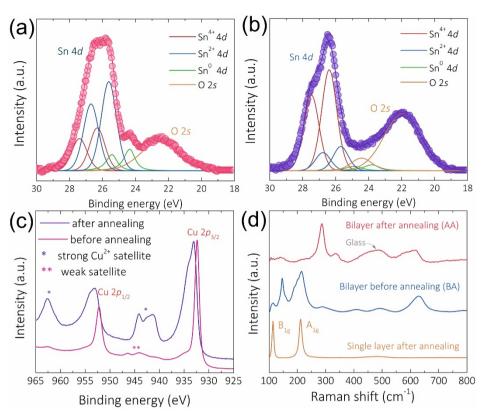

**Materials Characterization.** Recently, we have demonstrated a detailed investigation of the origin of *p*-type transport behavior in SnO channel TFTs<sup>10</sup>. Here we focus on the origin of *n*-type transport behavior in Cu<sub>2</sub>O/SnO bilayer TFTs. To investigate the oxidation state of tin in Cu<sub>2</sub>O/SnO bilayer, X-ray photoelectron spectroscopy (XPS) was performed on the before annealing (BA) and after annealing (AA) bilayer samples, which were prepared under the same conditions used in the TFTs fabrication (i.e., annealing was performed at 190°C for 30 min in air). The XPS spectra of the Sn 4*d* peaks of BA and AA samples are presented in Figure 4(a) and (b), respectively. It is reported that the Sn 4*d* peak is a doublet and consists of Sn 4*d*<sub>3/2</sub> and Sn 4*d*<sub>5/2</sub> located at binding energy of 27.3 and 26.2 eV, respectively<sup>24,25</sup>. The deconvolution of both Sn 4*d* peaks of BA and AA samples show Sn 4*d*<sub>3/2</sub> and Sn 4*d*<sub>5/2</sub> doublet peaks, with a chemical shift of ~0.7 eV between doublet peaks, which is

consistent with the report from Themlin *et al.*<sup>26</sup> For Sn<sup>4+</sup>, Sn  $4d_{3/2}$ and Sn  $4d_{5/2}$  peaks are located at 27.4 and 26.3 eV, respectively; in contrast, for Sn<sup>2+</sup>, Sn  $4d_{3/2}$  and Sn  $4d_{5/2}$  peaks are located at 26.7 and 25.6 eV, respectively. This is a clear evidence of the co-existance of both SnO and SnO<sub>2</sub> phases in our bilayers. In case of both BA and AA samples, Sn 4d peak corresponding to metallic tin could be observed, this is nature of direct current (dc) reactive magnetron sputtering thin film and is consistent with our previous report<sup>10</sup>. Interestingly, the atomic content (in at%) of Sn<sup>4+</sup>, Sn<sup>2+</sup> and Sn<sup>0</sup> are determined to be 28, 62 and 10%, respectively in BA sample, and 78, 16 and 6%, respectively in AA sample. In the BA sample, the dominant phase is determined to be SnO. However, the content of *n*-type SnO<sub>2</sub> phase significantly increases in AA sample, and becomes dominant (~78 at %) after the PDA process, which we believe is the origin of *n*-type transport behavior in the bilayer TFTs. The analysis result of XPS Sn 3d spectra of BA and AA sample is in agreement of XPS Sn 4d spectra (Figure S5).

XPS Cu 2*p* peaks were obtained to investigate the phase tranformation of copper in bilayer sample during the PDA process. Both XPS Cu 2*p* doublets of BA and AA samples are shown in Figure 4(c). It is reported that XPS Cu 2*p* doublet consists of two main peaks at 952 (Cu 2*p*<sub>1/2</sub>) and 932 eV (Cu 2*p*<sub>3/2</sub>) and some satellite peaks may exist depending on the oxidation state of Cu<sup>27,28</sup>. According to our XPS results, doublets attributed to Cu 2*p*<sub>1/2</sub> and Cu 2*p*<sub>3/2</sub> can be explicitly detected in both samples. For the BA sample, peaks located

Figure 3 | Performances of CMOS inverters. (a) Voltage transfer and gain characteristics of CMOS inverters with variable channel size ratios. (b) Voltage transfer curves of optimized CMOS inverter.

**Figure 4** | Materials characterizations for TFT channel layers. XPS Sn 4*d* peaks of (a) before and (b) after annealing bilayer sample; (c) XPS Cu 2*p* peaks of bilayer sample. (d) Raman spectra of before and after annealing bilayer samples and SnO single layer sample.

at 932.2 and 952.1 eV are attributed to the core level Cu  $2p_{3/2}$  and Cu  $2p_{1/2}$ , respectively. In addition to these two peaks, some weak satellite peaks can also be observed at ~945 and ~962 eV. Similar results have also been reported by Barreca et al.<sup>27</sup>, indicating that copper oxide in BA sample exists as Cu<sub>2</sub>O phase. For Cu 2p spectra of AA sample, doublet peaks with  $\sim 1$  eV chemical shift from the BA one was observed. Main peaks located at 933.2 and 953.1 eV, these two peaks correspond to Cu  $2p_{3/2}$  and Cu  $2p_{1/2}$  of the CuO phase, respectively<sup>29</sup>. In addition to these two main peaks, three other intense satellite peaks located at 941.2, 944.2 and 962.6 eV were observed in the AA sample. These peaks were reported as shake-up satellites<sup>30,31</sup>, a phenomenon where the emitted photoelectrons encounter the valence electrons that are being excited to higher energy level(s). This process would decrease the kinetic energy of these photoelectrons, thus satellite peaks with higher binding energy will appear in XPS spectra, correspondingly. The appearance of these intense satellite peaks is attributed to the completely oxidized CuO phase. Therefore, after the PDA process, higher oxidized state CuO is formed.

Raman spectra of BA and AA samples are shown in Figure 4(d). In case of the BA sample, peaks at 112, 147, 213 and 631 cm<sup>-1</sup> corresponding to the Cu<sub>2</sub>O phase were observed, similar results were also reported by Zoolfakar and Solache-Carranco *et al.*<sup>28,32</sup> For the AA sample, Raman peaks located at 287, 340 and 621 cm<sup>-1</sup> were observed, which were assigned to the CuO phase, similar results were reported by Zoolfakar and Rashad *et al.*<sup>28,33</sup> The phase analysis from Raman spectrum for BA and AA sample is consistent with the XPS results. Raman spectra for post-annealed single layer sample is also shown in Figure 4(d), in which, two peaks at 112.1 and 211 cm<sup>-1</sup> can be observed, which were assigned to the A<sub>1g</sub> and B<sub>1g</sub> vibration modes of tin monoxide, respectively<sup>34</sup>.

UV-Vis transmission spectra of SnO single layer and  $Cu_2O/SnO$  bilayer are presented in supplementary information (Figure S6). Films were deposited on glass substrates under the same condition

as the actual device. The transmittances of single layer and bilayer samples are above 85% and 54% respectively, in wavelength range from 400 to 700 nm.

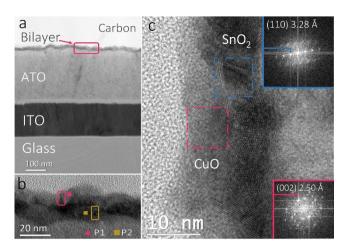

High resolution cross-sectional transmission electron microscopy (TEM) was performed to investigate the structure and phase composition of the post annealed bilayer sample, the results are shown in Figure 5. The cross-sectional TEM micrograph of the bilayer device is presented in Figure 5(a), from which the stack structure of glasssubstrate/ITO (150 nm)/ATO (220 nm)/bilayer can be seen clearly. High resolution TEM cross-sectional micrograph is shown in Figure 5(c), in which copper oxide and tin oxide laver stack can be seen as a well-defined bilaver structure. Fast Fourier transform (FFT) analysis was performed in selected areas marked in Figure 5(c) and the results are shown as the insets. The FFT analysis for tin oxide zone shows inter-planar spacing (d) value of  $\sim$  3.28 Å which is close to the  $d_{110}$  of SnO<sub>2</sub> (JCPDS card No. 00-041-1445). For copper oxide, d value of  $\sim$ 2.50 Å could be measured from the FFT pattern, which is close to the  $d_{002}$  in CuO (JCPDS card No. 00-002-1040). Figure 5(b) shows the larger scale TEM micrograph for the bilayer sample, pink rectangular indicates the CuO layer and the yellow one for SnO<sub>2</sub> layer. Energy dispersive X-ray spectrometer (EDS) point analysis was performed on the selected small zones labeled as P1 and P2 in the TEM image. The obtained results show only copper peaks in P1 and tin peaks can be detected in P2 (Figure S7). This result is consistent with the FFT analysis, which confirms the bilayer sample in fact exists as CuO/SnO<sub>2</sub> bilayer stacking structure. High resolution cross-sectional TEM micrograph of as-deposited bilayer sample is shown in Figure S8, in which both the CuO<sub>2</sub> and SnO layer are found to be amorphous.

#### Discussion

It has been reported that the metastable SnO phase could be oxidized to SnO<sub>2</sub> at temperature higher than 300°C in air<sup>22</sup>. However, for the bilayer case, we found that temperature as low as 190°C is enough to

Figure 5 | Cross-sectional TEM characterizations for bilayer sample. TEM micrograph of (a) the stack structure of glass-substrate/ITO (150 nm)/ATO (220 nm)/bilayer and (b) details of copper oxide (pink rectangular) and tin oxide (yellow rectangular) zones, EDS point analysis positions were labeled as P1 and P2. (c) High resolution TEM micrograph of bilayer sample, FFT analysis of selected zones are depicted as the insets.

realize this oxidation process. There are three points that can help us understand the low-temperature phase transition from SnO to SnO<sub>2</sub> in our bilayer films. Firstly, according to the bilayer structure (Figure 5, S7 and S8), copper oxide layer is located directly above tin oxide layer, which makes copper oxide a good candidate as the oxygen source. Secondly, the tin oxide layers were deposited and annealed at the same time, but the as-deposited single layer tin oxide TFT was only transformed to *p*-type from the same annealing, which indicates the *n*-type behavior of bilayer TFT comes from the additional oxidation effect from the copper oxide capping layer. Finally, according to the Ellingham diagram (Figure S1), the corresponding lines of copper oxides are located above the lines for tin oxides within a large temperature range, which confirms the thermodynamical possibility of copper oxide serving as oxygen source and oxidizing the underlying tin oxide layer. Combining the XPS, Raman and TEM results, we can conclude that during the PDA process the surface cuprous oxide (Cu<sub>2</sub>O) was oxidized to CuO and oxygen atoms from copper oxide layer diffused into the underlying tin oxide layer, forming *n*-type tin dioxide phase at temperature as low as  $190^{\circ}$ C.

In conclusion, both p- and n-type tin oxide based TFTs were acquired from the same low temperature PDA process in air. N-type bilayer TFT was achieved by applying dual-active-layer structure, i.e. Cu<sub>2</sub>O/SnO channel layer, while the SnO single layer TFT shows ptype polarity. Based on these tin oxides TFTs, CMOS inverters were successfully fabricated. Our materials characterization results demonstrate that the copper oxide layer served as the oxygen source, which oxidized the underlying as-deposited tin oxide layer, forming *n*-type SnO<sub>2</sub> phase at temperature as low as 190°C. Therefore, by selectively depositing a capping layer, variable valence states of tin oxides were achieved simultaneously, which enables the low-temperature tuning of transporting polarity of tin oxides. Our method provides an alternative solution to lower the process temperature of SnO<sub>2</sub>, which normally requires an annealing temperature over  $300^\circ C^{22}.$  This approach facilitates the application of transparent semiconductors in emerging electronic devices.

#### **Methods**

**Device fabrication.** Commercial indium tin oxide (ITO) and a bilayer of aluminum oxide and titanium oxide (ATO) deposited by atomic layer deposition on glass substrates were used as the gate electrode and dielectric, respectively. The glass substrates with ITO and ATO films were purchased from Planar Systems Inc., Finland. Substrates were cleaned sequentially by acetone, isopropanol and de-ionized water using an ultrasonic cleaner (Branson 3510, Switzerland), for 15 min in each solution and finally dried by nitrogen gas. Tin oxide and copper oxide thin films were

deposited by direct current reactive magnetron sputtering (Angstrom Engineering Inc, Canada) at room temperature using a mixture of argon and oxygen gases. Tin oxide films were deposited at an oxygen partial pressure (Opp) of 9%, dc power of 20 W and pressure of 1.8 mTorr. After deposition of tin oxide films, half of substrate was covered by Kapton tape as protection mask for selective deposition of the capping layer. Copper oxide films were then deposited at Opp of 10%, dc power of 50 W, and pressure of 4.5 mTorr. 2-inch tin metal target (purity  $\sim$ 99.99%) and 2-inch copper target (purity ~99.99%) were used for sputtering. The growth rates of tin oxide and copper oxide are ~0.65 and 1 Å/s, respectively. Titanium (10 nm) and gold (70 nm) source and drain electrodes were deposited by e-beam evaporation. Both channel and electrode layers were patterned by lift-off process using  $1.4 \ \mu m$  photoresist (AZ 1512HS from MicroChemicals). Multiple channel widths and lengths were patterned in each substrate, varying from 10 to 200  $\mu$ m. Post-deposition annealing of the devices was performed at 190°C for 30 min in a tube furnace (Thermo Scientific) in air. SnO single layer and Cu<sub>2</sub>O/SnO bilayer thin films were prepared under the same deposition condition for materials characterization.

Device and material characterizations. The capacitance curve for the ATO dielectric was measured by a capacitance meter (Agilent E4981A). The electrical performance of p- and p-type TFTs and CMOS inverters were characterized at room temperature in dark using a semiconductor device analyzer (Agilent B1500A) and a microprobe station (Summit-11600 AP, Cascade Microtech). The chemical composition of the Cu<sub>2</sub>O/SnO bilayer films was analyzed by x-ray photoelectron spectroscopy (XPS) using an Axis Ultra DLD spectrometer (Kratos Analytical, UK). Raman spectra were analyzed at room temperature at wavenumber range from 100 to 800 cm<sup>-1</sup> by LabRAM ARAMIS Raman Microscope (Horiba Scientific) and a 473 nm cobalt laser source was used for excitation. Cross-sectional TEM sample was prepared by a focused ion beam (FIB) from Quanta 3D FEG (FEI). About 500 nm amorphous carbon layer was deposited by a carbon coater (Emitech K950X) as protection layer before performing the cross-sectional sample preparation by FIB. High resolution TEM image of bilayer sample was investigated by a Titan ST (FEI) transmission electron microscope. The UV-Vis transmittance spectra was measured by Evolution 600 UV-Vis Spectrophotometer (Thermo Scientific).

- Martins, R. et al. Complementary metal oxide semiconductor technology with and on paper. Advanced Materials 23, 4491–4496 (2011).

- Liu, P.-T., Chou, Y.-T., Teng, L.-F. & Fuh, C.-S. High-gain complementary inverter with InGaZnO/pentacene hybrid ambipolar thin film transistors. *Applied Physics Letters* 97, 083505 (2010).

- 3. Wager, J. F. Transparent electronics. Science 300, 1245–1246 (2003).

- Na, J. H., Kitamura, M. & Arakawa, Y. Organic/inorganic hybrid complementary circuits based on pentacene and amorphous indium gallium zinc oxide transistors. *Applied Physics Letters* 93, 213505 (2008).

- Fortunato, E., Barquinha, P. & Martins, R. Oxide semiconductor thin-film transistors: a review of recent advances. *Advanced Materials* 24, 2945–2986 (2012).

- Presley, R. E. et al. Tin oxide transparent thin-film transistors. Journal of Physics D: Applied Physics 37, 2810–2813 (2004).

- Dhananjay et al. Complementary inverter circuits based on p-SnO<sub>2</sub> and n-In<sub>2</sub>O<sub>3</sub> thin film transistors. Applied Physics Letters 92, 232103 (2008).

- Fortunato, E. et al. Recent advances in ZnO transparent thin film transistors. Thin Solid Films 487, 205–211 (2005).

- Nomura, K. *et al.* Room-temperature fabrication of transparent flexible thin-film transistors using amorphous oxide semiconductors. *Nature* 432, 488–492 (2004).

- Caraveo-Frescas, J. A. *et al.* Record mobility in transparent *p*-type tin monoxide films and devices by phase engineering. ACS Nano 7, 5160–5167 (2013).

- Fortunato, E. et al. Transparent p-type SnOx thin film transistors produced by reactive rf magnetron sputtering followed by low temperature annealing. Applied Physics Letters 97, 052105 (2010).

- Sung, S.-Y. *et al.* Fabrication of *p*-channel thin-film transistors using CuO active layers deposited at low temperature. *Applied Physics Letters* 97, 222109 (2010).

- Pattanasattayavong, P., Thomas, S., Adamopoulos, G., McLachlan, M. A. & Anthopoulos, T. D. P-channel thin-film transistors based on spray-coated Cu<sub>2</sub>O films. Applied Physics Letters 102, 163505 (2013).

- 14. Fortunato, E. et al. Thin-film transistors based on p-type Cu<sub>2</sub>O thin films produced at room temperature. Applied Physics Letters **96**, 192102 (2010).

- 15. Kim, S. Y. et al. P-channel oxide thin film transistors using solution-processed copper oxide. ACS Applied Materials & Interfaces 5, 2417–2421 (2013).

- Togo, A., Oba, F., Tanaka, I. & Tatsumi, K. First-principles calculations of native defects in tin monoxide. *Physical Review B* 74, 195128 (2006).

- Ogo, Y. *et al.* Tin monoxide as an s-orbital-based *p*-type oxide semiconductor: Electronic structures and TFT application. *Physica Status Solidi A* 206, 2187–2191 (2009).

- Granato, D. B., Caraveo-Frescas, J. A., Alshareef, H. N. & Schwingenschlögl, U. Enhancement of *p*-type mobility in tin monoxide by native defects. *Applied Physics Letters* **102**, 212105 (2013).

- Nayak, P. K. *et al.* Thin film complementary metal oxide semiconductor (CMOS) device using a single-step deposition of the channel layer. *Sci. Rep.* 4, 4672 (2014).

- Batzill, M. & Diebold, U. The surface and materials science of tin oxide. Progress in Surface Science 79, 47–154 (2005).

- 21. Al-Jawhari, H. A., Caraveo-Frescas, J. A., Hedhili, M. N. & Alshareef, H. N. P-type Cu<sub>2</sub>O/SnO bilayer thin film transistors processed at low temperatures. ACS Applied Materials & Interfaces 5, 9615–9619 (2013).

- 22. Pan, X. Q. & Fu, L. Oxidation and phase transitions of epitaxial tin oxide thin films on (1012) sapphire. *Journal of Applied Physics* **89**, 6048–6055 (2001).

- Wager, J. F. Transfer-curve assessment of oxide thin-film transistors. Journal of the Society for Information Display 18, 749–752 (2010).

- Akgul, F. A. et al. Structural and electronic properties of SnO<sub>2</sub>. Journal of Alloys and Compounds 579, 50–56 (2013).

- Themlin, J. M. et al. Resonant-photoemission study of SnO<sub>2</sub>: Cationic origin of the defect band-gap states. *Physical Review B* 42, 11914–11925 (1990).

- Themlin, J. M. et al. Characterization of tin oxides by x-ray-photoemission spectroscopy. *Physical Review B* 46, 2460–2466 (1992).

- 27. Barreca, D., Gasparotto, A. & Tondello, E. CVD  $\rm Cu_2O$  and CuO nanosystems characterized by XPS. Surface Science Spectra 14, 41–51 (2007).

- Zoolfakar, A. S. et al. Nanostructured copper oxides as ethanol vapour sensors. Sensors and Actuators B: Chemical 185, 620–627 (2013).

- Ghijsen, J. et al. Electronic structure of Cu<sub>2</sub>O and CuO. Physical Review B 38, 11322–11330 (1988).

- 30. Biesinger, M. C., Lau, L. W. M., Gerson, A. R. & Smart, R. S. C. Resolving surface chemical states in XPS analysis of first row transition metals, oxides and hydroxides: Sc, Ti, V, Cu and Zn. *Applied Surface Science* 257, 887–898 (2010).

- Poulston, S., Parlett, P. M., Stone, P. & Bowker, M. Surface oxidation and reduction of CuO and Cu<sub>2</sub>O studied using XPS and XAES. Surface and Interface Analysis 24, 811–820 (1996).

- Solache-Carranco, H. *et al.* Photoluminescence and X-ray diffraction studies on Cu<sub>2</sub>O. *Journal of Luminescence* 129, 1483–1487 (2009).

- Rashad, M., Rüsing, M., Berth, G., Lischka, K. & Pawlis, A. CuO and Co<sub>3</sub>O<sub>4</sub> nanoparticles: synthesis, characterizations, and Raman spectroscopy. *Journal of Nanomaterials* 2013, 714853 (2013).

34. Geurts, J., Rau, S., Richter, W. & Schmitte, F. J. SnO films and their oxidation to SnO<sub>2</sub>: Raman scattering, IR reflectivity and X-ray diffraction studies. *Thin Solid Films* 121, 217–225 (1984).

#### Acknowledgments

Research reported in this publication was supported by King Abdullah University of Science and Technology (KAUST).

#### Author contributions

Z.W., H.A.A. and H.N.A. designed the research, analyzed the data and co-wrote the report. Z.W., P.K.N. and J.A.C. carried out the device fabrications and characterizations. N. W. contributed for the TEM imaging. M.N.H. contributed with film characterizations by XPS.

#### Additional information

Supplementary information accompanies this paper at http://www.nature.com/ scientificreports

Competing financial interests: The authors declare no competing financial interests.

How to cite this article: Wang, Z. *et al*. Low Temperature Processed Complementary Metal Oxide Semiconductor (CMOS) Device by Oxidation Effect from Capping Layer. *Sci. Rep.* 5, 9617; DOI:10.1038/srep09617 (2015).