# SCIENTIFIC REPORTS

### **OPEN**

#### SUBJECT AREAS:

SENSORS AND BIOSENSORS NANOSENSORS ELECTRONIC PROPERTIES AND DEVICES

> Received 2 May 2014

> Accepted 6 June 2014

Published 7 July 2014

Correspondence and requests for materials should be addressed to Z.Y.Z. (zyzhang@pku. edu.cn) or L.-M.P. (Impeng@pku.edu.cn)

## Graphene/Si CMOS Hybrid Hall Integrated Circuits

Le Huang<sup>1</sup>, Huilong Xu<sup>1</sup>, Zhiyong Zhang<sup>1</sup>, Chengying Chen<sup>2</sup>, Jianhua Jiang<sup>2</sup>, Xiaomeng Ma<sup>1</sup>, Bingyan Chen<sup>1</sup>, Zishen Li<sup>1</sup>, Hua Zhong<sup>1</sup> & Lian-Mao Peng<sup>1</sup>

<sup>1</sup>Key Laboratory for the Physics and Chemistry of Nanodevices and Department of Electronics, Peking University, Beijing 100871, China, <sup>2</sup>ASIC and System Department, Institute of Microelectronics of Chinese Academy of Sciences, Beijing 100029, China.

Graphene/silicon CMOS hybrid integrated circuits (ICs) should provide powerful functions which combines the ultra-high carrier mobility of graphene and the sophisticated functions of silicon CMOS ICs. But it is difficult to integrate these two kinds of heterogeneous devices on a single chip. In this work a low temperature process is developed for integrating graphene devices onto silicon CMOS ICs for the first time, and a high performance graphene/CMOS hybrid Hall IC is demonstrated. Signal amplifying/process ICs are manufactured via commercial 0.18 um silicon CMOS technology, and graphene Hall elements (GHEs) are fabricated on top of the passivation layer of the CMOS chip via a low-temperature micro-fabrication process. The sensitivity of the GHE on CMOS chip is further improved by integrating the GHE with the CMOS amplifier on the Si chip. This work not only paves the way to fabricate graphene/Si CMOS Hall ICs with much higher performance than that of conventional Hall ICs, but also provides a general method for scalable integration of graphene devices with silicon CMOS ICs via a low-temperature process.

raphene is a two-dimensional material with sp<sup>2</sup> structure that has been considered as an outstanding functional material for constructing high-performance nanodevices such as radio frequency (RF) transistors<sup>1-3</sup>, photo-detectors<sup>4</sup>, flexible electronics<sup>5</sup>, gas sensors<sup>6</sup> and magnetic field detectors<sup>7,8</sup>. Although graphene has many excellent physical properties such as extremely high intrinsic carrier mobility, ultrathin body, long mean-free-path, great thermoelectric property and stability<sup>9-14</sup>, this material also suffers from some major drawbacks. One of the vital intrinsic shortcomings of graphene is that the material has a zero band gap. This problem leads to small current on/off ratio and no stable saturation region in output characteristics of graphene transistors, limiting the applications of graphene in some mainstream fields such as digital electronics and amplifiers<sup>1,14</sup>. Instead of modifying the intrinsic drawbacks of graphene intentionally, graphene has also been used in such fields as sensors<sup>4-8</sup> and ambipolar electronics<sup>15,16</sup> which can take full advantages of its excellent properties while avoiding intrinsic drawbacks. Therefore an advisable and feasible route for graphene devices is to integrate them complementarily with the mainstreaming silicon CMOS circuits to construct more powerful hybrid integrated circuits (ICs) or systems, in which both graphene devices and Si CMOS circuits can do what they are good at. To realize such a hybrid ICs, one has to overcome the challenge as to how to integrate these two kinds of heterogeneous devices on the same chip, and this work aims to develop exactly this technique, i.e. a graphene device fabrication process that is compatible with Si CMOS technology to spread the applications of graphene devices and to extend the functions of Si CMOS ICs.

Previously graphene has been demonstrated as an ideal material for constructing graphene Hall element (GHE)<sup>7,8,17</sup>, which takes full advantage of graphene's excellent properties such as high carrier mobility, ultrathin body, low noise and great stability, while avoids the main shortcoming, *i.e.* zero band gap. In particular, GHE has exhibited great advantages over commercial Silicon and even III-V compounds Hall sensors in many key figures of merits, e.g. sensitivity, linearity, resolution and temperature stability<sup>7,8,17</sup>. Moreover, a scalable fabrication process has been developed which might promise commercial applications of GHE in the future<sup>18</sup>.

In most applications, the output Hall voltage from a Hall element is very small, and Hall ICs composed of Hall elements and cascaded signal amplifying/processing circuits are widely used in advanced applications. Until now, silicon based Hall ICs remain the mainstream since silicon CMOS technology is the most mature and advanced technology for realizing advanced signal amplifying/processing circuits<sup>19</sup>. Although individual Hall sensors made from III-V compounds may outperform silicon based Hall element, these high performance Hall sensors are hardly used in Hall ICs since it is hard to fabricate signal amplifying/processing ICs using III-V semiconductors<sup>20,21</sup>. Ideally we would want to combine the best Hall elements with the most advanced ICs, but it is

difficult to integrate the III-V based high-performing Hall sensors with advanced Silicon CMOS ICs on the same chip due to the complicated and demanding heterogeneous fabrication processes<sup>22-24</sup>. The situation becomes very different when graphene is considered. Several works have been demonstrated to utilize graphene as interconnects and integrate them with Si CMOS IC<sup>25-27</sup>. Although it remains challenging to fabricate digital ICs or amplifier using graphene, GHEs may in principle be fabricated on silicon CMOS ICs as well. This is because only low temperature processes are involved in graphene transfer and sensor fabrications. The excellent combination between GHE and Si CMOS ICs should further improve the performance of Hall ICs.

In this work, we develop a low-temperature process for fabricating graphene devices which is compatible with Si-based CMOS technology, and demonstrate the integration of GHEs with Si CMOS ICs on the same chip. Signal amplifying/processing ICs are manufactured via commercial 0.18  $\mu$ m silicon CMOS technology, and GHEs are fabricated on top of the passivation layer of the Si CMOS chip via a low-temperature micro-fabrication process. The hybrid ICs work well, exhibiting full function of the Hall ICs at a low supply voltage of 3.3 V, i.e. the GHE can convert a magnetic signal to electrical signal which can then be processed/amplified by the Si CMOS ICs. In addition, this work also provides a general method for scalable integration of graphene devices and silicon CMOS ICs.

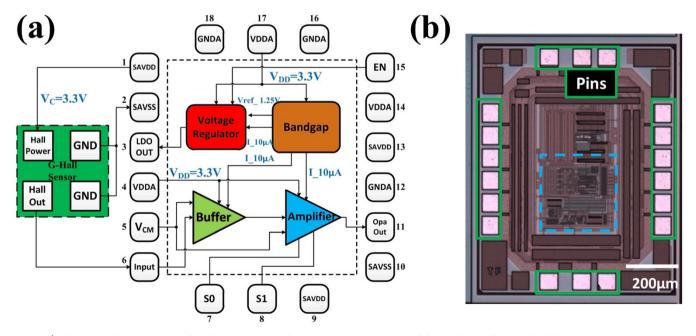

The graphene/silicon CMOS hybrid IC to be demonstrated here is a widely-used linear Hall IC, and its function diagram is depicted in Figure 1a. This IC contains five components, *i.e.* a buffer, a voltage amplifier, a bandgap, a voltage regulator and a Hall element. The Hall element used here is fabricated using graphene as the channel material<sup>7,8,17</sup>. The other four blocks are amplifying and assistant IC modules, and are realized via matured 0.18  $\mu$ m silicon CMOS technology. The output signal from the GHE is first transmitted to the CMOS buffer module with storage and modulation functions, and is then inputted to the amplifier module. This module is designed to amplify the input AC signal with two optional amplifications (35 and 50 at 1 kHz) via setting the level of the pin named S0 (#7) and S1 (#8) respectively (Figure 1a). The bandgap module works as a power reference, which supplies a constant current (DC 10  $\mu$ A) to power the buffer, amplifier and voltage regulator; and a constant voltage (DC 1.25 V) for the voltage regulator. The regulator, controlled by the pin named EN (#15), outputs a constant voltage (DC 3 V), which is an alternative power supply for the GHE. The pin named V<sub>CM</sub> (#5), biased with DC 1.65 V, offers a common mode reference voltage for the buffer and amplifier. The Si CMOS IC contains totally 98 transistors, and is designed to run at a direct current (DC) voltage of 3.3 V (the standard supply voltage for 0.18 um ICs). In contrast to conventional linear Hall ICs, the GHE in the hybrid Hall ICs works in voltage mode<sup>8</sup>, and the complex module for supplying constant current for energizing Hall element in current mode may thus be saved. This simplification profits from the highly linear response of the GHE in voltage mode, which is another important advantage of the GHE when compared with other conventional Hall elements.

Silicon based CMOS ICs were first fabricated via commercial 0.18  $\mu$ m Si CMOS technology. Figure 1b shows a typical optical image of an as-fabricated chip with an overall size of 5 mm  $\times$  5 mm and an active area of 820  $\mu$ m  $\times$  1030  $\mu$ m. Totally 18 pins enclosed by solid green line in Figure 1b are arranged around the chip as interconnecting ports. The area for fabricating the GHE is enclosed by the dashed blue square. This region is on top of the Si<sub>3</sub>N<sub>4</sub> passivation layer above the silicon devices, and hybrid graphene/Si CMOS IC is thus a three-dimensional IC<sup>28</sup>.

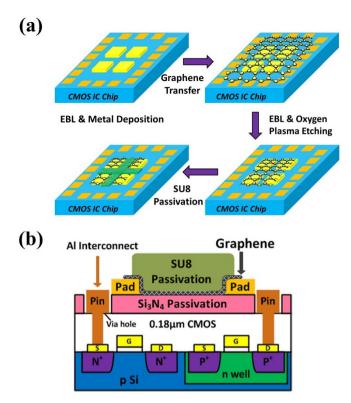

The GHE was fabricated on top of the  $Si_3N_4$  passivation layer of the finished Si CMOS chip via a scalable micro processing technology, and detailed fabrication process flow is shown in Figure 2a. The structure of the completed graphene/silicon hybrid Hall IC is depicted in Figure 2b. Since the GHE is fabricated on the passivation layer above the Si CMOS circuits, no additional chip area is needed. The construction method demonstrated here is in fact a transistor stacking three-dimensional integrating method<sup>28</sup>, which is a big challenge in conventional semiconducting technology since the temperatures required for building another layer of high-performing semiconductor devices would destroy any metallic interconnection wire and cause migration of transistor dopants on previous layers. However, this problem is avoided in the construction of our

**Figure 1** | **Silicon based CMOS chip before the integration of GHE.** (a) Circuit diagram of the graphene-silicon hybrid chip. The pins named SAVDD (#1) and VDDA (#17) denote In/Out (IO) power supply and analogue power supply respectively, which are identical in this work (DC 3.3 V). The pins named SAVSS (#2) and GNDA (#16) denote IO ground and analogue ground respectively, which are also identical. (b) Typical optical image showing the unprocessed CMOS chip. Totally 18 pins of the chip are marked by the solid green frame. The dashed blue square denotes the area where the GHE is to be fabricated.

Figure 2 | Fabrication process flow and structure of the graphene-Silicon hybrid Hall chip. (a) Process flow showing the fabrication of a GHE on the Si CMOS chip. All processes are carried out via micro fabrication technology based on EBL. (b) Depicted side-view of the completed graphene-Silicon hybrid chip. The chip is fabricated by using 0.18  $\mu$ m technology based on conventional Silicon CMOS structure. The GHE is fabricated on the passivation layer of the Si chip.

graphene/Si hybrid ICs, since no high-temperature process is required, *i.e.* both material transfer and fabrication of graphene devices on top of the Si chip are carried out at temperature no more than  $180^{\circ}$ C.

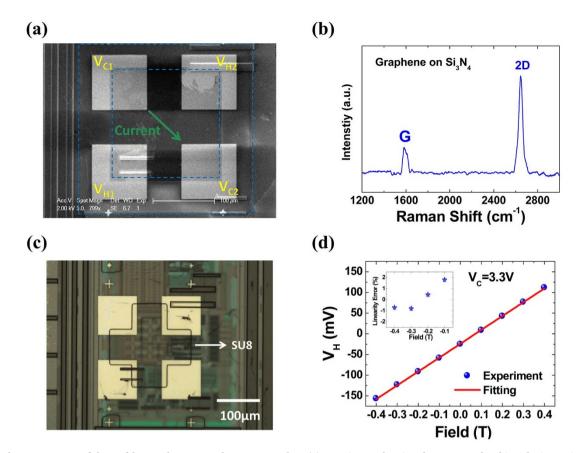

Before being connected to the Si CMOS ICs, the GHE fabricated on Si<sub>3</sub>N<sub>4</sub> passivation layer of the Si chip was characterized and results are shown in Figure 3. It should be noted that graphene is not visible under optical microscope since the beneath Si<sub>3</sub>N<sub>4</sub> layer is not designed with the right thickness to contrast graphene visible<sup>29</sup>. Instead scanning-electron-microscope (SEM) is used to observe graphene and device structures here. SEM image of a typical GHE after oxygen plasma etching process (but before being passivated by SU8) is shown in Figure 3a, in which we can readily distinguish the active graphene channel from the etched graphene area by the contrast of the image. The square shaped graphene channel remains uniform and complete on top of the Si<sub>3</sub>N<sub>4</sub> passivation layer, suggesting that our modified transfer process of graphene works well. The graphene on Si CMOS chip is further characterized via Raman spectroscopy, and a typical Raman spectrum is shown in Figure 3b. The 2D/G peak ratio of about 3 indicates that the graphene is monolayer as well as high-quality, suggesting that our fabricating process is almost harmless to graphene. It should be noted that the Raman spectrum shown in Figure 3b was obtained by subtracting the substrate  $(Si_3N_4)$  signal from the total signal (Figure S1, Supplementary information), since the graphene is located on the surface of Si<sub>3</sub>N<sub>4</sub> passivation layer of the chip. The final GHE after passivation is shown in Figure 3c, where the graphene layer is hardly visible because of the limited contrast between the substrate chip and graphene.

The magnetic response of the GHE was measured via a Hall probe station. When a magnetic field is applied normal to the channel of the GHE which is biased with a constant voltage or current over the electrodes V<sub>C1</sub> and V<sub>C2</sub>, a Hall voltage is generated over the other two opposite electrodes V<sub>H1</sub> and V<sub>H2</sub>. The magnetic field dependent Hall voltages are measured in constant voltage ( $V_c = 3.3$  V, which is consistent with the operating voltage of the CMOS ICs) mode, and results are shown in Figure 3d. It is obvious that Hall voltage increases linearly with increasing magnetic field, and the linearity error is smaller than 2% over a large magnetic field range from -0.4 T to 0.4 T, showing excellent linearity of the GHE. As a comparison, the typical linearity error is about 10% for high-performance two-dimensional electron gas (2DEG) Hall elements at magnetic field of less than 0.1 T<sup>23</sup>. The excellent linearity of the GHE over a wide magnetic field range in voltage mode enables us to use it in voltage mode. As a result, the complex constant current source widely used in conventional Hall ICs can be saved and the hybrid graphene/Si Hall ICs can be significantly simplified.

The slope of the V<sub>H</sub>-B curve in Figure 3d reflects the absolute sensitivity S<sub>A</sub> of the GHE, *i.e.* about 0.335 V T<sup>-1</sup>. The voltage related sensitivity S<sub>V</sub> is then retrieved to be 0.10 T<sup>-1</sup>, yielding a carrier mobility of about 1000 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> for the graphene channel. This mobility is much smaller than those of the GHE on SiO<sub>2</sub>/Si substrate, which have typical values of 6000 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1 8,17</sup>. Nevertheless, the achieved voltage related sensitivity is still higher than that of silicon based Hall sensors fabricated via CMOS technology, which have typically a sensitivity of about 0.07  $T^{-1}$  owing to the lower carrier mobility in Si<sup>20</sup>. The low graphene channel mobility is mainly attributed to the scattering and charge impurities introduced by Si<sub>3</sub>N<sub>4</sub> substrate and SU8 passivation layer since fabricating process and structure of the GHE are both far from optimized. It is expected that the performance of the integrated GHE on Si chip can be greatly improved by perfecting the fabrication process, device geometry and substrate preparation or treatment conditions. On the other hand, if the GHE is stimulated by a constant current of 100  $\mu$ A (Figure S2, Supplementary information), the current related sensitivity is derived to be 200 V A<sup>-1</sup> T<sup>-1</sup>, which is again much larger than that of typical silicon based Hall sensor, i.e. 100 V A<sup>-1</sup> T<sup>-1 20</sup>.

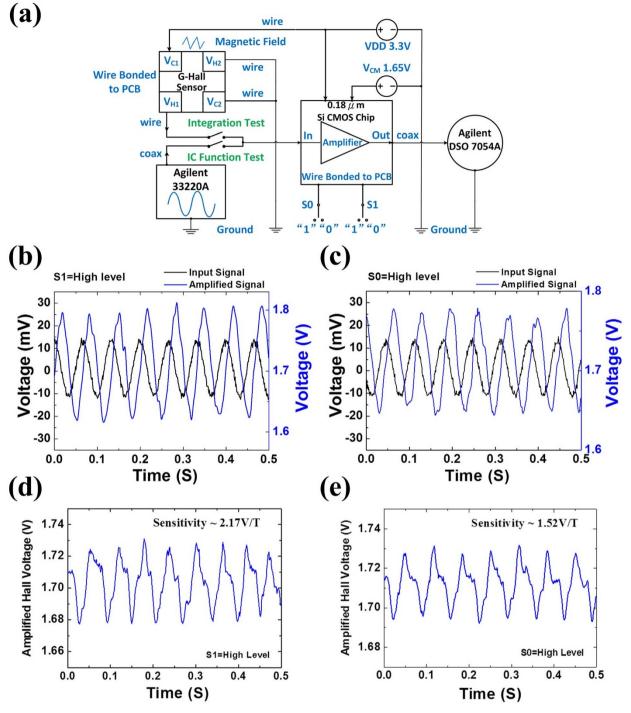

After fabrication and characterization on the GHE were finished, the silicon CMOS ICs and GHE were wire-bonded to a printed circuit board (PCB) for further IC function and integration test (Figure S3, Supplementary information). Output signals of the hybrid Hall ICs under an alternating magnetic field were measured using a test circuitry as shown in Figure 4a. During the test, the input signals of the chip were selected either from an Agilent function waveform generator 33220A or the GHE output, which correspond to IC function test and integrated system test respectively. We first tested the functions of the Si CMOS ICs. As a reference, a sinusoidal wave (generated by the function waveform generator 33220A) with a frequency of 15 Hz and a peak-to-peak voltage of 25 mV was inputted into the Si CMOS amplifier, and its output signal was observed by an oscilloscope (Agilent DSO7054A). Figures 4b and 4c show the input and output signals in amplification mode S1 and S0 respectively. It is evident that the silicon ICs can function normally at low frequency with amplifications of about 7.2 in S1 and 4.8 in S0, which are about one seventh of those at 1 kHz (Figure S4a and S4b, Supplementary information). The damping of amplification at low frequency is resulted from the coupling and shunt capacitances of the ICs at low frequency outside the band width of the amplifier (Figure S4c and S4d, Supplementary information).

In performing graphene/Si hybrid Hall ICs system test, the GHE and CMOS ICs are biased with one constant power supply of 3.3 V, and the hybrid ICs chip is measured under an alternating magnetic field which is generated by rotating a magnet using an electro-motor. The magnetic field at the measurement position varies periodically following the position of rotating magnet with amplitude of 21.7 mT and a frequency of 15 Hz (Figure S5, Supplementary information). As a magnetic sensor, the GHE on the chip should convert the

Figure 3 | Characterization of the as-fabricated GHE on silicon CMOS chip. (a) SEM image showing the GHE on the chip. The image is taken after completing the oxygen plasma etching process. The area enclosed by the two blue dashed squares is the place where graphene is etched away. The green arrow denotes current flow from electrode  $V_{C1}$  to electrode  $V_{C2}$ . (b) Typical Raman spectrum obtained from the CVD graphene on top of the Si<sub>3</sub>N<sub>4</sub> passivation layer of the Si chip. The wavelength of the excitation laser is 633 nm. (c) An optical image showing the GHE after the device is passivated by a cross shaped SU8 layer, which is marked in the image by a white arrow. (d) A typical linear fitting of the Hall voltage versus magnetic field in voltage mode. Inset: linearity error of the GHE in a magnetic field ranging from -0.4 T to -0.1 T.

alternating magnetic field into an alternating Hall voltage signal. The alternating output signal of the GHE is then sent to the Si CMOS IC which amplifies the Hall voltage with optional amplification S1 or S0, and the final output signals are shown in Figure 4d and 4e respectively. It should be pointed out that the noise in the final result is mainly resulted from the low frequency 1/f noise of the device which dominates the measurement system at 15 Hz. This represents the upper limit of the alternating magnetic field frequency that we can realize in this work. It should be noted that the Si CMOS chip is designed to work at high frequency of above 1 kHz, which is much higher than the maximum alternating magnetic field frequency of 15 Hz used here. In principle, the signal/noise ratio of our Hall ICs can be significantly improved if the Hall measurements were carried out at higher frequency, e.g. at 1 kHz. Nevertheless, the output signals of the hybrid ICs follow the same 15 Hz frequency of the rotating magnet, suggesting that the output signals of the hybrid ICs is stimulated by the external magnetic field. The voltage amplitude of the output signal is 47 mV in mode S1 and 33 mV in mode S0, yielding an absolute sensitivities of the integrated Hall ICs of 2.17 V  $T^{-1}$  and 1.52 V  $T^{-1}$  respectively. These values are much higher than that of the as-fabricated GHE before being integrated to Si CMOS ICs. The increased sensitivity of the Hall ICs may be attributed to the silicon amplifying module in the Si CMOS ICs, and the actual amplifications is 6.6 in S1 and 4.6 in S0 respectively, which are very close to the measured values of 7.2 and 4.8 from Figure 4b and 4c. In the same way the voltage related sensitivity of the Hall ICs is also improved by the silicon amplifier and reaches 0.66 T<sup>-1</sup> in mode S1 and 0.46 T<sup>-1</sup> in mode S2, which are 6.6 and 4.6 times higher

than that of the GHE in mode S1 and S2 respectively. It should be noted that the best performance of the hybrid Hall ICs cannot be fully demonstrated at very low operating frequency here because it falls outside the designed bandwidth of the Si CMOS ICs. Nevertheless the graphene/Si hybrid CMOS Hall ICs work well, demonstrating certain advantages of the hybrid Hall ICs, *i.e.* the sensitivity of the fabricated GHEs is higher than that of silicon Hall elements and can be further increased directly by the integrated Si CMOS amplifier on the chip. Although the final sensitivity of the hybrid Hall ICs is still lower than that of the best commercial silicon Hall ICs<sup>30</sup>, there remains a huge space to optimize the hybrid Hall ICs. Among other factors, the carrier mobility of graphene is many times higher and the temperature stability of the GHE is much better than that of Si. We thus expect that via further optimizing the fabrication process of GHEs and the silicon amplifying circuits, the graphene/Si CMOS Hall ICs might eventually outperform all conventional Hall ICs.

In conclusion, we have developed a low-temperature process for fabricating graphene Hall sensors and integrating them with silicon CMOS ICs. Signal amplifying/processing ICs are manufactured via commercial 0.18  $\mu$ m silicon CMOS technology, and GHEs are fabricated on the passivation layer of the Si CMOS chip via a low-temperature micro-fabrication process. The hybrid ICs work well and fully exhibit the function of Hall ICs at a low supply voltage of 3.3 V, *i.e.* GHE converts a magnetic signal to electrical signal which can be further amplified by Si CMOS ICs. The as-fabricated GHE on CMOS chip exhibits higher sensitivity than that of silicon Hall element, and the sensitivity can be further improved by the cascaded Si CMOS amplifier. This work not only paves the way for fabricating

**Figure 4** | **Electronic measurements of the hybrid Hall IC.** (a) Measurement circuitry. IC function test results showing the input and output signals when the amplifier is selected as (b) Amplification S1 and (c) Amplification S0. The input signals of (b) and (c) are sinusoidal waves with a frequency of 15 Hz and a peak-to-peak voltage of 25 mV, which are produced by the function waveform generator. Test results for the Hall IC under an alternating magnetic field when the amplifier is selected as (d) Amplification S1 and (e) Amplification S0. The input signals of (d) and (e) are collected from the output of the GHE.

graphene/Si CMOS Hall ICs with much higher performance than that of conventional Hall ICs, but also provides a general method for scalable integration of graphene devices and silicon CMOS ICs.

#### Methods

**Fabrication of GHE devices on Si-CMOS chip.** (1) Ti/Au (10/90 nm) metal contacts and alignment marks for next patterning process are patterned using electron-beam lithography (EBL) based on PMMA, and deposition is made by electron beam evaporator, followed by a standard lift-off process in acetone. Before the exposure, PMMA 200k is spun onto the chip at a speed of 4000 round per minute, and then the chip is baked on the hotplate at 180°C for 3 minutes. (2) Chemical vapor deposition (CVD) graphene is synthetized on a Pt foil and transferred to the Si chip via a well-developed bubbling method<sup>31</sup>. (3) The Si<sub>3</sub>N<sub>4</sub> surface of the Si chip is pre-cleaned through oxygen plasma and functionalized with 3-aminopropyltriethoxysilane (APTES) before transferring graphene<sup>8,18</sup>. This step is crucial to keep the transferred graphene complete and stable on Si<sub>3</sub>N<sub>4</sub> surface due to the strong interaction between APTES and graphene, which is harmless to graphene sample<sup>18</sup>. Moreover, our previous work has proven that GHE with APTES modification exhibites higher transconductance and smaller Dirac point voltage compared with that without modification<sup>8</sup>. (4) The transferred graphene is patterned to form a channel for the Hall element through another EBL on PMMA 200k, followed by an oxygen plasma

The supplementary information contains detailed descriptions of graphene characterization, Hall measurements, and graphene/Si CMOS hybrid Hall ICs.

- Schwierz, F. Graphene transistor. Nature Nanotechnol. 5, 487–496; DOI: 10.1038/ nnano.2010.89 (2010).

- Liao, L. *et al.* Scalable fabrication of self-aligned graphene transistors and circuits on glass. *Nano Lett.* 12, 2653–2657; DOI: 10.1021/nl201922c (2012).

- 3. Lin, Y. M. *et al.* Wafer-scale graphene integrated circuit. *Science* **332**, 1294–1297 (2011).

- Mueller, T., Xia, F. & Avouris, P. Graphene photodetectors for high-speed optical communications. *Nat. Photon.* 4, 297–301; DOI: 10.1038/nphoton.2010.40 (2010).

- Eda, G., Fanchini, G. W. & Chhowalla, M. Large-area ultrathin films of reduced graphene oxide as a transparent and flexible electronic material. *Nat. Nanotechnol.* 3, 270–274; DOI: 10.1038/nnano.2008.83 (2008).

- Schedin, F. et al. Detection of individual gas molecules adsorbed on graphene. Nat. Mater. 6, 652–655; DOI: 10.1038/nmat1967 (2007).

- Huang, L. et al. Ultra-sensitive graphene Hall elements. Appl. Phys. Lett. 104, 183106; DOI: 10.1063/1.4875597 (2014).

- 8. Xu, H. L. *et al.* Batch-fabricated high-performance graphene Hall elements. *Sci. Rep.* **3**, 1207; DOI: 10.1038/srep01207 (2013).

- Novoselov, K. S. et al. Electric field effect in atomically thin carbon films. Science 306, 666–669 (2004).

- Geim, A. K. & Novoselov, K. L. The rise of graphene. Nat. Mater. 6, 183–191; DOI:10.1038/nmat1849 (2007).

- 11. Castro Neto, A. H., Guinea, F., Peres, N. M. R., Novoselov, K. S. & Geim, A. K. The electronic properties of graphene. *Rev. Mod. Phys.* 81, 109–162; DOI: 10.1103/ RevModPhys.81.109 (2009).

- Marko, B., Hagen, K. & Klaus, K. Carbon-based field-effect transistors for nanoelectronics. *Adv. Mater.* 21, 2586–2600; DOI: 10.1002/adma.200803582 (2009).

- Meric, I. et al. Current saturation in zero-bandgap, topgated graphene field-effect transistors. Nat. Nanotechnol. 3, 654–659; DOI: 10.1038/nnano.2008.268 (2008).

- Xu, D., Ivan, S., Anthony, B. & Eva, Y. A. Approaching ballistic transport in suspended graphene. *Nat. Nanotechnol.* 3, 491–495; DOI:10.1038/ nnano.2008.199 (2008).

- Wang, H., Nezich, D., Kong, J. & Palacios, T. Graphene frequency multipliers. IEEE Electron Device Lett. 30, 547–549; DOI: 10.1109/LED.2009.2016443 (2009).

- Wang, Z. X. et al. A high-performance top-gate graphene field-effect transistor based frequency doubler. *Appl. Phys. Lett.* 96, 173104; DOI: 10.1063/1.3413959 (2010).

- Xu, H. L. et al. Flicker noise and magnetic resolution of graphene hall sensors at low frequency. Appl. Phys. Lett. 103, 112405; DOI: 10.1063/1.4821270 (2013).

- Shi, R. B., Xu, H. L., Chen, B. Y., Zhang, Z. Y. & Peng, L. M. Scalable fabrication of graphene devices through photolithography. *Appl. Phys. Lett.* **102**, 113102; DOI: 10.1063/1.4795332 (2013).

- Ripka, P. & Janosek, M. Advances in magnetic field sensors. *IEEE Sensors Journal* 10, 1108–1116; DOI: 10.1109/JSEN.2010.2043429 (2010).

- Popovic, R. S. Hall Effect Devices. Second Edition, Institute Physics Publishing, 2004.

- Boero, G., Demierre, M., Besse, P. A. & Popovic, R. S. Micro-Hall devices: performance, technologies and applications. *Sensors and Actuators A* 106, 314–320; DOI: 10.1016/S0924-4247(03)00192-4 (2003).

- Bando, M. *et al.* High sensitivity and multifunctional micro-Hall sensors fabricated using InAlSb/InAlSb/InAlSb heterostructures. *Appl. Phys. Lett.* **105**, 07E909; DOI: 10.1063/1.3074513 (2009).

- Kunets, V. P. *et al.* Highly sensitive micro-Hall devices based on Al0.12In0.88Sb/ InSb heterostructures. J. Appl. Phys. 98, 014506; DOI: 10.1063/1.1954867 (2005).

- Hara, T., Mihara, M., Toyoda, N. & Zama, M. Highly linear GaAs Hall devices fabricated by ion implantation. *IEEE Transactions on Electron Devices* ED-29, 78–82 (1982).

- Lee, K. J., Qazi, M., Kong, J. & Chandrakasan, A. P. Low-swing signaling on monolithically integrated global graphene interconnects. *IEEE T. Electron Dev.* 57, 3418; DOI: 10.1109/TED.2010.2083667 (2010).

- Chen, X. Y. *et al.* Fully integrated graphene and carbon nanotube interconnects for gigahertz high-speed CMOS electronics. *IEEE T. Electron Dev.* 57, 3137; DOI: 10.1109/TED.2010.2069562 (2010).

- Lee, K. J., Park, H., Kong, J. & Chandrakasan, A. P. Demonstration of a subthreshold FPGA using monolithically integrated graphene interconnects. *IEEE T. Electron Dev.* **60**, 383; DOI: 10.1109/TED.2012.2225150 (2013).

- Robert, S. P. Three-dimensional integrated circuits and the future of system-onchip designs. *Proceedings of the IEEE* 94, 1214–1224; DOI: 10.1109/ JPROC.2006.873612 (2006).

- Blake, P. et al. Making graphene visible. Appl. Phys. Lett. 91, 063124; DOI: 10.1063/1.2768624 (2007).

- Popovic, R. S., Randjelovic, Z. & Manic, D. Integrated Hall-effect magnetic sensors. Sensors and Actuators A 91, 46–50 (2001).

- Gao, L. B. *et al.* Repeated growth and bubbling transfer of graphene with millimetre-size single-crystal grains using platinum. *Nature. Comm.* 3, 699; DOI: 10.1038/ncomms1702 (2012).

- Al-Mumen, H., Dong, L. X. & Li, W. SU-8 doped and encapsulated n-type graphene nanomesh with high air stability. *Appl. Phys. Lett.* 103, 232113; DOI: 10.1063/1.4841615 (2013).

#### **Acknowledgments**

This work was supported by the Ministry of Science and Technology of China (Grant Nos. 2011CB933001 and 2011CB933002), National Science Foundation of China (Grant Nos. 61322105, 61271051, 61376126, 61321001 and 61390504), and Beijing Municipal Science and Technology Commission (Grant Nos. Z131100003213021 and 20121000102).

#### Author contributions

Z.Z. and L.M.P. designed the experiment, L.H., H.X., X.M., B.C., Z.L. and H.Z. performed the growth and transfer of graphene, device fabrication and characterization. L.H., C.C. and J.J. designed the silicon CMOS ICs. L.H., Z.Z. and L.M.P. analyzed the data and co-wrote the manuscript. All authors discussed the results and commented on the manuscript.

#### Additional information

Supplementary information accompanies this paper at http://www.nature.com/ scientificreports

Competing financial interests: The authors declare no competing financial interests.

How to cite this article: Huang, L. *et al.* Graphene/Si CMOS Hybrid Hall Integrated Circuits. *Sci. Rep.* 4, 5548; DOI:10.1038/srep05548 (2014).

This work is licensed under a Creative Commons Attribution-NonCommercial-NoDerivs 4.0 International License. The images or other third party material in this article are included in the article's Creative Commons license, unless indicated otherwise in the credit line; if the material is not included under the Creative Commons license, users will need to obtain permission from the license holder in order to reproduce the material. To view a copy of this license, visit http:// creativecommons.org/licenses/by-nc-nd/4.0/