ARTICLE

https://doi.org/10.1038/s42005-018-0102-8

OPEN

# An adapted method for analyzing 4H silicon carbide metal-oxide-semiconductor field-effect transistors

Martin Hauck<sup>1</sup>, Johannes Lehmeyer<sup>1</sup>, Gregor Pobegen <sup>1</sup>, Heiko B. Weber <sup>1</sup> & Michael Krieger <sup>1</sup>

Silicon carbide (SiC) metal-oxide-semiconductor field-effect transistors (MOSFETs) are key devices for next-generation power electronics. However, accurate determination of device parameters from 3-terminal characteristics is hampered by the presence of interface traps. Here we present a method that, in contrast to previous evaluation schemes, explicitly considers those defects. A well-tractable parametrization of the SiC/SiO<sub>2</sub>-specific interface trap spectrum is introduced that reflects the body of known data. With this ingredient, we develop an analysis that targets for an accurate determination of device parameters from simple 3-terminal characteristics. For its validation, we investigate MOSFETs with significantly different defect densities. The resulting parameters – charge carrier density, mobility and threshold voltage – are in excellent agreement with Hall effect investigations on the very same devices, avoiding systematic errors inherent to conventional evaluation techniques. With this adapted scheme, 4H-SiC power MOSFETs, even packaged, can be meaningfully characterized, speeding up innovation cycles in energy-saving power electronics.

<sup>&</sup>lt;sup>1</sup>Lehrstuhl für Angewandte Physik, Department Physik, Friedrich-Alexander-Universität Erlangen-Nürnberg (FAU), Staudtstraße 7, 91058 Erlangen, Germany. <sup>2</sup>Kompetenzzentrum für Automobil- und Industrieelektronik (KAI) GmbH, Europastraße 8, 9524 Villach-St. Magdalen, Austria. Correspondence and requests for materials should be addressed to M.K. (email: michael.krieger@fau.de)

ilicon carbide (SiC) is the most important wide-bandgap semiconductor material for next-generation power electronic devices. The commercialization of SiC devices started in 2001 with the introduction of the first 4H-SiC-based Schottky diode<sup>1</sup>. A great challenge for SiC technology is the fabrication of metal-oxide-semiconductor field-effect transistors (MOSFETs). Such unipolar transistors are, e.g., a power-saving substitution for silicon-based insulated-gate bipolar transistors (IGBTs) as power switches<sup>2</sup>. A material peculiarity is the high density of defects at the 4H-SiC/SiO<sub>2</sub> interface near the conduction band edge, which gives a limitation that has been partially resolved by the introduction of a post-oxidation annealing (POA) process in nitric oxide  $(NO)^{3,4}$ . That paved the way for commercial 4H-SiC MOSFETs. Nevertheless, there is still room for substantial performance improvements: despite nitridation processes, the density of interface traps  $(D_{it})$  is still at a very high level compared to, e.g., silicon MOSFET devices<sup>5,6</sup>. The performance of a MOSFET is often characterized by extraction of the mobility and the threshold voltage from 3-terminal characteristics<sup>7,8</sup>. In such commonly used evaluation schemes, originally developed for silicon based devices, the  $D_{it}$  is neglected and the inversion charge carrier density in the MOSFET channel is estimated from a simple plate capacitor approximation. Applied to SiC, this leads to an underestimation of the charge carrier drift mobility<sup>6,9</sup>. To experimentally distinguish between mobility and inversion charge carrier density, Hall-effect measurements in the MOSFET channel are the method of choice. They are, however, time-consuming and require special geometries with additional probes. This requirement is incompatible with typical power MOSFET designs with vertical channels (VMOS, Trench MOS).

The aim of this work is to provide a method for analyzing the performance of 4H-SiC n-MOSFETs of any geometry from a simple 3-terminal characterization. It includes the specific distribution of defects at the 4H-SiC/SiO<sub>2</sub> interface into the modeling of the drain current. A best fit to experimental transfer characteristics results in a reliable determination of the charge carrier mobility, the threshold voltage and the  $D_{it}$  in the energy range relevant for the MOSFET performance, without the need of Hall-effect measurements.

## Results

**Modeling.** The density of interface states in 4H-SiC MOS structures has been extensively studied. A common observation is a relatively flat distribution in the bandgap with an exponential increase towards the conduction band edge  $E_{\rm C}^{10-12}$ . Whereas the former part is often assigned to carbon-related defects directly at

the interface<sup>10,13</sup>, the increase towards  $E_{\rm C}$  stems from electron traps in the oxide near the 4H-SiC/SiO<sub>2</sub> interface, so-called near interface traps (NITs)<sup>14</sup>. Those traps exhibit a rather sharp distribution in energy close to the conduction band edge of 4H-SiC<sup>15-17</sup>. Their microscopic origin is still unclear, but intrinsic defects in amorphous SiO<sub>2</sub><sup>18</sup> as well as extrinsic carbon-related defects near the interface<sup>19</sup> have been suggested.

We propose an empirical parametrization that summarizes the body of findings in Eq. (1). The constant  $D_0$  reflects the above mentioned flat distribution of traps directly at the interface. The Gaussian term expresses the observed exponential increase of the density of NITs towards  $E_C$  and respects an overall finite number of defects.

$$D_{\rm it} = D_0 + \frac{D_1}{\sigma \cdot \sqrt{\pi/2}} \cdot \exp\left(-\frac{2 \cdot (E - E_0)^2}{\sigma^2}\right). \tag{1}$$

A width in the range of  $\sigma = (100...200)$  meV and a position in the range of  $E_0 - E_C = (10...150)$  meV of the Gaussian part is consistent with the majority of reported experimental studies. This parametrization is the key ingredient to the subsequent method.

Transport in the channel is crucially determined by the inversion charge carrier density  $n_{\rm inv}$  as a response to the gate voltage and is directly affected by the density of interface traps (Eq. (1)). The link between  $n_{\rm inv}$  and  $V_{\rm G}$  is the surface Fermi potential  $\phi_{\rm S} = (E_{\rm F} - E_{\rm i}^{\rm interface})/e$ .  $V_{\rm G}$  is determined by Eq. (5) (see methods section).

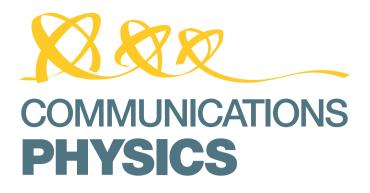

$n_{\rm inv}(\phi_{\rm S})$  can be calculated either by using the quasi-classical charge sheet model (CSM)<sup>20</sup> or by self-consistently solving the Schrödinger-Poisson equations (SPS)<sup>21,22</sup>. The CSM uses the 3D density of states in the conduction band to calculate the inversion charge carrier density by integration of the electron density in the inversion channel. It will turn out that this is an oversimplification relevant for our problem. The CSM introduces an artificial offset to the surface Fermi potential at a given charge carrier density, because it neglects the formation of 2D sub-bands in the inversion layer. Figure 1a and b compares the density of states in the inversion channel, Fig. 1c the band bending in the semiconductor and Fig. 1d  $n_{inv}$  as a function of  $\phi_s$ . For MOS parameters taken from the samples discussed later the CSM analysis introduces an error of more than 50 meV to  $\phi_{\rm S}$ , as compared to the more refined SPS calculations. In the following, only the SPS analysis is employed.

**Fig. 1** Charge sheet model vs. Schrödinger-Poisson-Solver. **a** along the *z*-axis projected density of states in the inversion channel used in the charge sheet model (CSM); **b** density of states calculated using a Schrödinger-Poisson-Solver (SPS),  $E_{\rm c}^{\rm CSM}$  and  $E_{\rm F}^{\rm SPS}$  are the positions of the Fermi energy calculated via CSM and SPS respectively; **c** conduction bands of 4H-SiC calculated via CSM (blue) or SPS (red), z = 0 denotes the 4H-SiC/SiO<sub>2</sub> interface, **d** dependence of the inversion charge carrier density  $n_{\rm inv}$  from the surface Fermi potential  $\phi_{\rm s} = (E_{\rm F} - E_{\rm i}^{\rm interface})/e$ . The formation of the 2D sub-bands leads to a shift of at least 50 meV of the Fermi energy further into the conduction band compared to the quasi-classical solution of the CSM

With  $V_G(\phi_S)$ ,  $Q_{sc}(\phi_S)$  and  $n_{inv}(\phi_S)$ , the transfer characteristics  $I_D - V_G$  can be calculated using

shift the curve on the *x*-axis and cannot be independently determined.

$$I_{\rm D} = \frac{W}{L} \cdot \boldsymbol{e} \cdot \boldsymbol{n}_{\rm inv} (\phi_{\rm S}(V_{\rm G})) \cdot \boldsymbol{\mu} \cdot (V_{\rm D} - I_{\rm D} \boldsymbol{R}_{\rm S}), \qquad (2)$$

where W and L denotes the width and the length of the inversion channel, respectively, and  $R_{\rm S}$  is the series resistance. The charge carrier mobility  $\mu$  can either be assumed constant, or more specific models can be implemented. Since Coulomb scattering is typically the dominating mobility limiting mechanism in lateral 4H-SiC n-MOSFETs, we opted for a power law description that reflects the potential screening with increasing charge carrier density<sup>23</sup>:

$$\mu(n_{\rm inv}) = \mu_0 \cdot \left(\frac{n_{\rm inv}}{n_0}\right)^{\zeta},\tag{3}$$

with  $n_0$  and  $\zeta$  being an arbitrary reference value and an empirical exponent, respectively.

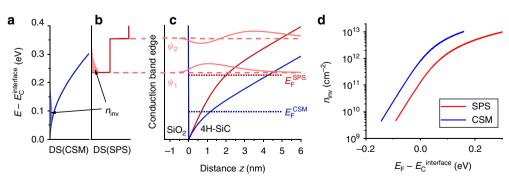

Figure 2 illustrates the effect of different parameters on the transfer characteristics on a linear and on a logarithmic scale, see in particular the figure caption. It turns out that each of the parameters  $\mu$ ,  $D_1$ , and  $D_0$  affects specific features of the shape of the transfer characteristics and can, thus, be well distinguished. In contrast, the neutral level  $E_n$  and the fixed oxide charge  $Q_{ox}$  both

**Fig. 2** Influence of model parameters. Scheme of the influence of the important simulation parameters on the transfer characteristic of a 4H-SiC n-channel metal-oxide-semiconductor field-effect transistor on **a** a linear and **b** a logarithmic scale. The constant part of the  $D_{it}$ -distribution  $D_0$  primarily adjusts the slope of the curve at low gate voltages on the logarithmic scale. The fixed oxide charge  $Q_{ox}$  shifts the gate voltage. The mobility  $\mu$  adjusts the slope at high gate voltages on the linear scale and the Gaussian part of the  $D_{it}$ -distribution  $D_1$  smears out the onset of the drain current and shifts the threshold voltage (which also does the parameter  $D_{0}$ , but  $D_0$  is already determined by the subthreshold region)

**Analysis.** In order to test the proposed evaluation scheme, MOSFETs with Hall bar geometries were designed and fabricated using an industrial process. They allow for measurements of Hall effect as well as of 3-terminal characteristics on the same device. Two series of samples with drastically different  $D_{it}$  were produced by variation of the process gas of the post-oxidation annealing (POA): nitric oxide (sample #1) and oxygen (sample #2).

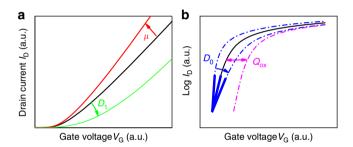

Figure 3 shows the transfer characteristics of two of the investigated Hall-MOSFETs. During the measurement, a sufficient measurement delay after each gate voltage change ensured relaxation of the interface defect occupation into thermodynamical equilibrium. The symbols represent the measurement data and the lines are the least square fits of the model including the general shape of the  $D_{\rm it}$  (Eq. 1). Table 1 summarizes the extracted performance parameters and compares the results to two frequently used conventional methods for performance analysis of MOSFETs and to results obtained by Hall-effect investigations. The Hall-effect method is the only one that independently and directly measures the charge carrier density and the Hall mobility. Therefore, it is the most reliable method and is taken as benchmark.

From Table 1 it can be seen that the two conventional methods based on transfer characteristics clearly underestimate the mobility due to negligence of interface traps. This effect becomes more pronounced for higher  $D_{it}$  and, remarkably, even leads to a deviation by more than one order of magnitude in the case of sample #2. This drastic discrepancy of the all-important parameter  $\mu$  could so far be resolved only in Hall-effect measurements requiring specific sample structures<sup>6,9,24,25</sup>. In contrast, the mobility values of our adapted method are in excellent agreement with the benchmark values obtained by Hall effect.

Furthermore, the introduced method delivers reliable values for the threshold voltage  $V_{\rm T}$ , i.e., the onset of strong inversion ( $\phi_{\rm S} = -\phi_{\rm B}$ ). These values are much lower than the values extracted from linear extrapolation in conventional methods. This is obvious because the  $D_{\rm it}$  close to  $E_{\rm C}$  causes a soft turn-on of the transfer characteristics with notable deviation from linearity.

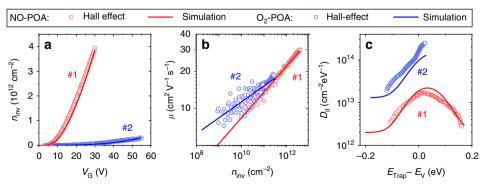

**Comparison to gate voltage-dependent Hall-effect investigations**. For closer analysis the proposed method is compared to Hall-effect measurements for various gate voltages, see Fig. 4. We find excellent agreement for the extracted inversion charge carrier densities and the charge carrier mobilities between both methods, for both samples (see Fig. 4a, b). In contrast to the large difference

**Fig. 3** Comparison of measurement and simulation. Transfer characteristics of sample #1 (a) and sample #2 (b). The symbols represent the measured drain currents and the solid line is a best fit using our modeled  $D_{it}$ , Eq. (1). The data are shown on a linear and a logarithmic scale to show the excellent agreement of model and experiment

in  $n_{inv}$ , both devices have nearly identical charge carrier mobilities, depending only on the charge carrier densities, a fact that would have been overlooked by traditional evaluation schemes of 3-terminal measurements. An apparent difference of roughly a factor of two can rather be traced back to a generally lower charge carrier density in sample #2 than to a mobility enhancement by nitridation. An analysis of an extended data set, including nominally identical Hall-MOS devices with POAs in nitric oxide and oxygen shows that the difference in the curves displayed in Fig. 4b is rather within the device-to-device variation than a systematic influence of the post-oxidation treatment. Exponents  $\zeta$  in the power law in the range of 0.1...0.4 have been extracted. Altogether, nitridation of the oxide does not affect the charge carrier mobility, but strongly the field-effect efficiency, in agreement with previous studies<sup>6</sup>.

From Hall-effect measurements it is also possible to derive the density of interface traps  $D_{it}^{26,27}$ . The results are presented in Fig. 4c (symbols). The evaluation scheme is described in the methods section. As expected, post-oxidation annealing in nitric oxide strongly reduces the density of interface traps. Moreover, these data provide an independent reconfirmation that our initial assumption which lead to Eq. (1) is valid: the  $D_{it}$  has a maximum near the conduction band edge of 4H-SiC. The solid curves represent the  $D_{it}$  distribution according to Eq. (1) with the parameters  $D_{0}$ ,  $D_{1}$ ,  $E_{0}$ , and  $\sigma$  extracted from 3-terminal measurements (Fig. 3) using our proposed method. The comparison to the point-by-point analysis from Hall-effect measurements displays a nearly quantitative agreement. The predictive power of our method is remarkable, as it results from a

| Sample | Method                    | μ (cm²<br>V <sup>-1</sup> s <sup>-1</sup> ) | V <sub>T</sub> (V) | D <sub>it</sub> <sup>max</sup> (cm <sup>-2</sup> eV <sup>-1</sup> ) |

|--------|---------------------------|---------------------------------------------|--------------------|---------------------------------------------------------------------|

| #1     | Field effect <sup>8</sup> | 21.0                                        | 14.1               | _                                                                   |

|        | Ghibaudo <sup>7</sup>     | 18.8                                        | 13.3               | _                                                                   |

|        | Hall effect               | 29.4                                        | _                  | 5.7 · 10 <sup>12</sup>                                              |

|        | This work                 | 28.1                                        | 2.2                | 2.8 · 10 <sup>12</sup>                                              |

| #2     | Field effect <sup>8</sup> | 0.42                                        | 28.8               | _                                                                   |

|        | Ghibaudo <sup>7</sup>     | 0.43                                        | 29.0               | _                                                                   |

|        | Hall effect               | 17.2                                        | _                  | 3.1 · 10 <sup>13</sup>                                              |

|        | This work                 | 19.3                                        | 7.1                | 1.8 · 10 <sup>13</sup>                                              |

voltage range of 27 V to 30 V for sample #1 and 50 V to 55 V for sample interface traps has been extracted at  $E_T = E_C - 0.1 \text{ eV}$

quick 3-terminal measurement without the need of special geometries for time-consuming Hall-effect investigations. Hence, this method can be applied to vertical power MOSFET geometries as well, for which Hall-effect analysis is not applicable. Note again that the proposed method benefits from the very specific  $D_{\rm it}$  distribution at 4H-SiC/SiO<sub>2</sub> interfaces.

# Discussion

We present a method that resolves the fundamental problem that in 3-terminal 4H-SiC n-channel MOSFET devices the charge carrier mobility is always underestimated by all available evaluation schemes (e.g., field-effect mobility or effective mobility). This underestimation stems from the negligence of interface traps which are all-important in 4H-SiC. However, their qualitative spectral distribution D<sub>it</sub> is well known. It displays a strong Gaussian distribution near the conduction band edge, responsible for the soft turn-on commonly observed in 4H-SiC MOSFETs. Our model parametrizes this  $D_{it}$  by four parameters, among which two are confined within small boundaries. Using this model and taking quantum confinement into account by a selfconsistent solution of the Schrödinger-Poisson equations, we precisely simulate the transfer characteristics. In turn, by fitting the parameters to measured data, our method allows an accurate determination of charge carrier mobility  $\mu$ , threshold voltage  $V_{\rm T}$ and density of interface traps  $D_{it}$ . This adapted method has been successfully tested on two sets of 4H-SiC Hall-MOSFETs with drastically different D<sub>it</sub> by comparing the results to Hall-effect investigations on the very same devices. We find excellent agreement between the results of these two independent methods, such that we can claim predictive power to our analysis scheme that can, however, be applied to any 3-terminal MOSFET geometry including packaged state-of-the-art power MOSFET devices.

# Methods

**Experimental**. The Hall-MOSFET structures were fabricated using an industrial process. Their channel has a length of 200  $\mu$ m and a width of 32  $\mu$ m. The distance of the 4-point probes for the conductivity measurement is 100  $\mu$ m. The oxide has a thickness of 80 nm and was deposited using a PECVD process with a subsequent annealing step in different atmospheres: nitric oxide for MOSFETs with low  $D_{it}$  and oxygen for MOSFETs with high  $D_{it}$ . The p-well was formed using ion implantation with an aluminum concentration of  $[AI] = 1.5 \cdot 10^{17} \text{ cm}^{-3}$ .

All measurements were performed at room temperature using an Agilent E5270B Precision Measurement Mainframe with Agilent E5287A High Resolution SMUs connected to each sample contact. To reach quasi thermodynamic equilibrium, the transfer characteristics were recorded using a double staircase sweep with a delay that minimized the hysteresis between the two sweep directions. The magnetic field during the Hall measurements was  $\pm 0.65$  T. For the Hall

**Fig. 4** Benchmarking of the adapted method against Hall effect. The results of the Hall-effect investigations are shown as symbols and the simulation using the extracted parameters from the fit of the transfer characteristics is shown as solid lines: **a** charge carrier density  $n_{inv}$ , **b** charge carrier mobility  $\mu$ , and **c** density of interface traps  $D_{it}$ . For both samples, the results of our method agree well with the benchmark data obtained by Hall effect. Especially in the case of sample #2 when a high defect density at the interface is involved this is a substantial improvement compared to conventional mobility extraction schemes out of the transfer characteristics (e.g.,  $\mu_{\text{EF}}^{\text{max}} = 0.4 \text{ cm}^2 \text{V}^{-1} \text{s}^{-1}$ )

measurements as well as for the conductivity measurements *I–V* curves were recorded in the linear regime of the output characteristics. This ensures linearity between the applied current and the measured voltage. Hall constant and conductivity were then calculated from the slopes of the curves. For the evaluation of the inversion charge carrier density a Hall scattering factor of  $r_{\rm H} = 1$  has been assumed. This is in agreement with previous experiments on bulk material, which determined a Hall scattering factor between  $r_{\rm H,bulk} = 0.95$  and  $r_{\rm H,bulk} = 1.00$  for electron transport in 4H-SiC at 300 K<sup>28</sup>.

Simulation of the drain current. For simulating the drain current, the following formula has been used, which includes the conductivity of the channel and the series resistance  $R_{S}$ :

$$I_{\rm D} = \left[ \left( \frac{W}{L} \cdot e \cdot n_{\rm inv} \left( \phi_{\rm S}(V_{\rm G}) \right) \cdot \mu \right)^{-1} + R_{\rm S} \right]^{-1} \cdot V_{\rm D}, \tag{4}$$

The evaluation of Eq. (4) requires the calculation of  $\phi_{\rm S}(V_{\rm G})$  and  $n_{\rm inv}$ .

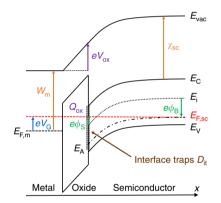

Figure 5 shows a schematic of the band bending and the relevant materials parameters with the applied gate bias  $V_{\rm G} > 0$ .  $W_{\rm m}$  denotes the work function of the gate metal,  $\chi_{\rm sc}$  the electron affinity in the semiconductor,  $E_{\rm F,m}$  and  $E_{\rm F,sc}$  the Fermi energy in the metal and semiconductor, respectively, and  $E_{\rm A}$  the acceptor level. The Fermi potential is defined as  $\phi(x) = (E_{\rm F,sc} - E_{\rm i}(x))/e$  with the intrinsic energy  $E_{\rm i}(x)$  as point of reference. With this at hand, it is easy to derive the following formula for the gate voltage:

$$V_{\rm G}(\phi_{\rm S}) = \frac{W_{\rm m}}{e} - \frac{\chi_{\rm sc}}{e} - \frac{E_{\rm C} - E_{\rm i}}{e} + \phi_{\rm S} + V_{\rm ox}(\phi_{\rm S}). \tag{5}$$

The voltage drop over the oxide capacitor  $V_{\text{ox}}$  can be calculated by using the charge in the semiconductor  $Q_{\text{sc}}$  the charge trapped in interface traps  $Q_{\text{it}}$  and the

Fig. 5 Band schematic of the metal-oxide-semiconductor capacitor

fixed oxide charge  $Q_{ox}$ :

$$V_{\rm ox}(\phi_{\rm S}) = -\frac{Q_{\rm sc}(\phi_{\rm S}) + Q_{\rm it}(\phi_{\rm S}) + Q_{\rm ox}}{C_{\rm ox}}.$$

(6)

The interface trapped charge  $Q_{it}$  is obtained by integration of the parametrized  $D_{it}$  (Eq. 1) over the trap energy. The typical approach is to introduce a neutral level  $E_n$ , where all interface defects above  $E_n$  add a negative charge to the interface when occupied and all interface defects below  $E_n$  add a positive charge to the interface when unoccupied. Those defects are often referred to as acceptor-like and donor-like, respectively.  $Q_{it}$  was calculated as follows:

$$Q_{\rm it}(\phi_{\rm S}) = e \int_{-\infty}^{E_{\rm n}} \frac{D_{\rm it}(E)}{1 + 2 \cdot \exp\left(\frac{-\Delta E(\phi_{\rm S})}{k_{\rm B}T}\right)} dE - e \int_{E_{\rm n}}^{\infty} \frac{D_{\rm it}(E)}{1 + \frac{1}{2} \cdot \exp\left(\frac{\Delta E(\phi_{\rm S})}{k_{\rm B}T}\right)} dE.$$

(7)

For the multiplicity of the states involved, we opted for a consistent description for both cases. Since the exact degeneracy of the states is not known, we assumed a value frequently used for donor-like defects for all interface traps. This seems natural because the important interface traps for the performance of the devices are energetically close to the conduction band edge. It leads to the factor 2 in the case of unoccupation and to the factor 1/2 in the case of occupation in Eq. (7). Note that the evaluation results remain essentially unaffected upon a different choice of multiplicities. For the calculation of  $Q_{sc}(\phi_S)$  see the next paragraph.  $\phi_S(V_G)$  is obtained by numerical inversion of Eq. (5).

To calculate  $n(\phi_S)$  and  $Q_{sc}(\phi_S)$  two methods were used. The first one is the charge sheet model for silicon carbide proposed by Arnold<sup>20</sup>. It's a semiclassical model, where both relations are calculated by integration over the space charge region. The second method used employs the Schrödinger–Poisson solver of Snider et al.<sup>21,22</sup> to simulate the band bending and the ground states of the 2D sub-bands in the inversion channel. For the calculation of the total charge in the semiconductor  $Q_{sc}(\phi_S)$  the electron charge density, the hole charge density and the charge density of ionized dopants are integrated over the space charge region. The surface Fermi potential  $\phi_S$  is given by  $(E_F - E_i)/e$  at the interface. The inversion channel.

#### Evaluation of the density of interface traps from Hall-effect investigations.

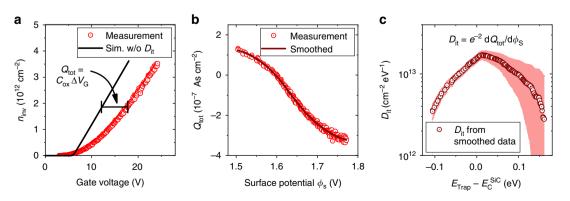

Figure 6 shows the evaluation of Hall-effect measurements obtained on sample #1 as example. In Fig. 6a the measured inversion charge carrier density  $n_{inv}$  is plotted and compared to the SPS-simulated  $n_{inv}$  for an ideal MOSFET with identical parameters, but without fixed oxide charge  $Q_{ox}$  and interface traps  $D_{it}$  (black solid curve). A point-by-point analysis of the gate voltage difference  $\Delta V_G = V_{G,ideal} - V_G$  delivers the total trapped charge  $Q_{tot}$  as a function of  $n_{inv}$  with

$$Q_{\rm tot} = Q_{\rm ox} + Q_{\rm it}(\phi_{\rm S}) = C_{\rm ox} \cdot \Delta V_{\rm G}.$$

(8)

The surface Fermi potential  $\phi_{\rm S}$  is calculated by inverting the result for  $n_{\rm inv}(\phi_{\rm S})$  from the Schrödinger–Poisson solver discussed in the previous section. While  $Q_{\rm ox}$  is independent of the surface Fermi potential  $\phi_{\rm S}$ , the interface trapped charge  $Q_{\rm it}$

**Fig. 6** Evaluation of the density of interface traps  $D_{it}$  from Hall-effect measurements. The  $D_{it}$  in **c** is derived from the deviations of the Hall-effect data from the simulation assuming no  $D_{it}$ . The measurement error can be read off the weak scatter of the measurement data in **a** and **b**, resulting in the shaded error margin in **c**

varies with  $\phi_{\rm S}$ . This gives access to the density of interface traps (Fig. 6c):

$$D_{\rm it} = \frac{1}{e^2} \cdot \left| \frac{\mathrm{d}Q_{\rm it}}{\mathrm{d}\phi_{\rm S}} \right| = \frac{1}{e^2} \cdot \left| \frac{\mathrm{d}Q_{\rm tot}}{\mathrm{d}\phi_{\rm S}} \right|. \tag{9}$$

The surface Fermi potential is linked to the energy position of traps in the bandgap by  $\phi_{\rm S} = (E_{\rm F} - E_{\rm i}^{\rm interface})/e$  with  $E_{\rm it} \approx E_{\rm F}$ .

## Data availability

The data that support the findings of this study are available from the corresponding author upon request.

Received: 11 July 2018 Accepted: 28 November 2018 Published online: 10 January 2019

## References

- She, X., Huang, A., Lucia, O. & Ozpineci, B. Review of silicon carbide power devices and their applications. *IEEE Trans. Ind. Electron.* 64, 8193–8205 (2017).

- Wang, G. et al. Performance comparison of 1200V 100A SiC MOSFET and 1200V 100A silicon IGBT. 2013 IEEE Energy Conversion Congress and Exposition, ECCE 2013, 15–19 Sept 3230–3234 (2013).

- Li, H.-f, Dimitrijev, S., Harrison, H. B. & Sweatman, D. Interfacial characteristics of N2O and NO nitrided SiO<sub>2</sub> grown on SiC by rapid thermal processing. *Appl. Phys. Lett.* **70**, 2028–2030 (1997).

- Chung, G. Y. et al. Effect of nitric oxide annealing on the interface trap densities near the band edges in the 4H polytype of silicon carbide. *Appl. Phys. Lett.* 76, 1713–1715 (2000).

- Moghadam, H. A., Dimitrijev, S., Han, J., Haasmann, D. & Aminbeidokhti, A. Transient-current method for measurement of active near-interface oxide traps in 4H-SiC MOS capacitors and MOSFETs. *IEEE Trans. Electron Devices* 62, 2670–2674 (2015).

- Hatakeyama, T. et al. Characterization of traps at nitrided SiO<sub>2</sub>/SiC interfaces near the conduction band edge by using Hall effect measurements. *Appl. Phys. Express* 10, 046601 (2017).

- Ghibaudo, G. New method for the extraction of MOSFET parameters. Electron. Lett. 24, 543–545 (1988).

- Schroder, D. K. Semiconductor Material and Device Characterization 3rd edn (John Wiley & Sons, Hoboken, NJ, 2005).

- Saks, N. S. & Agarwal, A. K. Hall mobility and free electron density at the SiC/ SiO<sub>2</sub> interface in 4Hâ€"SiC. Appl. Phys. Lett. 77, 3281–3283 (2000).

- Afanasev, V. V., Bassler, M., Pensl, G. & Schulz, M. Intrinsic SiC/SiO<sub>2</sub> Interface States. *Phys. Status Solidi (a)* 162, 321–337 (1997).

- Noborio, M., Suda, J., Beljakowa, S., Krieger, M. & Kimoto, T. 4H-SiC MISFETs with nitrogen-containing insulators. *Phys. Status Solidi (a)* 206, 2374–2390 (2009).

- Amini Moghadam, H., Dimitrijev, S., Han, J. & Haasmann, D. Active defects in MOS devices on 4H-SiC: A critical review. *Microelectron. Reliab.* 60, 1–9 (2016).

- Knaup, J. M. et al. Theoretical study of the mechanism of dry oxidation of 4H-SiC. Phys. Rev. B 71, 1–9 (2005).

- Afanas'ev, V. V. & Stesmans, A. Interfacial defects in SiO<sub>2</sub> revealed by photon stimulated tunneling of electrons. *Phys. Rev. Lett.* 78, 2437–2440 (1997).

- Haasmann, D. & Dimitrijev, S. Energy position of the active near-interface traps in metal-oxide- semiconductor field-effect transistors on 4H-SiC. *Appl. Phys. Lett.* 103, 1–4 (2013).

- Hauck, M. et al. Quantitative investigation of near interface traps in 4H-SiC MOSFETs via drain current deep level transient spectroscopy. *Mater. Sci. Forum* 897, 111–114 (2017).

- Pande, P. et al. Direct measurement of active near-interface traps in the strong-accumulation region of 4H-SiC MOS capacitors. *IEEE J. Electron Devices Soc.* 6, 468–474 (2018).

- El-Sayed, A.-M., Watkins, M. B., Afanas'ev, V. V. & Shluger, A. L. Nature of intrinsic and extrinsic electron trapping in SiO<sub>2</sub>. *Phys. Rev. B* 89, 125201 (2014).

- Devynck, F., Alkauskas, A., Broqvist, P. & Pasquarello, A. Charge transition levels of carbon-, oxygen-, and hydrogen-related defects at the SiC/ SiO<sub>2</sub>interface through hybrid functionals. *Phys. Rev. B* 84, 1–18 (2011).

- Arnold, E. Charge-sheet model for silicon carbide inversion layers. *IEEE Trans. Electron Devices* 46, 497–503 (1999).

- Tan, I. H., Snider, G. L., Chang, L. D. & Hu, E. L. A self-consistent solution of Schrödinger-Poisson equations using a nonuniform mesh. J. Appl. Phys. 68, 4071–4076 (1990).

- Snider, G. L., Tan, I. & Hu, E. L. Electron states in mesa-etched one dimensional quantum well wires. J. Appl. Phys. 68, 2849–2853 (1990).

- Powell, S. K. et al. Physics-based numerical modeling and characterization of 6H-silicon-carbide metal-oxide-semiconductor field-effect transistors. J. Appl. Phys. 92, 4053–4061 (2002).

- Tilak, V., Matocha, K. & Dunne, G. Electron-scattering mechanisms in heavily doped silicon carbide MOSFET inversion layers. *IEEE Trans. Electron Devices* 54, 2823–2829 (2007).

- Tilak, V., Matocha, K., Dunne, G., Allerstam, F. & Sveinbjornsson, E. Ö. Trap and inversion layer mobility characterization using Hall effect in silicon carbide-based MOSFETs with gate oxides grown by sodium enhanced oxidation. *IEEE Trans. Electron Devices* 56, 162–169 (2009).

- Saks, N. S., Ancona, M. G. & Rendell, R. W. Using the Hall effect to measure interface trap densities in silicon carbide and silicon metal-oxidesemiconductor devices. *Appl. Phys. Lett.* **80**, 3219–3221 (2002).

- Schöner, A., Krieger, M., Pensl, G., Abe, M. & Nagasawa, H. Fabrication and characterization of 3C-SiC-based MOSFETs. *Chem. Vap. Depos.* 12, 523–530 (2006).

- Schmid, F., Krieger, M., Laube, M., Pensl, G. & Wagner, G. in *Silicon Carbide* -*Recent Major Advances* (eds Choyke, W. J., Matsunami, H., & Pensl, G.) 517–536 (Springer, Berlin, 2004).

# Author contributions

M.H., H.B.W., and M.K. designed research; M.H. J.L., G.P., H.B.W., and M.K. performed research; G.P. provided samples; M.H. analyzed data; M.H., H.B.W., and M.K. wrote the manuscript.

## Additional information

Competing interests: The authors declare no competing interests.

Reprints and permission information is available online at http://npg.nature.com/ reprintsandpermissions/

**Publisher's note:** Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

**Open Access** This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this license, visit http://creativecommons.org/ licenses/by/4.0/.

© The Author(s) 2019