Abstract

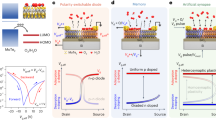

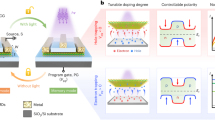

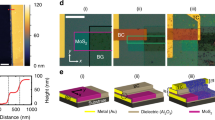

Reconfigurable logic and neuromorphic devices are crucial for the development of high-performance computing. However, creating reconfigurable devices based on conventional complementary metal–oxide–semiconductor technology is challenging due to the limited field-effect characteristics of the fundamental silicon devices. Here we show that a homojunction device made from two-dimensional tungsten diselenide can exhibit diverse field-effect characteristics controlled by polarity combinations of the gate and drain voltage inputs. These electrically tunable devices can achieve reconfigurable multifunctional logic and neuromorphic capabilities. With the same logic circuit, we demonstrate a 2:1 multiplexer, D-latch and 1-bit full adder and subtractor. These functions exhibit a full-swing output voltage and the same supply and signal voltage, which suggests that the devices could be cascaded to create complex circuits. We also show that synaptic circuits based on only three homojunction devices can achieve reconfigurable spiking-timing-dependent plasticity and pulse-tunable synaptic potentiation or depression characteristics; the same function using complementary metal–oxide–semiconductor devices would require more than ten transistors.

This is a preview of subscription content, access via your institution

Access options

Access Nature and 54 other Nature Portfolio journals

Get Nature+, our best-value online-access subscription

$29.99 / 30 days

cancel any time

Subscribe to this journal

Receive 12 digital issues and online access to articles

$119.00 per year

only $9.92 per issue

Buy this article

- Purchase on Springer Link

- Instant access to full article PDF

Prices may be subject to local taxes which are calculated during checkout

Similar content being viewed by others

Data availability

The data that support the plots within this manuscript and other findings of this study are available from the corresponding author upon reasonable request.

References

Qiu, C. et al. Dirac-source field-effect transistors as energy-efficient, high-performance electronic switches. Science 361, 387–392 (2018).

Li, D. et al. Two-dimensional non-volatile programmable p–n junctions. Nat. Nanotechnol. 12, 901–906 (2017).

Huang, M. et al. Multifunctional high-performance van der Waals heterostructures. Nat. Nanotechnol. 12, 1148–1154 (2017).

Cheng, R. et al. High-performance, multifunctional devices based on asymmetric van der Waals heterostructures. Nat. Electron. 1, 356–361 (2018).

Yang, H. et al. Graphene barristor, a triode device with a gate-controlled Schottky barrier. Science 336, 1140–1143 (2012).

Liu, C. et al. A semi-floating gate memory based on van der Waals heterostructures for quasi-non-volatile applications. Nat. Nanotechnol. 13, 404–410 (2018).

Resta, G. V. et al. Towards high-performance polarity-controllable FETs with 2D materials. In 2018 Design, Automation & Test in Europe Conference & Exhibition (DATE) 637–641 (IEEE, 2018).

Pang, C. & Chen, Z. First demonstration of WSe2 CMOS inverter with modulable noise margin by electrostatic doping. In 2018 76th Device Research Conference (DRC) 1–2 (IEEE, 2018).

Pang, C., Thakuria, N., Gupta, S. K. & Chen, Z. First demonstration of WSe2 based CMOS-SRAM. In 2018 IEEE Int. Electron Devices Meeting (IEDM) 22.2.1–22.2.4 (IEEE, 2018).

Resta, G. V. et al. Doping-free complementary logic gates enabled by two-dimensional polarity-controllable transistors. ACS Nano 12, 7039–7047 (2018).

Liu, C. et al. Small footprint transistor architecture for photoswitching logic and in situ memory. Nat. Nanotechnol. 14, 662–667 (2019).

International Technology Roadmap for Semiconductors 2.0 2015 Edition—Beyond CMOS (IEEE, 2018) https://www.semiconductors.org/wp-content/uploads/2018/06/6_2015-ITRS-2.0-Beyond-CMOS.pdf

Orji, N. G. et al. Metrology for the next generation of semiconductor devices. Nat. Electron. 1, 532–547 (2018).

Gaillardon, P., Tang, X., Kim, G. & De Micheli, G. A novel FPGA architecture based on ultrafine grain reconfigurable logic cells. IEEE Trans. Very Large Scale Integr. VLSI Syst. 23, 2187–2197 (2015).

Trommer, J., Heinzig, A., Slesazeck, S., Mikolajick, T. & Weber, W. M. Elementary aspects for circuit implementation of reconfigurable nanowire transistors. IEEE Electron Device Lett. 35, 141–143 (2014).

Liu, Y. et al. Ambipolar barristors for reconfigurable logic circuits. Nano Lett. 17, 1448–1454 (2017).

Raitza, M. et al. Exploiting transistor-level reconfiguration to optimize combinational circuits. In Proc. Conference on Design, Automation & Test in Europe 338–343 (European Design and Automation Association, 2017).

Ben-Jamaa, M. H., Mohanram, K. & De Micheli, G. An efficient gate library for ambipolar CNTFET logic. IEEE Trans. Comput. Aided Des. Integr. Circuits Syst. 30, 242–255 (2011).

Yan, H. et al. Programmable nanowire circuits for nanoprocessors. Nature 470, 240–244 (2011).

Chhowalla, M., Jena, D. & Zhang, H. Two-dimensional semiconductors for transistors. Nat. Rev. Mater. 1, 16052 (2016).

Jariwala, D., Sangwan, V. K., Lauhon, L. J., Marks, T. J. & Hersam, M. C. Emerging device applications for semiconducting two-dimensional transition metal dichalcogenides. ACS Nano 8, 1102–1120 (2014).

Liu, Y. et al. Van der Waals heterostructures and devices. Nat. Rev. Mater. 1, 16042 (2016).

Yu, W. J. et al. Vertically stacked multi-heterostructures of layered materials for logic transistors and complementary inverters. Nat. Mater. 12, 246–252 (2013).

Wang, Y. et al. Negative photoconductance in van der Waals heterostructure-based floating gate phototransistor. ACS Nano 12, 9513–9520 (2018).

Lee, C. et al. Atomically thin p–n junctions with van der Waals heterointerfaces. Nat. Nanotechnol. 9, 676–681 (2014).

Wang, M. et al. Robust memristors based on layered two-dimensional materials. Nat. Electron. 1, 130–136 (2018).

Pospischil, A., Furchi, M. M. & Mueller, T. Solar-energy conversion and light emission in an atomic monolayer p–n diode. Nat. Nanotechnol. 9, 257–261 (2014).

Baugher, B. W., Churchill, H. O., Yang, Y. & Jarillo-Herrero, P. Optoelectronic devices based on electrically tunable p–n diodes in a monolayer dichalcogenide. Nat. Nanotechnol. 9, 262–267 (2014).

Liu, T. et al. Nonvolatile and programmable photodoping in MoTe2 for photoresist-free complementary electronic devices. Adv. Mater. 30, 1804470 (2018).

Ross, J. S. et al. Electrically tunable excitonic light-emitting diodes based on monolayer WSe2 p–n junctions. Nat. Nanotechnol. 9, 268–272 (2014).

Das, S. & Appenzeller, J. WSe2 field effect transistors with enhanced ambipolar characteristics. Appl. Phys. Lett. 103, 103501 (2013).

Liu, W. et al. Role of metal contacts in designing high-performance monolayer n-type WSe2 field effect transistors. Nano Lett. 13, 1983–1990 (2013).

Fang, H. et al. High-performance single layered WSe2 p-FETs with chemically doped contacts. Nano Lett. 12, 3788–3792 (2012).

Allain, A. & Kis, A. Electron and hole mobilities in single-layer WSe2. ACS Nano 8, 7180–7185 (2014).

Yu, L. et al. High-performance WSe2 complementary metal oxide semiconductor technology and integrated circuits. Nano Lett. 15, 4928–4934 (2015).

Pu, J. et al. Highly flexible and high-performance complementary inverters of large-area transition metal dichalcogenide monolayers. Adv. Mater. 28, 4111–4119 (2016).

Yu, L. et al. Design, modeling, and fabrication of chemical vapor deposition grown MoS2 circuits with E-mode FETs for large-area electronics. Nano Lett. 16, 6349–6356 (2016).

Wachter, S., Polyushkin, D. K., Bethge, O. & Mueller, T. A microprocessor based on a two-dimensional semiconductor. Nat. Commun. 8, 14948 (2017).

Dathbun, A. et al. Large-area CVD-grown sub-2 V ReS2 transistors and logic gates. Nano Lett. 17, 2999–3005 (2017).

Wang, H. et al. Integrated circuits based on bilayer MoS2 transistors. Nano Lett. 12, 4674–4680 (2012).

Prezioso, M. et al. Training and operation of an integrated neuromorphic network based on metal-oxide memristors. Nature 521, 61–64 (2015).

Tuma, T., Pantazi, A., Le Gallo, M., Sebastian, A. & Eleftheriou, E. Stochastic phase-change neurons. Nat. Nanotechnol. 11, 693–699 (2016).

Jo, S. H. et al. Nanoscale memristor device as synapse in neuromorphic systems. Nano Lett. 10, 1297–1301 (2010).

Kuzum, D., Jeyasingh, R. G., Lee, B. & Wong, H. P. Nanoelectronic programmable synapses based on phase change materials for brain-inspired computing. Nano Lett. 12, 2179–2186 (2011).

Wang, Z. et al. Memristors with diffusive dynamics as synaptic emulators for neuromorphic computing. Nat. Mater. 16, 101–108 (2017).

Shi, Y. et al. Electronic synapses made of layered two-dimensional materials. Nat. Electron. 1, 458–465 (2018).

Sangwan, V. K. et al. Multi-terminal memtransistors from polycrystalline monolayer molybdenum disulfide. Nature 554, 500–504 (2018).

Zhu, X., Li, D., Liang, X. & Lu, W. D. Ionic modulation and ionic coupling effects in MoS2 devices for neuromorphic computing. Nat. Mater. 18, 141–148 (2019).

Zhu, J. et al. Ion gated synaptic transistors based on 2D van der Waals crystals with tunable diffusive dynamics. Adv. Mater. 30, 1800195 (2018).

Zhu, L. Q., Wan, C. J., Guo, L. Q., Shi, Y. & Wan, Q. Artificial synapse network on inorganic proton conductor for neuromorphic systems. Nat. Commun. 5, 3158 (2014).

Tian, H. et al. Anisotropic black phosphorus synaptic device for neuromorphic applications. Adv. Mater. 28, 4991–4997 (2016).

Wang, Z. et al. Fully memristive neural networks for pattern classification with unsupervised learning. Nat. Electron. 1, 137–145 (2018).

Indiveri, G., Chicca, E. & Douglas, R. A VLSI array of low-power spiking neurons and bistable synapses with spike-timing dependent plasticity. IEEE Trans. Neural Netw. 17, 211–221 (2006).

Tian, H. et al. Emulating bilingual synaptic response using a junction-based artificial synaptic device. ACS Nano 11, 7156–7163 (2017).

Pan, C. et al. Analog circuit applications based on ambipolar graphene/MoTe2 vertical transistors. Adv. Electron. Mater. 4, 1700662 (2018).

Acknowledgements

This work was supported in part by the National Natural Science Foundation of China (61625402, 61921005 and 61974176), and the Collaborative Innovation Center of Advanced Microstructures and Natural Science Foundation of Jiangsu Province (BK20180330), Fundamental Research Funds for the Central Universities (020414380084). K.W. and T.T. acknowledge support from the Elemental Strategy Initiative conducted by MEXT, Japan, A3 Foresight by JSPS and a CREST (JPMJCR15F3) from JST. The authors thank S. Liu and Q. Qian from Southeast University, and L. Shao from Nanjing University for their helpful discussions.

Author information

Authors and Affiliations

Contributions

F.M., S.-J.L. and C.P. conceived the idea and designed the experiments. F.M. and S.-J.L. supervised the whole project. C.P. fabricated the ETH devices and performed all the experiments. Chenyu Wang, Y.W., T.C. and P.W. assisted in the device fabrication and circuit measurements. C.P., Chenyu Wang, S.-J.L. and F.M. analysed the experimental data. K.W. and T.T. prepared the h-BN samples. Cong Wang, S.W., A.G., B.C. and E.L. contributed to the discussions. C.P., S.-J.L. and F.M. co-wrote the manuscript with inputs from all the co-authors.

Corresponding authors

Ethics declarations

Competing interests

The authors declare no competing interests.

Additional information

Publisher’s note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Supplementary information

Supplementary Information

Supplementary Figs. 1–11 and refs. 1–12.

Rights and permissions

About this article

Cite this article

Pan, C., Wang, CY., Liang, SJ. et al. Reconfigurable logic and neuromorphic circuits based on electrically tunable two-dimensional homojunctions. Nat Electron 3, 383–390 (2020). https://doi.org/10.1038/s41928-020-0433-9

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1038/s41928-020-0433-9

This article is cited by

-

In-sensor dynamic computing for intelligent machine vision

Nature Electronics (2024)

-

Homojunction-loaded inverters based on self-biased molybdenum disulfide transistors for sub-picowatt computing

Nature Electronics (2024)

-

Reconfigurable logic and in-sensor encryption operations in an asymmetrically tunable van der Waals heterostructure

Nano Research (2024)

-

Realization of flexible in-memory computing in a van der Waals ferroelectric heterostructure tri-gate transistor

Nano Research (2024)

-

A scalable solution recipe for a Ag-based neuromorphic device

Discover Nano (2023)