Abstract

In the past five decades, the semiconductor industry has gone through two distinct eras of scaling: the geometric (or classical) scaling era and the equivalent (or effective) scaling era. As transistor and memory features approach 10 nanometres, it is apparent that room for further scaling in the horizontal direction is running out. In addition, the rise of data abundant computing is exacerbating the interconnect bottleneck that exists in conventional computing architecture between the compute cores and the memory blocks. Here we argue that electronics is poised to enter a new, third era of scaling — hyper-scaling — in which resources are added when needed to meet the demands of data abundant workloads. This era will be driven by advances in beyond-Boltzmann transistors, embedded non-volatile memories, monolithic three-dimensional integration and heterogeneous integration techniques.

This is a preview of subscription content, access via your institution

Access options

Access Nature and 54 other Nature Portfolio journals

Get Nature+, our best-value online-access subscription

$29.99 / 30 days

cancel any time

Subscribe to this journal

Receive 12 digital issues and online access to articles

$119.00 per year

only $9.92 per issue

Buy this article

- Purchase on Springer Link

- Instant access to full article PDF

Prices may be subject to local taxes which are calculated during checkout

Similar content being viewed by others

Change history

22 August 2018

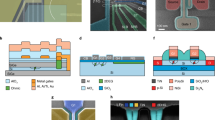

In the version of this Perspective originally published, in the key for Fig. 2d the labels for the light-blue and dark-blue lines were mistakenly swapped. The light-blue line should have been labelled ‘Tunnel FET’ and the dark-blue line should have been labelled ‘Negative capacitance FET’. This has now been corrected.

References

Moore, G. E. Cramming more components onto integrated circuits. Electronics 38, 114–117 (1965).

Dennard, R. H. et al. Design of ion-implanted MOSFET’s with very small physical dimensions. IEEE J. Solid-State Circuits 9, 256–268 (1974).

Thompson, S. E. et al. A logic nanotechnology featuring strained-silicon. IEEE Electron Dev. Lett. 25, 191–193 (2004).

Chau, R. et al. High-κ metal-gate stack and its MOSFET characteristics. IEEE Electron Dev. Lett. 25, 408–410 (2004).

Doyle, B. S. et al. High performance fully-depleted tri-gate CMOS transistors. IEEE Electron Dev. Lett. 24, 263–265 (2003).

Sherazi, S. M. Y. et al. Low track height standard cell design in iN7 using scaling boosters. Proc. SPIE https://doi.org/10.1117/12.2257658 (2017).

Pillarisetty, R. Academic and industry research progress in germanium nanodevices. Nature 479, 324–328 (2011).

del Alamo, J. Nanometer-scale electronics with III-V compound semiconductors. Nature 479, 317–323 (2011).

Cao, Q., Tersoff, J., Farmer, D. B., Zhu, Y. & Han, S. J. Carbon nanotube transistors scaled to a 40-nanometer footprint. Science 356, 1369–1372 (2017).

Salahuddin, S. & Datta, S. Interacting systems for self-correcting low power switching. Appl. Phys. Lett. 90, 093503 (2007).

Salahuddin, S. & Datta, S. Use of negative capacitance to provide voltage amplification for low power nanoscale devices. Nano Lett. 8, 405–410 (2008).

Khan, A. I. et al. Experimental evidence of ferroelectric negative capacitance in nanoscale heterostructures. Appl. Phys. Lett. 99, 113501 (2011).

Krivokapic, Z. et al. 14 nm ferroelectric FinFET technology with steep subthreshold slope for ultra-low power applications. 2017 IEEE Int. Electron Dev. Meet. https://doi.org/10.1109/IEDM.2017.8268393 (2017).

Freeman, E. et al. Nanoscale structural evolution of electrically driven insulator to metal transition in vanadium dioxide. Appl. Phys. Lett. 103, 263109 (2013).

Shukla, N. et al. A steep-slope transistor based on abrupt electronic phase transition. Nat. Commun. 6, 7812 (2015).

Verhulst, A. S. et al. Complementary silicon-based heterostructure tunnel-FETs with high tunnel rates. IEEE Electron Dev. Lett. 29, 1398–1401 (2008).

Kao, K. H. et al. Direct and indirect band-to-band tunneling in germanium-based TFETs. IEEE Trans. Electron Dev. 59, 292–301 (2012).

Braucks, C. S. et al. Fabrication, characterization, and analysis of Ge/GeSn heterojunction p-type tunnel transistors. IEEE Trans. Electron Dev. 64, 4354–4362 (2017).

Mookerjea, S., Mohata, D., Mayer, T., Narayanan, V. & Datta, S. Temperature-dependent I–V characteristics of a vertical In0.53Ga0.47As tunnel FET. IEEE Electron Dev. Lett. 31, 564–566 (2010).

Mohata, D. et al. Barrier-engineered arsenide–antimonide heterojunction tunnel FETs with enhanced drive current. IEEE Electron Dev. Lett. 33, 1568–1570 (2012).

Rajamohanan, B. et al. 0.5 V supply voltage operation of In0.65Ga0.35As/GaAs0.4Sb0.6 tunnel FET. IEEE Electron Dev. Lett. 36, 20–22 (2015).

Swaminathan, K. et al. Steep slope devices: from dark to dim silicon. IEEE Micro 22, 50–59 (2013).

Krizhevsky, A., Sutskever, I. & Hinton, G. E. ImageNet classification with deep convolutional neural networks. 2012 Proc. Adv. Neural Inf. Process. Syst. (NIPS) 1097–1105 (2012).

Graves, A., Mohamed, A. R., Hinton, G. E. Speech recognition with deep recurrent neural networks. 2013 Proc. IEEE Int. Conf. Acoust. Speech Signal Process. https://doi.org/10.1109/ICASSP.2013.6638947 (2013).

Aly, M. et al. Energy-efficient abundant-data computing: the N3XT 1,000X. IEEE Computer 48, 24–33 (2015).

Desoli, G. et al. A 2.9 TOPS/W deep convolutional neural network SoC in FD-SOI 28nm for intelligent embedded systems. 2017 IEEE Int. Solid-State Circuits Conf. (ISSCC) https://doi.org/10.1109/ISSCC.2017.7870349 (2017).

Miura, N., Kasuga, K., Saito, M. & Kuroda, T. An 8Tb/s 1pJ/b 0.8mm2/Tb/s QDR inductive coupling interface between 65nm CMOS GPU and 0.1 μm DRAM. 2010 IEEE Int. Solid-State Circuits Conf. (ISSCC) (ISSCC) https://doi.org/10.1109/ISSCC.2010.5433909 (2010).

Karl, E. et al. 4.6GHz 162 Mb SRAM design in 22nm tri-gate CMOS technology with integrated active VMIN-enhancing assist circuitry. 2012 IEEE Int. Solid-State Circuits Conf. https://doi.org/10.1109/ISSCC.2012.6176988 (2012).

Hamzaoglu, F. et al. A 1Gb 2GHz embedded DRAM in 22nm tri-gate CMOS technology. 2014 IEEE Int. Solid-State Circuits Conf. Dig. Tech. Papers (ISSCC) https://doi.org/10.1109/ISSCC.2014.6757412 (2014).

Taito, Y. et al. A 28nm embedded SG-MONOS flash macro for automotive achieving 200MHz read operation and 2.0MB/s write throughput at Ti of 170 °C. 2015 IEEE Int. Solid-State Circuits Conf. Dig. Tech. Papers (ISSCC) https://doi.org/10.1109/ISSCC.2015.7062961 (2015).

Dong, Q. et al. A 1Mb embedded NOR flash memory with 39 μW program power for mm-scale high temperature sensor nodes. 2017 IEEE Int. Solid-State Circuits Conf. (ISSCC) https://doi.org/10.1109/ISSCC.2017.7870329 (2017).

Noguchi, H. et al. A 3.3ns access time 71.2μW/MHz 1Mb embedded STT-MRAM using physically eliminated read-disturb scheme and normally-off memory architecture. 2015 IEEE Int. Solid-State Circuits Conf. (ISSCC) https://doi.org/10.1109/ISSCC.2015.7062963 (2015).

Dong, Q. et al. A 1Mb 28nm STT-MRAM with 2.8ns read access time at 1.2V VDD using single-cap offset-cancelled sense amplifier and in-situ self-write-termination. 2018 IEEE Int. Solid-State Circuits Conf. (ISSCC) https://doi.org/10.1109/ISSCC.2018.8310393 (2018).

Takashima, D. Overview of FeRAMs: trends and perspectives. 2011 Non-Volatile Memory Technol. Symp. Proc. https://doi.org/10.1109/NVMTS.2011.6137107 (2011).

Dünkel, S. et al. A FeFET based super-low-power ultra-fast embedded NVM technology for 22nm FDSOI and beyond. 2017 IEEE Int. Electron Device Meeting (IEDM) https://doi.org/10.1109/IEDM.2017.8268425 (2017).

Ni, K. et al. Critical role of interlayer in Hf0.5Zr0.5O2 FeFet nonvolatile memory performance. IEEE Trans. Electron Dev. 65, 2461–2469 (2018).

Annunziata, R. et al. Phase change memory technology for embedded non-volatile memory applications for 90nm and beyond. 2009 IEEE Int. Electron Device Meeting (IEDM) https://doi.org/10.1109/IEDM.2009.5424413 (2009).

Choi, Y. et al. A 20nm 1.8V 8Gb PRAM with 40 MB/s program bandwidth. 2012 IEEE Int. Solid-State Circuits Conf. https://doi.org/10.1109/ISSCC.2012.6176872 (2012).

Govoreanu, B. et al. 10×10 nm2 Hf/HfOx crossbar resistive RAM with excellent performance, reliability and low-energy operation. 2011 IEEE Int. Electron Device Meeting https://doi.org/10.1109/IEDM.2011.6131652 (2011).

Luo, Q. et al. 8-layers 3D vertical RRAM with excellent scalability towards storage class memory applications. 2017 IEEE Int. Electron Dev. Meet. (IEDM) https://doi.org/10.1109/IEDM.2017.8268315 (2017).

Jo, S. H., Kumar, T., Narayanan, S., Lu, W. D. & Nazarian, H. 3D-stackable crossbar resistive memory based on field assisted superlinear threshold selector. 2014 IEEE Int. Electron Dev. Meet. https://doi.org/10.1109/IEDM.2014.7046999 (2014).

Hautier, G., Miglio, A., Ceder, G., Rignanese, G. M. & Gonze, X. Identification and design principles of low hole effective mass p-type transparent conducting oxides. Nat. Commun. 4, 2292 (2013).

Shulaker, M. M. et al. Three-dimensional integration of nanotechnologies for computing and data storage on a single chip. Nature 547, 74–78 (2017).

Batude, P. et al. Advances, challenges and opportunities in 3D CMOS sequential integration. 2011 Int. Electron Dev. Meet. https://doi.org/10.1109/IEDM.2011.6131506 (2011).

Chen, S. et al. Raman measurements of thermal transport in suspended monolayer graphene of variable sizes in vacuum and gaseous environments. ACS Nano 5, 321 (2011).

Ghosh, S. Dimensional crossover of thermal transport in few-layer graphene. Nat. Mater. 9, 555 (2010).

Doany, F. E. et al. Terabit/s-class optical PCB links incorporating 360-Gb/s bidirectional 850 nm parallel optical transceivers. J. Light Wave Technol. 30, 560–571 (2011).

Kim, N., Wu, D., Kim, D. W., Rahman, A. & Wu, P. Interposer design optimization for high frequency signal transmission in passive and active interposer using through silicon via (TSV). 2011 IEEE 61st Electronic Components Technol. Conf. (ECTC) https://doi.org/10.1109/ECTC.2011.5898657 (2011).

Ron, Ho,R. et al. Silicon photonic interconnects for large-scale computer systems. IEEE Micro 33, 68–78 (2013).

Bajwa, A. A. et al. Heterogeneous integration at fine pitch (≤ 10 μm) using thermal compression bonding. 2017 IEEE 67th Elec. Components Tech. Conf. (ECTC) https://doi.org/10.1109/ECTC.2017.240 (2017).

Acknowledgements

S.S., K.N. and S.D. acknowledge funding from ASCENT, one of six centres in JUMP (Joint University Microelectronics Program), a Semiconductor Research Corporation (S.R.C.) program sponsored by DARPA.

Author information

Authors and Affiliations

Contributions

S.S. and S.D. conceived the project, carried out the discussions and wrote the manuscripts. K.N. prepared the figures and co-wrote the section on memory benchmarking.

Corresponding authors

Ethics declarations

Competing interests

The authors declare no competing interests.

Additional information

Publisher’s note: Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Salahuddin, S., Ni, K. & Datta, S. The era of hyper-scaling in electronics. Nat Electron 1, 442–450 (2018). https://doi.org/10.1038/s41928-018-0117-x

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1038/s41928-018-0117-x

This article is cited by

-

High-speed emerging memories for AI hardware accelerators

Nature Reviews Electrical Engineering (2024)

-

Ferroelectric compute-in-memory annealer for combinatorial optimization problems

Nature Communications (2024)

-

Ferroelastically protected reversible orthorhombic to monoclinic-like phase transition in ZrO2 nanocrystals

Nature Materials (2024)

-

Steep-slope vertical-transport transistors built from sub-5 nm Thin van der Waals heterostructures

Nature Communications (2024)

-

Machine learning-powered compact modeling of stochastic electronic devices using mixture density networks

Scientific Reports (2024)