Abstract

Two-dimensional molybdenum disulfide (MoS2) has substantial potential as a semiconducting material for devices. However, it is commonly prepared by mechanical exfoliation, which limits flake size to only a few micrometers, which is not sufficient for processes such as photolithography and circuit patterning. Chemical vapor deposition (CVD) has thus become a mainstream fabrication technique to achieve large-area MoS2. However, reports of conventional photolithographic patterning of large-area 2D MoS2-based devices with high mobilities and low switching voltages are rare. Here we fabricate CVD-grown large-area MoS2 field-effect transistors (FETs) by photolithography and demonstrate their potential as switching and driving FETs for pixels in analog organic light-emitting diode (OLED) displays. We spin-coat an ultrathin hydrophobic polystyrene layer on an Al2O3 dielectric, so that the uniformity of threshold voltage (Vth) of the FETs might be improved. Our MoS2 FETs show a high linear mobility of approximately 10 cm2 V−1 s−1, due to a large grain size around 60 μm, and a high ON/OFF current ratio of 108. Dynamic switching of blue and green OLED pixels is shown at ~5 V, demonstrating their application potential.

Similar content being viewed by others

Introduction

Molybdenum disulfide (MoS2), a two-dimensional (2D) transition metal dichalcogenide (TMD) semiconductor has attracted much attention from many researchers owing to its interesting physical properties and potentials for future nanoscale electronics.1,2,3,4 Like graphene, those 2D semiconductors are easily formed by mechanical exfoliation using scotch tapes in general, while it also displays high ON/OFF current ratio and good subthreshold swing in a field-effect transistor (FET) form with n-type conduction unlike graphene, which shows no bandgap.5,6,7,8,9,10,11,12,13,14 Since 2D MoS2 obtained by mechanical exfoliation limits the length scale only to a few micrometers, researchers have studied on how to fabricate such 2D MoS2 in a large scale,15,16,17,18,19,20 which would open the gate toward more practical applications enabling conventional photolithographic device/circuit patterning. Chemical vapor deposition (CVD) has thus become one of mainstream fabrication techniques to achieve large-scale MoS2 2D sheets. Many of success on large-scale MoS2 monolayer sheets have been reported.21,22,23 Yet, reports on conventional photolithographic patterning for large-scale 2D MoS2-based devices with decently high mobilities are still rare,24,25,26 to the best of our limited knowledge. For instance, CVD-grown monolayer MoS2 FETs might have never been used for both switch and driver of organic light-emitting diodes (two FETs in an OLED pixel for active matrix: see the circuit details in Supporting Information Figure S1), while exfoliated TMD-based FETs were barely used once with poor yield as a proof-of-concept-type demonstration.27 According to previous works, low threshold voltage would be an important issue for OLED pixel switching.26,27

In the present work, we have fabricated CVD-grown large-scale MoS2 FETs with patterned bottom gate and investigated their applications toward analog OLED pixel as low voltage switching and high current driving FETs. In particular, we successfully spin-coated an ultrathin hydrophobic polystyrene (PS) polymer layer on Al2O3 dielectric before the CVD MoS2 monolayer was transferred onto the gate-patterned Al2O3 on glass, so that the uniformity of threshold voltage (Vth) of FETs might be improved. Our MoS2 FET shows a linear mobility of ~10 cm2 V−1 s−1 and an ON/OFF current ratio of 108 as patterned by photolithography on glass, and those values are regarded quite high or comparable to those of previous CVD MoS2 FETs28,29,30,31,32 because a single grain of our CVD MoS2 monolayer appears as large as ~60 μm in side dimension. Among 48 MoS2-based FETs realized from the same CVD MoS2 wafer, 38 devices successfully work (yield ~80%) operating at ~5 V with 50 nm-thick Al2O3 bottom gate dielectric. Dynamic/static switchings of blue and green OLED pixels were nicely demonstrated using the CVD monolayer MoS2 FETs.

Results and discussion

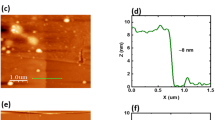

According to scanning electron microscope (SEM) images of Fig. 1a–c, sufficiently large area and continuous MoS2 monolayer film was achieved (Fig. 1b). For the CVD growth, we used a single precursor source consisting of MoS2 powder at a high growth temperature ~800 °C with a temperature of 900 °C for the powder precursor,33 instead of the combination of MoO3 and S, which is more often reportedly used (see Methods section for more details).15,16,17 From a more magnified view of the film region, a grain boundary is distinguished better as indicated by dashed outline in Fig. 1c. The average individual grain size is 2000 µm2. At the periphery of the substrate, characteristic triangular-shaped monolayer MoS2 with side dimensions from 30 to 60 µm were observed (Fig. 1a). In Fig. 1a we can also see how the monolayers start to join to ultimately form the continuous film. These results were obtained from all the thermally oxidized SiO2/Si substrates we used. Continuous film area approaches to a few mm2. Micro-Raman spectroscopy was used to confirm the monolayer nature of the MoS2 grown as the separation between the E12g and A1g Raman peaks is known to be characteristic of the number of MoS2 layers.34,35,36 The spectra obtained over the film regions (Fig. 1b) are shown in the red “1L” curve of Fig. 1d, with a peak separation of 20.2 cm−1. For further confirmation, we have put the spectra for bilayer (2L, blue, 23.2 cm−1 peak separation) and trilayer (3L, green, 24.2 cm−1 peak separation) MoS2 spots that we could sometimes find at the very outer periphery of the substrates, where MoS2 nucleation might not be so controllable resulting in more vertical growth (supporting photo image of the outer periphery is seen in Figure S2). We also included the Raman spectrum from bulk MoS2 powder (black line), which exhibited a 25.1 cm−1 peak separation. To assess the quality of the MoS2 monolayer films,37,38,39 we plot in Fig. 1e the full width at half maximum (FWHM) of the E12g and A1g Raman peaks for the material grown on the various thicknesses of SiO2. The FWHM was essentially independent of the oxide thickness, staying in the range of 2–2.5 and 3.5 cm−1 for the E12g and A1g, respectively. For comparison, FWHM values reported to date for the E12g and A1g peaks of CVD-grown monolayer have been in the ranges of 3.5–4.2 and of 5–7 cm−1 respectively.35,40,41 Furthermore, MoS2 monolayers exfoliated from geological materials exhibit a FWHM of 3.7 cm−1 for E12g peak in report.42 Therefore, the FWHM data we obtained may indicate that our CVD-grown monolayer MoS2 is comparable to or potentially better in crystalline quality than reported ones.43 We might attribute such good crystalline quality along with large-scale continuous monolayer MoS2 to a high growth temperature over ~800 °C with a temperature of 900 °C for the powder precursor, since the higher temperature enhances surface diffusion of adatoms and lateral crystal growth, and therefore smooth coalescence into a continuous film. The optical properties of our MoS2 monolayer films were also characterized using power-dependent photoluminescence (PL) measurements at room temperature, as shown in Fig. 1f. A strong emission related to the A-exciton in MoS2 was observed at 1.84 eV. The B-exciton-related peak could also be distinguished at 1.99 eV. The peak separation of 150 meV is due to the splitting of valence band.2,42,44 The peak positions did not shift with exciton power. The inset of Fig. 1f shows that the luminescence emission intensity (IPL) follows a power relationship with incident laser excitation power (IL): IPL = nILα.45 The exponent α indicates the type of radiative recombination process the PL originates from, with an exponent of 1 corresponding to free exciton recombination. In our samples, a slope of 0.79 (as α) was obtained, which indicates the recombination is close to excitonic although there is some degree of defect-related recombination.46,47 We have also compared the FWHM of the main luminescence peak for the MoS2 films grown on the various thicknesses of SiO2 as shown in Fig. 1g. The FWHM was found to range from 60 to 80 meV, which is close to the best reported value (60 meV) to date (50 meV is for the suspended MoS2 monolayer2).15

Scanning electron microscope (SEM) image of chemical vapor deposition (CVD)-grown MoS2. a Triangular shape MoS2 located near periphery, b whole area-covering MoS2 monolayer near central region. Each scale bar in a is 20 μm and in b is 200 μm. c Grain boundary is indicated by dashed line. Scale bar is 20 μm. d Raman spectra of 1L, 2L, and 3L CVD MoS2, and bulk. e Raman peak full width at half maximum (FWHM) of 1L MoS2 grown on differently thick SiO2. f PL spectra of 1L CVD MoS2 under varied laser power (inset). g Photoluminescence (PL) spectra FWHM plot obtained from varied SiO2 thickness

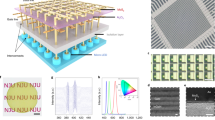

The large-scale MoS2 monolayer was transferred onto a 50 nm-thick Al2O3 dielectric, beneath which a patterned Au gate was located already. Our MoS2 was then aligned and patterned on the gate as channels by conventional photolithography including O2 plasma dry etching. Figure 2a displays such patterned MoS2 channels (red dotted-line rectangles) and gates in optical microscope (OM) images along with a schematic cross section (left inset) while completed devices (16 FETs) with Au S/D electrodes are also shown in the right inset as another OM image. As stated in the introduction part, we particularly spin-coated an ultrathin hydrophobic PS layer on Al2O3 dielectric before the transfer of CVD MoS2 monolayer, expecting and targeting a relatively uniform Vth distribution of MoS2 FETs. But we also fabricated another set of MoS2 FETs with bare Al2O3 without PS layer, so to compare the two types of FET devices with and without PS layer. Capacitance-voltage (C-V) measurements were thus conducted for two different dielectrics (see Figure S3 for the values of 8.46 nm PS/50 nm Al2O3 and 50 nm Al2O3). In addition, another PS layer was utilized as a technical sacrificial cover to transfer monolayer MoS2 during these device fabrications, and this second PS layer is peeled-off from MoS2 after transferring onto dielectric, while the ultrathin PS layer on Al2O3 stays firm because it covalently bonded on Al2O3 surface (see fabrication details in Methods section and Supporting Information, Figure S4.) According to the OM images of channels in Fig. 2a, most of the monolayer channels appear clean without any distinguishable specks except a few channels, which might contain nonuniform thickness (bilayer or trilayer) regions. Figure 2b is an SEM image from two MoS2 FETs with S/D electrodes as example devices for switch and driver of an OLED pixel circuit (as described in the overlaid inset circuit). The red rectangles in Fig. 2b identify the channel area as partially covered by S/D region while Fig. 2c illustrates the same circuit as a three-dimensional drawing.

a Optical microscope (OM) images of patterned chemical vapor deposition (CVD)-MoS2 channels (red dotted rectangles) on patterned bottom gate (left inset for cross section) and OM images of field- effect transistors (FETs; right inset with patterned Au S/D electrode). b Scanning electron microscope (SEM) image of switching and driver FETs for an organic light-emitting diode (OLED) pixel. Circuit for an OLED pixel is overlaid on SEM image. c Schematic three-dimensional (3D) view of those FETs for the OLED pixel circuit. Hydrophobic polystyrene (PS) layer on oxide dielectric is worth to note in our FETs (schematic 3D and cross-sectional two-dimensional). All scale bars are 20 μm

As we fabricated 48 MoS2 FETs with PS layer (type 1, FET with PS/Al2O3 bilayer for gate dielectric) and 32 FETs without PS layer (type 2, FET with Al2O3 only), 38 FETs operated among total 48 while 22 FETs appeared alive among total 32 devices (~80% vs. ~70% in yield for type 1 vs. type 2). Figure 3a shows drain current-gate voltage (ID-VGS) transfer characteristics of such 38 FETs with PS layer (type 1), and the transfer curves from 22 FETs without PS (type 2) were put to Supporting Information, Figure S5a and b. We compare device uniformity between FETs with PS layer and without in Fig. 3b, where the histograms of Vth and gate hysteresis (∆VGS) are plotted as obtained from those two types of FETs. The Vth distribution of FETs with PS layer appears quite uniformly centered (near −1 V) while that of FETs without is relatively scattered, and the ∆VGS of the former devices appears mostly smaller (as ~1 V in average) than that of the latter (approximately more than 3 V). Failed or low-performance FETs seem to originate from the transfer failure of MoS2 monolayer, which includes tearing and possible wrinkling during transfer whether on PS/Al2O3 or bare Al2O3 surface. It is, however, regarded that the hydrophobic PS layer surface certainly improves the device uniformity and causes hysteresis reduction due to trap density reduction at the MoS2 channel/dielectric interface. Among the 48 FETs of Fig. 3a, we selected two FETs for switch and driver, which have red and blue curves, respectively for active OLED pixel operation. Figure 3c shows transfer characteristics of switching MoS2 FET (inset circuit), where ∆VGS (~1 V) and Vth (~−1 V) of the device are displayed along with ON ID current of a few μA and high ON/OFF ID ratio of ~108 at a drain voltage (VDS) of 1, 3, and 5 V. Gate leakage was <~100 fA only. Output (ID-VDS) characteristics of the switching device are shown in Fig. 3d where ohmic behavior between Au and S/D is confirmed. Inset linear mobility plot of Fig. 3d shows that the average mobility of switching FET is as high as ~8 cm2 V−1 s−1. On the one hand, from the type 1 FET group in Fig. 3a we chose another device (blue transfer curve) for driving FET whose Vth is a little deviated to more (−) direction from central region. Our selection was according to a natural expectation that this FET would draw more current for OLED operation, although such Vth deviation may be undesirable in producing uniform devices. This deviation may come from bilayer- or trilayer-containing MoS2 channel. Figure 3e displays the transfer characteristics of driving MoS2 FET (inset circuit), where ∆VGS (~1 V) and Vth (~−4 V) of the device are shown along with high ID current of more than 5 μA at 5 V of VDS and high ON/OFF ID ratio of ~108 at 1, 3, and 5 V of VDS. Output characteristics of the driver FET are quite similar to those of switching device as shown in Fig. 3f. Inset mobility plot of Fig. 3f shows the linear mobility of driving FET as ~15 cm2 V−1 s−1. In fact, maximum mobility of ~15 cm2 V−1 s−1 and average of 8–10 cm2 V−1 s−1 were achieved from our type 1 FETs. Those decently high mobility values might come from large MoS2 grain size (~60 μm), which is relatively larger than channel length (L = 4.5 μm) and width (W = 10 μm).

a Transfer curves of total 38 chemical vapor deposition (CVD) MoS2 field- effect transistors (FETs) with polystyrene (PS) layer obtained at VD = 5 V (without including hysteresis). Blue and red curve FETs were selected for driver and switching devices in the pixel operation. b Histograms of the Vth and ∆VGS from 38 FETs (w/ PS) and 22 FETs (w/o PS). c Transfer curves of switching driver FETs obtained at VD = 1, 3, and 5 V (including hysteresis). Switching FET is indicated in the inset organic light-emitting diode pixel circuit by red dotted circle. d Output curve of switching FET and inset linear mobility plot. e Transfer curves of driver FET obtained at VD = 1, 3, and 5 V (including hysteresis). Driver FET is indicated in the inset circuit by red dotted circle. f Output curve of driver FET and inset linear mobility plot

Based on the device performances of the switching and driving FETs, an analog pixel operation for a single OLED was attempted with a circuit (the inset of Fig. 4c) under voltage conditions: a fixed supplied voltage (VDD), varied switching voltages (VSwitch), and varied data voltages (VData). Figure 4a shows OLED current (IOLED) and output voltage (VOUT) with respect to VData sweep, which was taken to turn on a green OLED (inset displays I-V curve characteristics of green and blue OLED). It is no doubt that high VSwitch (=8 V) and VData (=3 V) cause (or drive) high IOLED with most intense brightness among three different pixel displays of Fig. 4b. Medium and low IOLED are also displayed with VSwitch of 5 and 3 V showing their respective brightness in Fig. 4b. The value of VDD-VOUT matches with the applied voltage to the OLED pixel itself. Similar behavior of analog pixel operation was observed from a single blue OLED with two different switching voltages of 5 and 8 V as shown in Fig. 4c, d. However, it is recognized from blue OLED pixel operation that we might need higher VSwitch to brighten up the blue light than that for the case of green OLED. According to Fig. 4d, IOLED values of blue OLED are higher than those of green OLED for VSwitch (=8 and 5 V) while blue lights appear much dimmer than green lights.

a Organic light-emitting diode (OLED) current (left y-axis) and output voltage (right y-axis) plots obtained from the pixel circuit by VData sweep for green OLED (under VSwitch = 3, 5, and 8 V). Inset I-V curves were obtained from green and blue OLED diodes. b Each VSwitch condition causes different emission intensity and IOLED. c IOLED and VOUT plots obtained from the pixel circuit by VData sweep for blue OLED (VSwitch = 5 and 8 V). Inset pixel circuit is seen for analog OLED pixel operation. d Each VSwitch condition causes different blue emission intensity and IOLED. All scale bars are 50 μm

Dynamic ON/OFF switching of OLED pixels was attempted as shown in Fig. 5a, b, which are according to their static light-emitting performances in Fig. 4a–d. Figure 5a shows the IOLED and VOUT dynamics in green OLED pixel circuit as obtained by temporally modulating VData (between −3 and 3 V at 1 Hz). ON and OFF switching was observed from all the switching voltages (=3, 5, and 8 V), and of course, the green emission intensity appears distinguishable according to each switching voltage. For blue OLED pixel operation of Fig. 5b, almost the same dynamics was expected and observed from the circuit, however, in fact a low VSwitch of 3 V could not turn on the blue light at its IOLED (=~0.18 μA) while 6 and 8 V turn on the OLED without problem. Based on the IOLED results of Fig. 5a, b, dynamic OLED emissions for green and blue lights are displayed in Fig. 5c for more detailed comparison between the two OLEDs. According to Fig. 5c, the blue light appears completely dark at IOLED (=~0.18 μA) and 3 V switching voltage while the green emission is still very bright at the same voltage and even lower IOLED (=~0.15 μA). Such emission difference in both dynamic and static operations comes from their respective emission efficiencies since green OLED emission displays a higher efficiency than blue ones in general. On the one hand, an obvious delay in VOUT dynamics (Fig. 5b) for blue emission was observed under 3 V of VSwitch. It is probably because I-V curve characteristics of blue OLED is different from that of green OLED. According to the inset plots of Fig. 4a, blue OLED should have higher resistance (dV/dI) in the range of 1–3 V than green OLED device. Such higher resistance (R) might cause longer RC delay under the same parasitic capacitance (C) condition. Nevertheless, it is regarded that our CVD MoS2 monolayer channel FETs overall show strong potentials to function as the gate switch and IOLED driver for analog OLED pixel circuits.

Time domain plots of organic light-emitting diode (OLED) current and output voltage. a For ON (light) and OFF (dark) switching in the pixel circuit of green OLED, VData was modulated between −3 and 3 V at 1 Hz under three different VSwitch = conditions 3, 5, and 8 V. b For ON and OFF switching in the blue OLED pixel circuit, VData was modulated between 0 and 5 V at 1 Hz under three different VSwitch = conditions 3, 6, and 8 V. c Dynamic emission properties of green vs. blue OLED pixels. Even under smaller IOLED current, green light appears brighter than blue emission. Under VSwitch = 3 V, blue OLED cannot be turned on. All scale bars are 50 μm

Based on above switching dynamics results from Fig. 5a–c, we further conducted two types of more advanced dynamic switching: digital switching of 2 × 1 OLED pixel array and grayscale analog switching of single blue/green OLED pixel. These demonstrations were carried out under fixed VDD and VSwitch (VDD = VSwitch = 5 V), which appears to be a proper condition for pixel display in Fig. 5c when two alternating VData pulses are used between 0 and +5 V. Figure 6a shows 2 × 1 OLED pixel array operation employing four CVD MoS2 FETs, where green OLED is ON with VData,1 of +5 V when blue one is OFF with VData,2 of 0 V at a certain time t1, and vice versa at time t2. Such alternating digital operations are displayed with IOLED and VOUT from each OLED pixel circuit (green and blue) as shown in Fig. 6b. Grayscale analog pixel operation was designed as plotted in time-VIN (=VData), and in this case VIN decreases with 1 volt step in 4 s. According to resultant time-IOLED plots in Fig. 6d, e, grayscale pixel display appears quite clear in each step of IOLED. For each color, four different intensities of OLED are obtained while green color is much brighter than blue one as expected. Another interesting to note is that VOUT difference in analog green OLED driving is much minimal compared to that in analog blue driving. In other words, small VOUT difference causes large difference in IOLED for green OLED. Such difference between green and blue pixel would be again attributed to the I-V curve origins of green and blue OLED diode in the inset of Fig. 4a. Supporting Information, a video file (two MoS2 OLED.avi) is also prepared to demonstrate the digital switching of 2 × 1 pixel array and grayscale analog switching of single blue/green OLED pixel.

a Circuitry for digital alternate switching of 2 × 1 two-color organic light-emitting diode (OLED) pixel array, and b IOLED/VOUT dynamics for each color OLED under constant VDD = VSwitch = 5 V, periodic VData,1 = 5 and 0 V (VData,2 = 0 and 5 V, synchronously). c Time-VIN design plot for grayscale analog pixel switching. d, e Time domain IOLED and VOUT results for grayscale analog OLED pixel (blue and green)

In summary, we have fabricated CVD-grown a few mm large-scale MoS2 FETs and investigated their low voltage OLED pixel circuit applications. In particular, when CVD MoS2 monolayer was transferred onto gate-patterned Al2O3 dielectric on glass, an ultrathin hydrophobic PS layer was used as a moderating medium between MoS2 and Al2O3, to improve the uniformity of Vth and reduce the gate hysteresis in FETs. Our MoS2 FET shows its average linear mobility of 8–10 cm2 V−1 s−1 and a high ON/OFF ID ratio of 108 as patterned by photolithography on glass, and those values are regarded quite high or comparable to previous reports for CVD MoS2 FETs28,29,30,31,32 because a single grain of our CVD MoS2 monolayer appears as large as ~60 μm in side dimension. Among 48 MoS2-based FETs, 38 devices successfully work (yield ~80%) operating at ~5 V. Dynamic switching of blue and green OLED pixels was nicely demonstrated using the CVD monolayer MoS2 FETs in two ways: 2 × 1 digital pixel array switching and grayscale analog switching of single blue/green OLED pixel. We conclude that our CVD MoS2 FETs are very promising as backpanel devices for future active matrix OLED pixel display.

Methods

MoS2 CVD growth

The 2D MoS2 material was grown by CVD in a quartz tube furnace. A single precursor source was used, consisting of MoS2 powder.33 instead of the combination of MoO3 and S, which is more often reportedly used. The precursor was placed in a quartz boat at the center of a tube while the substrates were placed downstream. We did not use any substrate surface treatment to promote nucleation prior to growth. The growth was performed at a pressure of 10 mbar under 20 sccm Ar flow, with the furnace temperature ramped to 950 °C, for a duration of 20 min. This high temperature leads to the thermal evaporation of the MoS2 precursor, which nucleates and redeposits onto the substrates located at a cooler region of the furnace (estimated to be ~200 °C lower). The substrate temperature (~800 °C with a temperature of 900 °C for the powder precursor) is therefore also higher than those reported when a combination of MoO3 and S was used. We believe this higher growth temperature leads to enhanced surface diffusion during growth and therefore, in combination with the use of a single precursor, contributes to the larger area MoS2 monolayer film obtained here. Finally, the furnace was allowed to cool down naturally. Thermally oxidized silicon substrates were used in this work. The substrates were oxidized prior to growth under an O2/Ar at 1000 °C at an atmospheric pressure for the durations of 60, 120, 180, and 240 min, resulting in an oxide thickness of approximately 45, 75, 90, and 145 nm, respectively, as confirmed by ellipsometry. In addition, we have used commercially available 300 nm SiO2/Si wafer for comparison. To the best of our knowledge, this represents the first comparative study of MoS2 growth on different oxide thickness, while the majority of reported data was on thick 300 nm oxide.

Transfer process

As-grown MoS2 on the SiO2/p+-Si substrate was spin-coated by PS layer (molecular weight = 280,000, Sigma-Aldrich) at 3500 rpm for 60 s. The sample was annealed at 85 °C for 15 min. After baking, the resultant PS/MoS2/SiO2/p+-Si structure was dipped into deionized (DI) water, so that the PS/MoS2 membrane might be separated from the SiO2/p+-Si substrate and floated on the surface of DI water. The PS/MoS2 membrane was picked up and transferred onto the target (ultrathin PS/gate-patterned atomic layer deposition (ALD) Al2O3/glass or gate-patterned ALD Al2O3/glass) substrate. After the transfer to the target substrate, the sample was baked at 85 °C for 1 h and 180 °C for 30 min. The top PS residues were peeled-off by using toluene.48 (Supporting Information, Figure S4)

Device fabrication

The glass substrates were cleaned in acetone and ethanol using an ultrasonicator for 15 min. The Au/Ti (20 nm/10 nm) bilayer was deposited by DC magnetron sputtering system and patterned for bottom gate-electrodes by photolithography and lift-off process (lift-off layer: LOR 3A, Micro Chemical, and photoresist layer: AZ GXR-601, AZ electronic materials). For dielectric layers, ultrathin PS/50 nm-thick Al2O3 (or 50 nm-thick Al2O3 only) layer was prepared by ALD system and PS coating. For hydrophobic PS layer spin-coating, dimethyl chlorosilane-terminated PS (Polymer Source, Product No. P3881-SSiCl) was initially dissolved in toluene (Aldrich) solvent, and the oxygen plasma cleaning (150 W, 50 sccm, 20 s) was applied to the prepared Al2O3 dielectric surface. The PS-brush solution (10 mg/mL) was spin-coated onto the Al2O3 surface and then heated at 170 °C for 48 h inside a vacuum oven, so that the ultrathin PS layer may be covalently bonded to the plasma-treated Al2O3 surface.49,50 As stated in the above transfer process, as-grown monolayer was transferred from SiO2/p+-Si substrate to patterned bottom gate substrate using PS transfer method (Supporting Information, Figure S4).48 After transfer, CVD MoS2 flakes were patterned by photolithography and O2 plasma dry etching process. For the source (S) and drain (D) ohmic contact electrodes, Au (50 nm) was deposited and patterned using conventional photolithography and lift-off processes. Finally, we annealed the device at 250 °C in N2 ambient to improve the S/D contact for MoS2 channel.

Measurements

The device current-voltage (I-V) characterizations were carried out by a semiconductor parameter analyzer (HP 4155C, Agilent Technologies) and the capacitance-voltage (C-V) measurements were carried out by a LCR meter (HP4284A, Agilent Technologies). Electrical dynamics were investigated with a function generator (AFG 310, Sony/Tektronix). SEM images were taken with an Field Emission SEM (JSM-7800F, JEOL Ltd.). OLED sample pixels were supplied from Samsung Display Co.

Data availability

The datasets generated during and/or analyzed during the current study are available from the corresponding author on reasonable request.

References

Wang, Q. H., Kalantar-Zadeh, K., Kis, A., Coleman, J. N. & Strano, M. S. Electronics and optoelectronics of two-dimensional transition metal dichalcogenides. Nat. Nanotechnol. 7, 699–712 (2012).

Mak, K. F., Lee, C., Hone, J., Shan, J. & Heinz, T. F. Atomically thin MoS2: a new direct-gap semiconductor. Phys. Rev. Lett. 105, 136805 (2010).

Splendiani, A. et al. Emerging photoluminescence in monolayer MoS2. Nano Lett. 10, 1271–1275 (2010).

Kuc, A., Zibouche, N. & Heine, T. Influence of quantum confinement on the electronic structure of the transition metal sulfide TS2. Phys. Rev. B 83, 245213 (2011).

Radisavljevic, B., Radenovic, A., Brivio, J., Giacometti, V. & Kis, A. Single-layer MoS2 transistors. Nat. Nanotechnol. 6, 147–150 (2011).

Yin, Z. et al. Single-layer MoS2 phototransistors. ACS Nano 6, 74–80 (2012).

Yu, Y. et al. High phase-purity 1T′-MoS2- and 1T′-MoSe2-layered crystals. Nat. Chem. 10, 638–643 (2018).

Radisavljevic, B., Whitwick, M. B. & Kis, A. Integrated circuits and logic operations based on single-layer MoS2. ACS Nano 5, 9934–9938 (2011).

Han, S. et al. Synthesis of WOn-WX2 (n=2.7, 2.9; X = S, Se) heterostructures for highly efficient green quantum dot light-emitting diodes. Angew. Chem. Int. Ed. 56, 10486–10490 (2017).

Li, H., Wu, J., Yin, Z. & Zhang, H. Preparation and applications of mechanically exfoliated single-layer and multilayer MoS2 and WSe2 nanosheets. Acc. Chem. Res. 47, 1067–1075 (2014).

Yin, Z. et al. Preparation of MoS2–MoO3 hybrid nanomaterials for light-emitting diodes. Angew. Chem. Int. Ed. 53, 12560–12565 (2014).

Li, H. et al. Fabrication of single- and multilayer MoS2 film-based field-effect transistors for sensing NO at room temperature. Small 8, 63–67 (2012).

Lee, H. S. et al. MoS2 nanosheet phototransistors with thickness-modulated optical energy gap. Nano Lett. 12, 3695–3700 (2012).

Choi, K., Lee, Y. T. & Im, S. Two-dimensional van Der Waals nanosheet devices for future electronics and photonics. Nano Today 11, 626–643 (2016).

van der Zande, A. M. et al. Grains and grain boundaries in highly crystalline monolayer molybdenum disulphide. Nat. Mater. 12, 554–561 (2013).

Najmaei, S. et al. Vapour phase growth and grain boundary structure of molybdenum disulphide atomic layers. Nat. Mater. 12, 754–759 (2013).

Lee, Y. H. et al. Synthesis of large-area MoS2 atomic layers with chemical vapor deposition. Adv. Mater. 24, 2320–2325 (2012).

Tan, L. K. et al. Atomic layer deposition of a MoS2 film. Nanoscale 6, 10584–10588 (2014).

Jin, Z., Shin, S., Kwon, D. H., Han, S.-J. & Min, Y.-S. Novel chemical route for atomic layer deposition of MoS2 thin film on SiO2/Si substrate. Nanoscale 6, 14453–14458 (2014).

Liu, K.-K. et al. Growth of large-area and highly crystalline MoS2 thin layers on insulating substrates. Nano Lett. 12, 1538–1544 (2012).

Lee, Y. et al. Synthesis of wafer-scale uniform molybdenum disulfide films with control over the layer number using a gas phase sulfur precursor. Nanoscale 6, 2821–2826 (2014).

Lim, Y. R. et al. Wafer-scale, homogeneous MoS2 layers on plastic substrates for flexible visible-light photodetectors. Adv. Mater. 28, 5025–5030 (2016).

Lim, Y. R. et al. Roll-to-roll production of layer-controlled molybdenum disulfide: a platform for 2D semiconductor-based industrial applications. Adv. Mater. 30, 1705270 (2018).

Kwon, H. et al. Large scale MoS2 nanosheet logic circuits integrated by photolithography on glass. 2D Mater. 3, 044001 (2016).

Yu, L. et al. Graphene/MoS2 hybrid technology for large-scale two- dimensional electronics. Nano Lett. 14, 3055–3063 (2014).

Choi, M. et al. Flexible active-matrix organic light-emitting diode display enabled by MoS2 thin-film transistor. Sci. Adv. 4, eaas8721 (2018).

Yu, S. et al. Transition metal dichalcogenide-based transistor circuits for gray scale organic light-emitting displays. Adv. Funct. Mater. 27, 1603682 (2017).

Kang, K. et al. High-mobility three-atom-thick semiconducting films with wafer-scale homogeneity. Nature 520, 656–660 (2015).

Zhao, M. et al. Large-scale chemical assembly of atomically thin transistors and circuits. Nat. Nanotechnol. 11, 954–959 (2016).

Liu, H. et al. Statistical study of deep submicron dual-gated field-effect transistors on monolayer chemical vapor deposition molybdenum disulfide films. Nano Lett. 13, 2640–2646 (2013).

Dai, Z. et al. Large-area chemical vapor deposited MoS2 with transparent conducting oxide contacts towards fully transparent 2D electronics. Adv. Funct. Mater. 27, 1703119 (2017).

Jeon, J. et al. Layer-controlled CVD growth of large-area two-dimensional MoS2 films. Nanoscale 7, 1688–1695 (2015).

Garg, S., Mollah, A. S., Waters, J. L., Kim, S. M. & Kung, P. Transition metal dichalcogenide semiconductor growth and large area devices for optoelectronics and sensing. ECS Trans. 80, 1–11 (2017).

Zhu, W. et al. Electronic transport and device prospects of monolayer molybdenum disulphide grown by chemical vapour deposition. Nat. Commun. 5, 3087 (2014).

Yu, Y. et al. Controlled scalable synthesis of uniform, high-quality monolayer and few-layer MoS2 films. Sci. Rep. 3, 1866 (2013).

Lee, Y.-H. et al. Synthesis and transfer of single layer transition metal disulfides on diverse surfaces. Nano Lett. 13, 1852–1857 (2013).

Neumann, C. et al. Raman spectroscopy as probe of nanometre-scale strain variations in graphene. Nat. Commun. 6, 8429 (2015).

Mignuzzi, S. et al. Effect of disorder on Raman scattering of single-layer MoS2. Phys. Rev. B 91, 195411 (2015).

Antonelou, A., Hoffman, T., Edgar, J. H. & Yannopoulos, S. N. MoS2/h-BN heterostructures: controlling MoS2 crystal morphology by chemical vapor deposition. J. Mater. Sci. 52, 7028–7038 (2017).

Wang, S. et al. Shape evolution of monolayer MoS2 crystals grown by chemical vapor deposition. Chem. Mater. 26, 6371–6379 (2014).

Chen, J. et al. Chemical vapor deposition of high-quality large-sized MoS2 crystals on silicon dioxide substrates. Adv. Sci. 3, 1600033 (2016).

Cheiwchanchamnangij, T. & Lambrecht, W. R. L. Quasiparticle band structure calculation of monolayer, bilayer, and bulk MoS2. Phys. Rev. B 85, 205302 (2012).

Lee, C. et al. Anomalous lattice vibrations of single- and few-layer MoS2. ACS Nano 4, 2695–2700 (2010).

Liu, L., Qiu, H., Wang, J., Xu, G. & Jiao, L. Atomic MoS2 monolayers synthesized from a metal–organic complex by chemical vapor deposition. Nanoscale 8, 4486–4490 (2016).

Feng, Z. C., Mascarenhas, A. & Choyke, W. J. Low temperature photoluminescence spectra of (001) CdTe films grown by molecular beam epitaxy at different substrate temperatures. J. Lumin. 35, 329–341 (1986).

Senthilkumar, V. et al. Direct vapor phase growth process and robust photoluminescence properties of large area MoS2 layer. Nano Res. 7, 1759–1768 (2014).

Chen, B. et al. Large-area high quality MoS2 monolayers grown by sulfur vapor counter flow diffusion. RSC Adv. 6, 50306–50314 (2016).

Gurarslan, A. et al. Surface-energy-assisted perfect transfer of centimeter-scale mono layer and few-layer MoS2 films onto arbitrary substrates. ACS Nano 8, 11522–11528 (2014).

Kim, S. H., Jang, M., Yang, H., Anthony, J. E. & Park, C. E. Physicochemically stable polymer-coupled oxide dielectrics for multipurpose organic electronic applications. Adv. Funct. Mater. 21, 2198–2207 (2011).

Jeong, Y. et al. 2D MoSe2 transistor with polymer-brush/channel interface. Adv. Mater. Interfaces 5, 1800812 (2018).

Acknowledgements

The authors acknowledge the financial support from NRF (NRL program: Grant No. 2017R1A2A1A05001278, SRC program: Grant No.2017R1A5A1014862, vdWMRC center). J.H.P. acknowledges this research was supported by Basic Science Research Program through the National Research Foundation of Korea (NRF) funded by the Ministry of Education (NRF-2017R1A6A3A11035872). S.M.K. acknowledges travel support from NSF for US-Korea collaboration.

Author information

Authors and Affiliations

Contributions

H.K. performed the fabrication and measurements of the MoS2 transistors and demonstration of the AMOLED pixel, S.G. and P.K. performed the synthesis and characterization of the MoS2 films, S.M.K. performed Raman and PL measurement, J.H.P. and Y.J. helped with PS layer, S.Y. helped with 3D figure scheme techniques, and S.I. designed whole device experiments. All authors discussed the results.

Corresponding author

Ethics declarations

Competing interests

The authors declare no competing interests.

Additional information

Publisher’s note: Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Supplementary information

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made. The images or other third party material in this article are included in the article’s Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Kwon, H., Garg, S., Park, J.H. et al. Monolayer MoS2 field-effect transistors patterned by photolithography for active matrix pixels in organic light-emitting diodes. npj 2D Mater Appl 3, 9 (2019). https://doi.org/10.1038/s41699-019-0091-9

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41699-019-0091-9

This article is cited by

-

Research progress of optoelectronic devices based on two-dimensional MoS2 materials

Rare Metals (2023)

-

Structural, optical, and photo-response properties of MoO3:W:S compound thin films prepared by spray pyrolysis: effect of annealing under sulfuration and bandgap modulation

Journal of Materials Science: Materials in Electronics (2022)

-

Design and Analysis of Junctionless FinFET with Gaussian Doped for Non-polar Structure

Silicon (2022)

-

Van der Waals epitaxial growth and optoelectronics of a vertical MoS2/WSe2 p–n junction

Frontiers of Optoelectronics (2022)

-

Bottom-up water-based solution synthesis for a large MoS2 atomic layer for thin-film transistor applications

npj 2D Materials and Applications (2021)