Abstract

Fabrication of hydrogen-terminated diamond (H-diamond) field-effect transistor (FET) with AlOx dielectric layer has been successfully carried out. The AlOx layer was formed by auto-oxidizing 6 nm Al film in the air at room temperature, and a FET without AlOx dielectric layer has also been fabricated for comparison. For both FETs, 100 nm Al layers were deposited as the gate electrodes, respectively. The leakage current density in FET with AlOx dielectric layer was four magnitude orders lower than that without AlOx dielectric layer at VGS = −5 V, indicating that AlOx dielectric layer could effectively reduce leakage current and prevent reverse ID in ID − VDS caused by defects on diamond surface. Distinct pinch-off characteristic with p-type channel was observed in ID − VDS measurement. The threshold voltage was −0.4 V at VDS = −15 V.

Similar content being viewed by others

Introduction

Diamond is an attractive material with many excellent properties such as good bio-compatibility, highest thermal conductivity (22 W/K·cm), large bandgap (5.45 eV), high theoretical breakdown voltage (>10 MV·cm−1), high carrier mobilities (electron: 4500 cm2 V−1 S−1, hole: 3800 cm2 V−1 S−1) etc., having potential applications in biology field, especially electronic devices such as metal oxide semiconductor field-effect transistors (MOSFETs) and metal semiconductor field-effect transistors (MESFETs)1,2,3,4,5,6,7,8, which can operate in high frequency, high power, high temperature. However, due to the high dopants activation energies (boron 380 meV and phosphorous 570 meV) in diamond at this stage, carrier densities are quite low at room temperature (RT), leading to the poor performance of MOSFET and MESFET based on diamond8. In order to overcome this issue, some groups try to use δ-doping technique in diamond. However, this technique was complex and the carrier mobility is not enough9,10. Fortunately, when diamond surface is terminated with C-H bonds by hydrogen plasma treatment, two-dimensional hole gases (2DHG) with 1013 cm−2 sheet carrier density can be accumulated on its surface11, by which H-diamond FET can be fabricated.

Up to now, many dielectric materials have been used in H-diamond FETs such as SiO212, ZrO25, Al2O313, AlN14, TiOx4, HfO215, LaAlO316 and Ta2O517. To fabricate gate dielectric layers in H-diamond MOSFETs, many methods have been used such as atomic layer deposition, metal organic chemical vapor deposition or magnetron sputtering techniques. However, these techniques are expensive, complex and may deteriorate 2DHG channel layer by high temperature or plasma etching, because 2DHG of H-diamond is thermally and chemically instable18. Therefore, researchers should simplify gate oxide deposition and protect the 2DHG channel layer during fabrication process.

In this work, H-diamond FET with AlOx dielectric layer formed by auto-oxidizing in the air at RT was successfully fabricated. To authors’ knowledge, few investigations on H-diamond FETs using autoxidation AlOx dielectric layer has been reported.

Methods

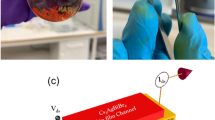

Two 3×3 × 0.5 mm3 Ib-type single crystal diamonds (001) were used as substrates defined as sample A and B. Figure 1(a,b) showed the fabrication process of the H-diamond FET with AlOx dielectric layer (sample A) and FET without AlOx dielectric layer (sample B), respectively.

To remove non-diamond phase from diamond surfaces, sample A and B were cleaned by a mixed acid and then treated with a mixed alkali as our previous work6, shown as Fig. 1(a,b-i). After that, microwave plasma CVD system (AX5200 Seki Technotron Corp.) was used to grow 200 nm single crystal H-diamond on sample A and B, shown as Fig. 1(a,b-ii). The growth conditions has been shown in our previous report7. Then, source and drain Au electrodes were fabricated on sample A and B by photolithographic and electron beam evaporation (EB) techniques, shown as Fig. 1 (a,b-iii). The thickness and space of electrodes (LSD) were 100 nm and 20 μm, respectively. Thereafter, negative photoresist was used to coat on channels between source and drain electrodes by photolithographic technique. After that, UV/ozone was used on sample A and B to form isolation, shown as Fig. 1(a,b-iv). Then, gate patterns were formed on sample A and B by photolithographic technique. For sample A, 6 nm Al film was deposited on diamond surface with gate patterns by EB technique, and then sample A was oxidized in the air at RT for 48 hrs to form AlOx dielectric layer, shown as Fig. 1(a-v). For comparison, sample B with gate patterns was placed in the air at RT for 48 hrs without 6 nm Al deposition on diamond surface. After 48 hrs done, 100 nm Al gate electrodes were deposited on sample A and B. The gate width (WG) and the gate length (LG) were 100 μm and 8 μm.

Micro-Raman, X-ray diffraction (XRD) and atomic force microscope (AFM) were used to characterize the samples, and the electrical properties of FETs with and without AlOx were measured using RT probe system all in the air at RT.

Results and Discussion

The quality of diamond with 200 nm single crystal H-diamond was characterized by Micro-Raman and XRD. 20 × objective lens was used in Raman measurement with 532 nm excitation laser and 0.4 cm−1/pixel resolution. Three Raman random points were measured on sample A and B, respectively. The average Raman FWHM results of sample A and B were 4.2 cm−1 and 4.0 cm−1, respectively. Rocking curves of sample A and B were measured by using four-bounce Ge (2 2 0)-monochromated Cu-K𝛼, with a 10 mm slit on the detector arm. The XRD FWHM of sample A and B were 0.012° and 0.011°, shown as Fig. 2(c). The roughness of sample A and B were 0.32 and 0.37 nm measured by AFM, shown as Fig. 2(a,b), respectively.

Figure 3(a,b) show the absolute value of gate leakage current density (|J|) of sample A and B in the log coordinate, respectively. Figure 3(c,d) show the gate leakage current density (J) of sample A and B, respectively. In Fig. 3(a,b), the gate-source voltages (VGS) was from −5 to 5 V. In Fig. 3(c,d), the VGS was from 0 to 5 V. When VGS decreased from 5 to 0 V, as shown in Fig. 3(c,d), the J decreased from 2.6 × 10−7 to 5 × 10−8 A·cm−2 for sample A and from 2.3 × 10−7 to −3 × 10−8 A·cm−2 for sample B, indicating that J of sample A and B were almost the same. When VGS decreased from 0 to −5 V in Fig. 3(a,b), J decreased from 5 × 10−8 to −1.0 × 10−3 A·cm−2 for sample A and from −3 × 10−8 to −40 A·cm−2 for sample B. And also, when VGS was −5 V, the J ratio between sample B and A was 4 × 104. It shows that the J of sample A was much smaller than that of sample B at VGS ranging between 0 and −5 V, indicating that AlOx dielectric layer in sample A could effectively reduce leakage current.

Figure 4 shows drain-source current (ID) versus drain-source voltage (VDS) output characteristics (ID − VDS) curves of (a) sample A and (b) sample B. In Fig. 4(a,b), the VGS was changed from 2 to −2.5 V in steps of −0.5 V. When VGS = 2, 1.5, 1, 0.5, 0 and −0.5 V, the curves of ID could not be distinguished due to the small value of them in Fig. 4(a). Base on the measurement results of sample A in Fig. 4(a), the ID shows the distinct pinch-off characteristic. And also, p-type channel characteristics were observed in Fig. 4(a), because the value of ID decreased with the decreasing of VDS value from 2 to −2.5 V3. When the VGS = −2.5 V and VDS = −6.4 V, ID was 300.9 μA, which was the maximum ID value in Fig. 4(a). When the VGS = 0 V and VDS = −6.4 V, ID was −5.6 × 10−6 μA (data not shown), indicating that on/off ratio was about 5.4 × 107. In Fig. 4(b), when VDS = 0 V, the reverse (positive) ID was observed, as indicated by the black arrow. And then, the value of ID decreased with the valve of VDS decreasing. The reason for the reverse ID was the gate leakage current according to Ricardo S. Sussmann19. This leakage current could be caused by defects on diamond surface19. In Fig. 4(a), no reverse ID was observed, indicating that gate leakage current was small in sample A, which was agreement with the results in Fig. 3. Therefore, AlOx dielectric layer in sample A can prevent reverse ID in ID − VDS measurement.

The transfer characteristics of sample A was measured to evaluate the threshold voltage (VTH) and maximum of extrinsic transconductance (gm), as shown in Fig. 5(a,b), respectively. In Fig. 5(a), the VTH was −0.44 V at the VDS = −15 V calculated by method of Jiangwei Liu15, indicating that FET with AlOx dielectric layer showed enhancement mode (normally-off), which has been discussed in our previous report6. One reason for normally-off characteristics is decreasing of hydrogen-termination on diamond surface during fabrication process of sample A, such as photolithographic and EB process. Another reason could be the depletion of hole carriers in FET under channel, which is due to the large difference of work function between 100 nm Al gate and H-diamond6. In Fig. 5(b), the gm was 1.8 mS·mm−1 at VDS = −15 V and VGS = −2.1 V.

In our previous work, normally-off H-diamond FET had been carried out with 3 nm Al2O3 dielectric layer6. However, in this work, H-diamond FET with 6 nm AlOx has been realized. For the previous one, 3 nm discontinuous Al2O3 film was formed by thermally oxidizing 3 nm Al in the air. During the long time thermally oxidization and gate electrode deposition process, parts of adsorbate and hydrogen-termination between Al2O3 gaps on H-diamond could be reduced18,20. While for this work, 6 nm continuous AlOx film was formed by auto-oxidizing 6 nm Al film at RT, and could protect adsorbate and hydrogen-termination during gate electrode deposition process18,20.

Conclusions

In summary, fabrication of H-diamond FETs with AlOx dielectric layer formed by auto-oxidizing 6 nm Al layer in the air at RT has been successfully carried out. The leakage current density in FET with AlOx dielectric layer was 4 × 104 lower than that without AlOx dielectric layer at VGS = −5 V. The AlOx dielectric layer can reduce leakage current and prevent reverse ID in ID − VDS caused by defects on diamond surface. The on/off ratio of FET with AlOx dielectric layer was 5.4 × 107. FET with AlOx dielectric layer has shown normally-off characteristics with −0.44 V threshold voltage at VDS = −15 V.

References

H. Kawarada et al. Wide Temperature (10–700 K) and High Voltage (~1000V) Operation of C-H Diamond MOSFETs for Power Electronics Application, Electron Devices Meeting 2015, 11.2.1–11.2.4 (2015).

Jiangwei Liu et al. Logic circuits with hydrogenated diamond field-effect transistors. IEEE Electron Device Letters 38, 992–925 (2017).

Wang, W. et al. Diamond based field-effect transistors with SiNx and ZrO2 double dielectric layers. Diamond & Related Materials 69, 237–240 (2016).

Jing Zhao et al. Assembly of a high-dielectric constant thin TiOx layer directly on H-terminated semiconductor diamond. Applied Physics Letters 108, 012105 (2016).

Jiangwei Liu et al. Low on-resistance diamond field effect transistor with high-k ZrO2 as dielectric. Scientific Reports 4, 6395 (2014).

Wang, Y.-F. et al. Normally-off hydrogen-terminated diamond field-effect transistor with Al2O3 dielectric layer formed by thermal oxidation of Al. Diamond & Related Materials 81, 113–117 (2018).

Yan-Feng, Wang et al. Ohmic contact between iridium film and hydrogen-terminated single crystal diamond. 7, 12157 (2017).

Chicot, G. et al. Metal oxide semiconductor structure using oxygen-terminated diamond. Applied Physics Letters 102, 242108 (2013).

Kunze, M., Vescan, A., Dollinger, G., Bergmaier, A. & Kohn, E. δ-Doping in diamond. Carbon 37, 787–791 (1999).

El-Hajj, H. et al. Characteristics of boron δ-doped diamond for electronic applications. Diamond & Related Materials 17, 409–414 (2008).

Masataka Imura et al. Development of AlN/diamond heterojunction field effect transistors. Diamond & Related Materials 124, 206–209 (2012).

Saito, T. et al. Fabrication of metal–oxide–diamond field-effect transistors with submicron-sized gate length on boron-doped (111) H-terminated surfaces using electron beam evaporated SiO2 and Al2O3. Journal of Electronic Materials 40, 247–252 (2011).

Kazuyuki Hirama et al. Characterization of diamond metal-insulator-semiconductor field-effect transistors with aluminum oxide gate insulator. Applied Physics Letters 88, 112117 (2006).

Kueck, D. et al. Passivation of H-terminated diamond with MOCVD-aluminum nitride–a key to understand and stabilize its surface conductivity. Physica Status Solidi 207, 2035–2039 (2010).

Liu, J. W., Liao, M. Y., Imura, M. & Koide, Y. Normally-off HfO2-gated diamond field effect transistors. Applied Physics Letters 103, 092905 (2013).

Liu, J. W. et al. Control of normally on/off characteristics in hydrogenated diamond metal-insulator-semiconductor field-effect transistors. Journal of Applied Physics 118, 115704 (2015).

Liu, J. W. et al. Diamond field effect transistors with a high-dielectric constant Ta2O5 as gate material. Journal of Physics D Applied Physics 47, 245102 (2014).

Riedel, M., Ristein, J. & Ley, L. Recovery of surface conductivity of H-terminated diamond after thermal annealing in vacuum. Physical Review B Condensed Matter 69, 125338 (2004).

Ricardo, S. Sussmann of referencing in CVD Diamond for Electronic Devices and Sensors (ed. Ricardo, S.) 296–298 (John Wiley & Sons Ltd, 2009).

Maier, F., Riedel, M., Mantel, B., Ristein, J. & Ley, L. Origin of Surface Conductivity in Diamond. Physical Review Letters 85, 16 (2000).

Acknowledgements

This work is supported by National Natural Science Foundation of China (NSFC) (61627812), Technology Coordinate and Innovative Engineering Program of Shaanxi (2016KTZDGY02-03) and Postdoctoral Science Foundation of China (PSFC) (2015M580850). This work is also supported by China Postdoctoral Science Foundation (2015M580850). We also thank Miss Yu Wang at Instrument Analysis Center of Xi’an Jiaotong University for their assistance with Raman analysis. This work is also supported by Nan Zhu, Jiuhong Wang, who gave help on AFM measurement using INNOVA of BRUKER.

Author information

Authors and Affiliations

Contributions

Yan-Feng Wang, Xiaohui Chang, Xiaofan Zhang, Jiao Fu designed the experiment. Yan-Feng Wang, Shuwei Fan, Renan Bu, Jingwen Zhang finished the experiment. Yan-Feng Wang, Dan Zhao, Guoqing Shao measured samples. Yan-Feng Wang, Zhangcheng Liu, Wei Wang, Hong-Xing Wang analyze the data. Yan-Feng Wang write this manuscript and all authors participate in discussions.

Corresponding author

Ethics declarations

Competing Interests

The authors declare no competing interests.

Additional information

Publisher’s note: Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made. The images or other third party material in this article are included in the article’s Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Wang, YF., Wang, W., Chang, X. et al. Hydrogen-terminated diamond field-effect transistor with AlOx dielectric layer formed by autoxidation. Sci Rep 9, 5192 (2019). https://doi.org/10.1038/s41598-019-41082-8

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41598-019-41082-8

Comments

By submitting a comment you agree to abide by our Terms and Community Guidelines. If you find something abusive or that does not comply with our terms or guidelines please flag it as inappropriate.