# SCIENTIFIC REPORTS

Received: 18 August 2017 Accepted: 27 November 2017 Published online: 08 December 2017

## **OPEN** Enhanced electronic-transport modulation in single-crystalline VO<sub>2</sub> nanowire-based solid-state fieldeffect transistors

Tingting Wei<sup>1,2</sup>, Teruo Kanki<sup>1</sup>, Masashi Chikanari<sup>1</sup>, Takafumi Uemura<sup>1</sup>, Tsuyoshi Sekitani<sup>1</sup> & Hidekazu Tanaka<sup>1</sup>

Field-effect transistors using correlated electron materials with an electronic phase transition pave a new avenue to realize steep slope switching, to overcome device size limitations and to investigate fundamental science. Here, we present a new finding in gate-bias-induced electronic transport switching in a correlated electron material, i.e., a VO<sub>2</sub> nanowire channel through a hybrid gate, which showed an enhancement in the resistive modulation efficiency accompanied by expansion of metallic nano-domains in an insulating matrix by applying gate biases near the metal-insulator transition temperature. Our results offer an understanding of the innate ability of coexistence state of metallic and insulating domains in correlated materials through carrier tuning and serve as a valuable reference for further research into the development of correlated materials and their devices.

As a representative transition metal oxide with correlated electrons, vanadium dioxide (VO<sub>2</sub>), has attracted considerable research attention because of its versatile properties. Primarily, this material shows a dramatic orders-of-magnitude resistivity change associated with the metal-insulator transition (MIT) at room temperature<sup>1,2</sup> and a distinct contrast in the optical properties<sup>3</sup> of the insulating and metallic phases. A variety of applications have been suggested based on these characteristics, such as multistate memory utilizing local domain transitions<sup>4-6</sup>, oscillators<sup>7-10</sup> and electrical/optical switching devices<sup>11-14</sup>. Among these applications, field-effect transistors (FETs) to control of the MIT by a gate bias, so-called Mott transistors (Mott-FETs), have been par-ticularly attractive over the past decade<sup>15-18</sup>. The field-triggered transport modulation ratio, however, has demonstrated comparatively low values of less than 0.6% for fast switching (or  $\sim$ 5% for slow switching)<sup>19-22</sup>. Much effort has been devoted to enhancing the resistance modulation, mainly focusing on inducing a large carrier density via a high electric field using a high-dielectric-constant (high-k) gate dielectric. The recent development of Mott-FETs has been attempted by fabricating an electric double-layer transistor (EDLT) with a strong electric field by applying to VO<sub>2</sub> channels<sup>23,24</sup>, while the existence of issues in the chemical reaction remain under debate<sup>25</sup>. In our previous report using VO<sub>2</sub> thin-film-based FETs, a high-k inorganic Ta<sub>2</sub>O<sub>5</sub>/organic polymer parylene hybrid solid gate insulator<sup>22,26,27</sup> was demonstrated, leading to reversible and prompt electrical-transport modulation owing to reduced interface deterioration and a high dielectric constant in the bi-layered gate insulator. As another new approach, the use of nanostructured channels is promising because the MIT sensitivity is highly responsive to sizes comparable in scale to the electronic phase domains, resulting in a dramatic resistance jump due to electronic avalanche effects<sup>28-30</sup>.

In this study, we report an enhanced on/off ratio by using epitaxial VO<sub>2</sub> nanowire-based FETs with a high-k Ta<sub>2</sub>O<sub>5</sub>/parylene hybrid solid gate insulator. In contrast to thin-film channels<sup>22</sup>, nanowire channels have superior sensitivity for transport modulation, resulting in an approximately ten-fold higher resistance modulation than that in thin-film channels. The enhancement in the resistance modulation is derived from expansion of metallic nano-frictions in an insulating matrix due to carrier accumulation driven by applying an electric field.

<sup>1</sup>Institute of Scientific and Industrial Research, Osaka Universit, Ibaraki, Osaka, 567-0047, Japan. <sup>2</sup>Faculty of Science, Kunming University of Science and Technology, Kunming, 650093, China. Correspondence and requests for materials should be addressed to T.K. (email: kanki@sanken.osaka-u.ac.jp) or H.T. (email: h-tanaka@sanken.osaka-u.ac.jp)

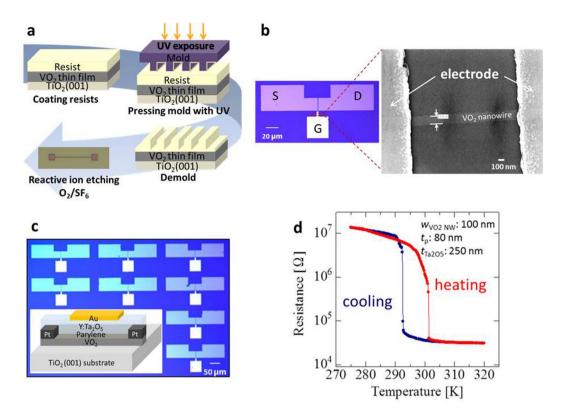

**Figure 1.** Device structure and characterization. (**a**)  $VO_2$  nanowire fabrication process using UV-NIL. (**b**) Representative  $VO_2$  nanowire-based field-effect transistor structure and morphology of the  $VO_2$  nanowires, as determined by scanning electron microscope (SEM). (**c**) Optical microscopy image of the  $VO_2$  nanowire-based FETs with a Y-doped Ta<sub>2</sub>O<sub>5</sub>/parylene hybrid gate dielectric; the inset shows a schematic illustration of the device structure. (**d**) Dependence of the resistance change on the temperature of an as-fabricated  $VO_2$  nanowire-based FET.

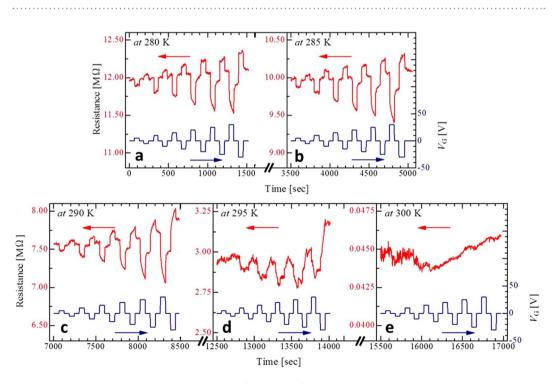

**Figure 2.** Resistance switching behaviour by applying a gate bias. (**a**–**e**) Resistance response versus gate bias in the VO<sub>2</sub> nanowire channel near  $T_{\rm MI}$  from 280 to 300 K.

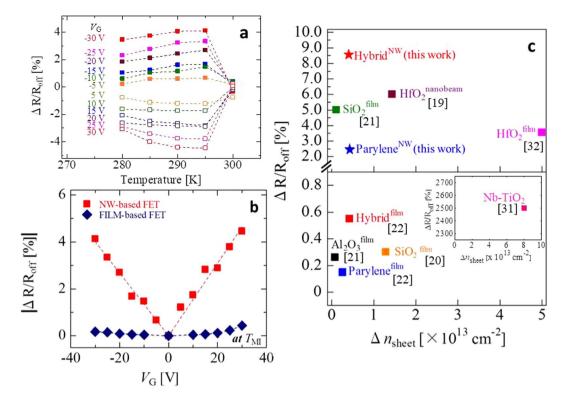

**Figure 3.** Resistive modulation ratio by an electric field in VO<sub>2</sub> nanowire and thin-film channels. (a) Resistance modulation efficiency as function of temperature at various gate biases applied in VO<sub>2</sub> nanowire channels. (b) Comparison of the absolute resistance modulation ratios for the nanowire-based and thin film-based FETs. (c) Comparison of studies of VO<sub>2</sub>-based FETs with various solid gate insulators from other papers, represented by the resistance modulation efficiency and induced sheet carrier density. The parylene-gated nanowire FET data are introduced in Fig. S5, Supplementary Information.

#### Results

Formation of VO<sub>2</sub> nanowire-based FET devices. This work begins with synthesis of epitaxial single-crystal VO<sub>2</sub> nanowires using the ultraviolet-nanoimprint lithography (UV-NIL) technique. The fabrication process is depicted in Fig. 1a. First, a resist is spin-coated onto epitaxial VO2 thin films, and then, a mold pattern containing nanowires is pressed into the resist under UV light. After a demolding process, the nanowire pattern is transcribed onto the VO<sub>2</sub> thin films. Subsequently, the nanowire patterns are formed by reactive ion etching (RIE). The image on the right in Fig. 1b shows a scanning electron microscope (SEM) image, which confirms the morphology with high precision. The electrode patterns shown in the image on the left in Fig. 1b were obtained by a conventional photolithography technique, and the size-controllable VO<sub>2</sub> nanowire-based FETs with 100- to 300-nm-wide and 8-nm-thick nanowires, as identified by atomic force microscopy (AFM), were manufactured over a large area (~200 devices on a single chip), as shown in Fig. 1c. Temperature-dependent resistance measurements were performed to investigate the MIT behaviour. The results are shown in Fig. 1d. An abrupt MIT as a function of temperature was achieved in all of the as-synthesized nanowire-based FETs with different nanowire widths, showing a different behaviour from that of film-based devices, which undergo a gradual MIT (see Fig. S1, Supplementary Information). This dramatic change in the nanowire resistance indicates the high MIT sensitivity to small temperature variations. In the typical device configuration, the VO<sub>2</sub> nanowire width is 100 nm, the parylene layer is 80 nm thick, and the overlay Y-doped Ta<sub>2</sub>O<sub>5</sub> layer is 250 nm thick. For comparison, we also fabricated VO<sub>2</sub> film-based FETs with similar hybrid gate insulator thicknesses. The fabrication of the film-based FETs was described in detail in our previous paper<sup>22</sup>.

**Resistance switching behaviour in VO<sub>2</sub> nanowire-based FET device.** To investigate transport modulation in the VO<sub>2</sub> nanowire channel, the resistance was measured under various applied gate biases ( $V_G = 0$  to  $\pm 30$  V at intervals of 5 V) as a function of time near the transition temperature ( $T_{\rm MI}$ ), as shown in Fig. 2a–e. Each resistance response cycle followed the same trend under various gate biases, including two main features: a flexible modulation in the channel resistance in response to the magnitude of the gate bias. Second, the resistance showed an abrupt drop and rise under positive and negative gate biases, respectively, from 280 K to 295 K in the insulating region. This behaviour is consistent with that of thin-film-based FETs<sup>22</sup> (see Fig. S2a–f in Supplementary Information). When the resistance modulation efficiency is defined as follows:

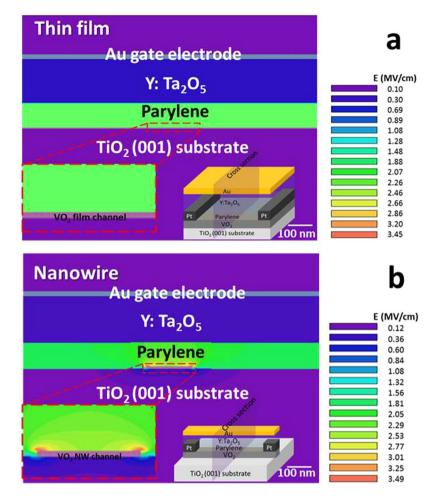

**Figure 4.** Electric field strength distribution. (a) and (b) Show the electric field distributions in the crosssections of the  $VO_2$  nanowire and thin-film channels, respectively. The insets show the simulated device structures.

$$\frac{\Delta R}{R_{off}} = \frac{R_{on} - R_{off}}{R_{off}} \times 100\%$$

<sup>(1)</sup>

where  $R_{on}$  and  $R_{off}$  are the resistances with and without a gate voltage, respectively,  $\Delta R/R_{off}$  is considerably enhanced in the VO<sub>2</sub> nanowire channels in comparison with that in the thin-film channels<sup>22</sup>. Figure 3a shows the summary of  $\Delta R/R_{\text{off}}$  estimated from Fig. 2a–e. The maximum resistance modulation ratio is approximately 8.58% at  $V_{\rm G} = \pm 30$  V just below the phase-transition temperature of 300 K in the heating process, defined as the point of maximum dR/dT, whose  $\Delta R/R_{off}$  is over 10-fold higher than that of film-based FETs, which is 0.61% (see Fig. S4 in Supplementary Information). When the temperature was varied from 280 K to 295 K, the  $\Delta R/R_{off}$  gradually increased under each given gate bias, but suddenly became almost zero at 300 K in the metallic state. Figure 3b shows  $|\Delta R/R_{off}|$  as a function of gate bias for the nanowire and film-based devices near the phase-transition temperature.  $\Delta R/R_{off}$  in the nanowire channel indicated greater sensitivity to increasing V<sub>G</sub> than that of the film-based FETs. We also plotted the resistance modulation efficiency for VO2-based FETs with the various gate dielectrics reported to date, as shown in Fig. 3c. On the horizontal axis, the sheet carrier number induced by the gate dielectric  $\Delta n_{\text{sheet}} = C_i V_G / e$ ), where Electric field strength distribution.<sub>i</sub> is the capacitance per unit area and e is the elemental charge, was selected as the conventional model because of performance comparison of various VO<sub>2</sub>-based FETs. Therefore, devices that have low  $\Delta R/R_{\text{off}}$  despite having high  $\Delta n_{\text{sheet}}$  imply the existence of multiple charge trap levels. Among the devices of this type, the  $VO_2$  nanowire-based FET with the hybrid gate dielectric exhibits the high resistance modulation, despite a low sheet carrier density of approximately  $5 \times 10^{12}$  cm<sup>-2</sup>, compared with other solid-state VO<sub>2</sub>-based FETs<sup>19-22</sup>. Efficient resistance modulation was thus realized in nanowire-based FETs with hybrid gate insulators, though T. Yajima et al.<sup>31</sup> reported the achievement of quite high resistance modulation due to carrier accumulation in non-conventional VO<sub>2</sub> FETs using a depletion layer gate between VO<sub>2</sub> and Nb-doped TiO<sub>2</sub>, as seen in the inset of Fig. 3c.

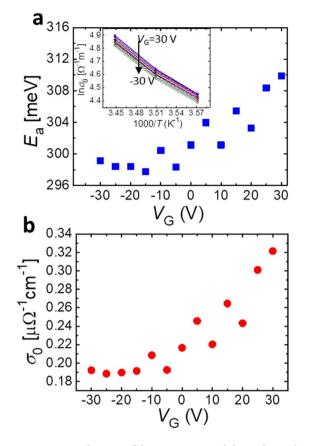

**Figure 5.** Mechanism of the resistance modulation by applying  $V_G$ . Plot of (**a**),  $E_a$  and (**b**),  $\sigma_0$  versus gate bias for the nanowire-based FETs with Y-doped Ta<sub>2</sub>O<sub>5</sub>/parylene hybrid gate dielectrics, where  $L = 2 \mu m$  and W = 100 nm in the nanowire channel. The inset of Fig. 5a shows 1/T dependence of  $\ln \sigma(T)$  with variety of  $V_G$  from -30 V to 30 V. Fittings by the least-square method were conducted to find the values of  $E_a$  and  $\sigma_0$ . All of the correlation coefficients  $|\mathbf{r}|^2$  of the fittings were over 0.99.

**Electric field strength analysis for the thin-film-based and nanowire-based devices.** To clarify the origin of the enhancement in the resistance modulation in nanowire-based FETs, we first analysed the electric field strength distributions for the thin film-based and nanowire-based FETs using the finite element method (FEM), and the results are shown in Fig. 4a and b, indicating distinct differences. The electric field was uniformly distributed on the thin-film channel surface, as shown in the magnified image in Fig. 4a. In contrast, the nanowire-channel field distribution showed an arc shape (see the magnified image in Fig. 4b), and the prevailing field converged on the edges. The electric field strength at the edge of the nanowire channel was enhanced 1.5-fold over that of the thin-film channel. However, this difference in the magnitude of the electric field cannot fully explain the experimental result of the 10-fold higher resistance modulation ratio for nanowire-based FETs. This therefore indicated that the dominant factor for enhanced resistance modulation is not a variation in the number of accumulated carriers by applying a gate bias.

**Mechanism of the resistance modulation by applying**  $V_{G}$ . To provide a reasonable explanation for the resistance modulation in VO<sub>2</sub> nanowire channels, we evaluated the activation energy for carrier hopping ( $E_a$ ) in an insulating state and the constant of transport conductivity ( $\sigma_0$ ) given by the following equation<sup>32,33</sup>.

$$\sigma(T) = \sigma_0 \exp\left(-\frac{E_a}{k_B T}\right),\tag{2}$$

where  $k_B$  is the Boltzmann constant. The natural logarithm conductance  $(\ln\sigma(T))$  from  $V_G = -30$  V to 30 V as a function of 1/T are shown in the inset of Fig. 5a. The  $E_a$  and  $\sigma_0$  were derived by their linear fittings. Figure 5a and b show the  $E_a$  and  $\sigma_0$  behavior as a function of  $V_G$ . In the positive  $V_G$ , the both of  $E_a$  and  $\sigma_0$  increase with increasing  $V_G$ . The change of  $\sigma_0$  means a change of coexistence state of inhomogeneity of metallic and thermally activated conductance in Si-based MOS-FET<sup>34</sup>. When this situation is applied to the VO<sub>2</sub>-based FET in this experiment, metallic nano-domains expand with increasing accumulated electron carriers due to applying positive  $V_G$ , especially at the edge part of VO<sub>2</sub> nanowire channel that an electric field converges as seen in Fig. 4b in a coexistent state of metallic and insulating phases near the  $T_{\rm MI}$ . Regarding the  $E_a$  behavior in the positive  $V_G$  region, the value increases approximately 12 meV from 298 meV to 310 meV, which is a factor of decrease in transport conductivity. However, influence of the increase in  $E_a$  is small near room temperature because thermal activation energy at

room temperature is approximately 30 meV, which is over 12 meV. Thus the main factor of decrease in resistance by positive  $V_{\rm G}$  is due to expansion of metallic nano-fractions by increasing  $\sigma_0$  in an insulating matrix. In the region of negative  $V_{\rm G}$ , the values of  $E_{\rm a}$  and  $\sigma_0$  are almost constant, meaning that the negative  $V_{\rm G}$  doesn't affect the activation energy and the coexistence state regardless of the increase in resistance as shown in Fig. 2 and Fig. 3a. Thus, the resistance enhancement by negative  $V_{\rm G}$  would be due to formation of depletion layer at the interface between VO<sub>2</sub> channels and gate insulating layers.

#### Discussion

In conclusion, superior resistance modulation sensitivity was obtained in  $VO_2$  nanowire-based FET devices by reducing the channel to the nanoscale (100 nm). Additionally, the maximum resistance modulation efficiency was observed near the transition temperature. We proposed that the enhanced resistance modulation of the nanowire channels was primarily due to the expansion of metallic nano-fractions in an insulating matrix especially at the edge parts of channel that an electric field converses. These results provide insight into the underlying properties of coexistence states of strongly correlated oxides and suggest possibilities for using nanoscale devices in high-performance next-generation electronics.

#### Methods

**Nanowire synthesis.** VO<sub>2</sub> nanowires were synthesized by nanoimprint photolithography (NIL), followed by the fabrication of epitaxial VO<sub>2</sub> thin films, which were grown on TiO<sub>2</sub> (001) single-crystal substrates by pulsed laser deposition using an ArF excimer laser at 450 °C under an oxygen pressure of 1.0 Pa. Oxygen reactive ion etching (RIE) was then performed at a power of 50 W, a pressure of 4 Pa, and a flow of 70 sccm for 150 s to remove the resist residue from the compressed regions. Subsequently, SF<sub>6</sub> gas was used for VO<sub>2</sub> etching (60 W, 1.0 Pa, 10 sccm, 10 s).

**Device fabrication.** VO<sub>2</sub> thin-film-based FETs were fabricated by the stencil mask method, as reported in the literature. Because the stencil mask approach is restricted to hundreds of microns, conventional photolithography was substituted for the stencil mask to form the standard three-terminal electrode pattern for nanowire-based FETs. Pt (20 nm)/Cr (5 nm) source and drain contacts were sputtered with 2 µm spacing. Subsequently, a hybrid gate insulator consisting of the high-*k* inorganic oxide Ta<sub>2</sub>O<sub>5</sub> and parylene organic polymer was fabricated, as reported in detail elsewhere<sup>27</sup>. A 50-nm-thick Au film was deposited as the gate electrode by electron-beam evaporation. The channel area overlap between the nanowires and the Au gate electrode was 100 nm × 2 µm.

**Measurements.** All electrical measurements were performed using an apparatus with a source measure unit (2635A, 236, Keithley), in which the attached Peltier-based sample stage was responsible for temperature control. Nitrogen gas was introduced to protect the VO<sub>2</sub> surface from humidity<sup>35</sup> and water<sup>36</sup>.

#### References

- Berglund, C. N. & Guggenheim, H. J. Electronic Properties of VO<sub>2</sub> near the Semiconductor-Metal Transition. *Phys. Rev.* 185, 1022 (1969).

- 2. Goodenough, J. B. The Two Components of the Crystallographic Transition in VO2. J. Solid State Chem. 3, 490 (1971).

- 3. Choi, H. S., Ahn, J. S., Jung, J. H. & Noh, T. W. Mid-infrared properties of a VO<sub>2</sub> film near the metal-insulator transition. *Phys. Rev.* B 54, 4621–4628 (1996).

- Pellegrino, L. et al. Multistate Memory Devices Based on Free-standing VO<sub>2</sub>/TiO<sub>2</sub> Microstructures Driven by Joule Self-Heating. Adv. Mater. 24, 2929–2934 (2012).

- 5. Bae., S.-H. *et al.* The Memristive Properties of a Single VO<sub>2</sub> Nanowire withSwitching Controlled by Self-Heating. *Adv. Mater.* **25**, 5098–5103 (2013).

- 6. Kanki, T., Kawatani, K., Takami, H. & Tanaka, H. Direct observation of giant metallic domain evolution driven by electric bias in VO<sub>2</sub> thin films on TiO<sub>2</sub>(001) substrate. *Appl. Phys. Lett.* **101**, 243118 (2012).

- 7. Fisher, B. Voltage oscillation in switching VO<sub>2</sub> needles. J. Appl. Phys. 49, 5339–5341 (1978).

- 8. Yoshiaki, T., Kato, F., Nitta, M. & Haradome, M. New Oscillation phenomena in VO2 crystals. Appl. Phys. Lett. 27, 212-214 (1975).

- 9. Shukla, N. et al. Synchronized charge oscillations in correlated electron systems. Sci. Rep. 4, 04964 (2014).

- Manca, N. *et al.* Programmable Mechanical Resonances in MEMS by Localized Joule Heating of Phase Change Materials. *Adv. Mater.* 25, 6430–6435 (2013).

- 11. Cheng, C. *et al.* Directly Metering Light Absorption and Heat Transfer in Singlee Nanowires Using Metal-Insulator Transition in VO<sub>2</sub>, Adv. *Optical Mater.* **3**, 336 (2015).

- Duchene, J., Terraillon, M., Pailly, P. & Adam, G. Fillamettary Conduction in VO<sub>2</sub> Coplaner Thin-Film Devices. *Appl. Phys. Lett.* 19, 115–117 (1971).

- Vitale, W. A. et al. Steep-Slope Metal-Insulator-Transition VO<sub>2</sub> Switches With Temperature-Stable High I<sub>ON</sub>. IEEE Electron Device Lett. 36, 972–974 (2015).

- Okimura, K. & Sakai, J. Time-dependent Characteristics of Electric Field-induced Metal–Insulator Transition of Planer VO<sub>2</sub>/c-Al<sub>2</sub>O<sub>3</sub> Structure. Jpn. J. Appl. Phys. 46, L813–L816 (2007).

- 15. Ahn, C. H., Triscon, J.-M. & Mannhart, J. Electric field effect in correlated oxide systems. Nature 424, 1015–1018 (2003).

- 16. Kim, H. T. *et al.* Mechanism and observation of Mott transition in VO<sub>2</sub>-based two- and Three-terminal devices. *New J. Phys.* **6**, 52 (2004).

- 17. Stefanovich, G., Pergament, A. & Stefanovich, D. Electrical switching and Mott transition in VO<sub>2</sub>. *J. Phys.: Condens. Mater* **12**, 8837–8845 (2000).

- 18. Hormoz, S. & Ramanathan, S. Limits on vanadium oxide Mott-metal-insulator transition field-effect transistors. *Solid-State Electronics* 54, 654–659 (2010).

- Sengupta, S. *et al.* Field-effect modulation of conductance in VO<sub>2</sub> nanobeam transistors with HfO<sub>2</sub> as the gate dielectric. *Appl. Phys. Lett.* 99, 062114 (2011).

- 20. Belyaev, M. A. *et al.* Field-effect modulation of resistance in VO<sub>2</sub> thin films at lower temperature. *Jpn. J. Appl. Phys.* **53**, 111102 (2014).

- 21. Ruzmetov, D., Gopalakrishnan, G., Ko, C., Narayanamurti, V. & Ramanathan, S. Three-terminal field effect devices utilizing thin films vanadium oxide as the channel layer. J. Appl. Phys. 107, 114516 (2010).

- Wei, T., Kanki, T., Fujiwara, K., Chikanari, M. & Tanaka, H. Electric field-induced transport modulation in VO<sub>2</sub> FETs with high-k oxide/organic parylene-C hybrid gate dielectric. *Appl. Phys. Lett.* 108, 053503 (2016).

- 23. Liu, K. et al. Dense Electron System from Gate-Controlled Surface Metal-Insulator Transition. Nano Lett. 12, 6272–6277 (2012).

- 24. Nakano, M. *et al.* Collective bulk carrier delocalization driven by electrostatic surface charge accumlation. *Nature* **487**, 459–462 (2012).

- 25. Jeong, J. et al. Science 339, 1402–1405 (2013).

- 26. Wei, T., Fujiwara, K., Kanki, T. & Tanaka, H. Impact of parylene-C thickness on performance of KTaO<sub>3</sub> field-effect transistors with high-*k* oxide/parylene-C hybrid gate dielectric. *J. Appl. Phys.* **119**, 034502 (2016).

- Eyvazov, A. B., Inoue, I. H., Stoliar, P., Rozenberg, M. J. & Panagopoulos, C. Enhanced and continuous electrostatic carrier doping on the SrTiO<sub>3</sub> surface. *Sci. Rep.* 3, 1721 (2013).

- Qazilbash, M. M. et al. Mott Transition in VO<sub>2</sub> Revealed by Infrared Spectroscopy and Nano-Imaging. Science 318, 1750–1753 (2007).

- 29. Takami, H., Kanki, T. & Tanaka, H. Multistep metal insulator transition in VO<sub>2</sub> nanowires on Al<sub>2</sub>O<sub>3</sub> (0001) substrates. *Appl. Phys. Lett.* **104**, 023104 (2014).

- Sharoni, A., Ramírez, J. G. & Schuller, I. K. Multiple Avalanches across the Metal-Insulator Transition of Vanadium Oxide Nanoscaled Junctions. *Phys. Rev. Lett.* 101, 026404 (2008).

- Yajima, T., Nishimura, T. & Toriumi, A. Positive-bias gate controlled metal-insulator transition in ultration VO<sub>2</sub> channels with TiO<sub>2</sub> gate dielectrics. *Nat. Commun.* 6, 10104 (2015).

- Martens, K. et al. Field Effect and Strongly Localized Carriers in the Metal-Insulator Transition Material VO<sub>2</sub>. Phys. Rev. Lett. 115, 196401 (2015).

- 33. Kawasugi, Y. *et al.* Field-Induced Carrier Delocalization in the Strain-Induced Mott Insulating State of an Organic Superconductor. *Phys. Rev. Lett.* **103**, 116801 (2009).

- 34. Arnold, E. Disorder-induced carrier localization in silicon surface inversion layers. Appl. Phys. Lett. 25, 705-708 (1974).

- Sasaki, T., Ueda, H., Kanki, T. & Tanaka, H. Electrochemical gating-induced reversible and drastic resistance switching in VO<sub>2</sub> nanowires. Sci. Rep. 5, 17080 (2015).

- Ji, H., Wei, J. & Natelson, D. Modulation of the Electrical Properties of VO<sub>2</sub> Nanobeams Using an Ionic Liquid as a Gating Medium. Nano Lett. 12, 2988–2992 (2012).

#### Acknowledgements

The authors gratefully thank Mr. S. Sakakihara for his assistance in the reactive ion etching of the nanowires. This work was supported by a Grant-in-Aid for Scientific Research A (No. 17H01054) and a Grant-in-Aid for Scientific Research B (No. 16H03871) from the Japan Society for the Promotion of Science (JSPS). Part of this work was also supported by "Nanotechnology Platform Project (Nanotechnology Open Facilities in Osaka University)" of MEXT, Japan [S-16-OS-0012 and F-16-OS-0016]. This work was performed under the Cooperative Research Program of "Network Joint Research Center for Materials and Devices".

#### **Author Contributions**

T.K. and H.T. conceived the experiment. T.W. and M.C. fabricated and characterized the devices. U.T. and T.S. prepared the insulating parylene materials. T.K. designed and provided support in the fabrication, evaluation and set up of the measurement system. T.W. wrote the manuscript with help of H.T. and T.K. All authors discussed the results and commented on the manuscript.

### Additional Information

Supplementary information accompanies this paper at https://doi.org/10.1038/s41598-017-17468-x.

Competing Interests: The authors declare that they have no competing interests.

**Publisher's note:** Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

**Open Access** This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/.

© The Author(s) 2017