Abstract

Junction-less nanowire transistors are being investigated to solve short channel effects in future CMOS technology. Here we demonstrate 8 nm diameter silicon nanowire junction-less transistors with metallic doping densities which demonstrate clear 1D electronic transport characteristics. The 1D regime allows excellent gate modulation with near ideal subthreshold slopes, on- to off-current ratios above 108 and high on-currents at room temperature. Universal conductance scaling as a function of voltage and temperature similar to previous reports of Luttinger liquids and Coulomb gap behaviour at low temperatures suggests that many body effects including electron-electron interactions are important in describing the electronic transport. This suggests that modelling of such nanowire devices will require 1D models which include many body interactions to accurately simulate the electronic transport to optimise the technology but also suggest that 1D effects could be used to enhance future transistor performance.

Similar content being viewed by others

Introduction

Complementary metal-oxide semiconductor (CMOS) transistor technology is the mainstay of electronics. The scaling of the technology to dimensions below ~45 nm where short channel effects start to become significant has required significant changes to the simple planar two-dimensional (2D) metal-oxide semiconductor field effect transistor (MOSFET)1. FinFET, double gate and/or fully-depleted approaches have been required for the 22 nm technology node to improve the electrostatic depletion of the transistor channel to improve the off-current, Ioff whilst future scaling beyond the 10 nm technology node is predicted to require nanowire technology2 to improve the electrostatic control further3. Si nanowires have a multitude of potential applications beyond replacing CMOS transistors2, 4 which include semiconductor memories5, photovoltaics6, thermoelectric generators7, biosensors8, colour selective photodetectors9 and qubits10. Cryogenic CMOS is a recently developing area especially for quantum simulators or computing where it is clear that control electronics must operate at 4.2 K or less in dilution refrigerators to be able to control qubits10 and readout electronics11. The low temperature behaviour of transistors is therefore also becoming important for a few niche applications in research.

Most nanowire transistor designs to date rely on the formation of junctions between the heavily doped source and drain contacts and the undoped quasi-one-dimensional (1D) channel. Theoretical12 and experimental studies13 have shown that atomic-scale variations in the doping profile can lead to drastic variability in transistor behaviour. The need for ultrasharp source and drain junctions, however, imposes severe constraints on doping techniques and the processing thermal budget. Junction-less nanowire transistors4 do not suffer from these limitations, and can be fabricated without the need for ultrafast annealing techniques.

While the junction-less transistor was first envisioned by Lilienfield14 in 1925, working devices only became possible with the advent of silicon-on-insulator (SOI) technology. Junction-less transistors require high doping (ideally >1 × 1019 atoms cm−3) to ensure a high current drive and to minimize contact resistance. In 3D devices, however, such high doping makes it impossible to fully deplete the channel of charge carriers because of electrostatic screening of the gate electric field and so the highest currents cannot be realised. Screening is modified in 2D and 1D allowing the device channels to be fully depleted. For 1D nanowires only electrons external to the nanowire can screen the Coulomb potential15 which enables the complete pinch-off of the channel which is necessary to turn the device off even for doping concentrations well above the Mott metal-insulator transition16.

In this Letter we investigate the influence of dimensionality in electrostatic screening as well as in charge transport in the nanowire transistor and demonstrate a number of clear signatures of 1D electronic behaviour. In particular, we will focus on the universal conductance scaling behaviour for low bias voltages. Such universal conductance scaling has been previously observed in single walled carbon nanotubes17, Li0.9Mo6O17 18 and metallic nanowires19, and is indicative for 1D charge transport. Low temperature transport also demonstrates clear Coulomb gap behaviour indicative of significant many body electron-electron interactions. Many simulations of junction-less transistors to date use 3D or 2D models20,21,22,23 to describe the electronic transport and to optimise the devices. We demonstrate that 1D transport models with many body interactions must be used to accurately describe the present devices when the nanowire diameters become less than the key electron transport length scales.

Results

Junction-less transistor behaviour

Figure 1 present a transmission electron microscope (TEM) image of the smallest nanowire with 8 ± 0.5 nm diameter along with a scanning electron microscope (SEM) lateral image demonstrating the gate overlapping the nanowire and the source and drain contact regions. Whilst the Al gate is much longer than the 150 nm long nanowire, the physical gate-length of the transistor will be determined by the nanowire length as the large source and drain sections are not depleted out by the gate (see Fig. 2). The nanowires for this work were implanted using P and previous measurements on sub-10 nm nanowires in Hall bar geometry devices at T = 1.4 K5, 24 have indicated an activated carrier density of 9.8 × 1018 cm−3. This is significantly above the Mott criterion of 3.5 × 1018 cm−3 indicating that the material is degenerately doped and should demonstrate metallic behaviour at all temperatures16.

3D to 1D dimensional transport change with nanowire diameter. The drain current, I D as a function of gate voltage for Si nanowires with three different diameters of 8 nm, 16 nm and 24 nm. The drain voltage, V D = 1.5 V and all measurements are at 293 K. The insert is an elemental map of a cross-section of the smallest nanowire, measured by TEM-EELS, which was used to determine the nanowire diameter.

First, we investigate the current–voltage behaviour of our junction-less transistors. We find that the devices with an 8 nm channel diameter behave nearly identically to a conventional MOSFET at 300 K, whereas the devices with larger channel diameters (16 ± 0.5 nm and 24 ± 0.5 nm) behave more like bulk, metallic conductors. Figure 2 demonstrates the drain current, I d , versus gate voltage, V g , for a drain voltage, V D of + 1.5 V. The I off is below the detection limit of the measurement setup (0.1 pA), and the on-current, I on to I off ratio between V g = −0.5 V and V g = +0.5 V is 1 × 108, which clearly demonstrates the electrostatic depletion of charge carriers in the 8 nm diameter channel. By contrast, the same I on /I off ratios for the 16 nm and 24 nm channels are only 10 and 2, respectively.

The subthreshold slope (SS), which is defined as the inverse of the slope of the log of the drain current versus gate voltage below threshold is 66 mV dec−1 for the 8 nm channel. The sharpness of the on-off switching ratio for these devices is close to the theoretical lower limit of SS = (k B T/q)ln(10), which corresponds to 60 mV dec−1 at T = 300 K, and is nearly equal to the best SOI trigate transistors25 with SS values of 63 mV dec−1. For the larger diameter channels, the subthreshold slope increases to 570 mV/dec for the 16 nm diameter nanowire and >12000 mV/dec for the 24 nm diameter nanowire. All the nanowire devices for all diameters demonstrate high I on values (all >10 μA at 1.0 V). Setting the off-current, I off at 100 nA/μm gate width with a gate overdrive of 1.0 V produces an I on of 1.15 mA/μm which compares favourably to 0.61 mA/μm measured previously from 25 nm gate-length Si MOSFETs26 and the 0.62 mA/μm measured from 50 nm gate-length InGaAs MOSFETs27. The nanowire current has been divided by the diameter to achieve the current per unit gate width since as will be demonstrated later, the Fermi wavelength is significantly larger than the nanowire diameter indicating the electron wavefunctions completely fill the diameter of the nanowire. Higher voltages provide even higher performance: for example, I off at 10 pA/μm with a gate overdrive of 1.8 V, the present 150 nm gate-length nanowires have 2.52 mA/μm drain current. This is significantly higher than the 0.92 mA/μm from 80 nm gate-length high-voltage 3D tri-gate MOSFETs from a 22 nm system on chip commercial technology25.

Discussion

The strong dependence of the current–voltage behaviour on the channel diameter suggests a dimensionality transition from 1D to 3D electronic transport behaviour between the 8 nm and 24 nm channels. Using a 3D carrier density N 3D = 9.8 × 1018 cm−3, we estimate the mean free path from elastic scattering as \(\ell =2\pi \hslash {n}_{{\rm{1D}}}/{g}_{s}{g}_{v}q\) = 1.4 nm, where n 1D = N 3D 1/3. g s = 2 and g v = 2 are the spin- and valley-degeneracies. The Fermi wavelength λ F = g s g v /n 1D = 18.7 nm at 300 K, indicating that a transition takes place from diffusive 1D transport in the 8 nm diameter channels to diffusive 3D transport in the 24 nm nanowires. It is clear that the electrostatic screening of the Coulomb potential in 3D limits the ability of the gate in the widest nanowires to deplete the channel resulting in poor modulation (I on to I off ratio) and poor I off . In the 1D regime, as determined by the nanowire diameter becoming smaller than the λ F , the electrons in the 1D channel cannot screen the Coulomb potential from the gate and excellent gate modulation can be achieved. This is therefore the first piece of evidence suggesting that the electron transport in the 8 nm diameter nanowires could be 1D.

In clean, high-mobility 1D channels where \(\ell \) is much longer than the gate-length, ballistic quantised current behaviour is expected28, 29. Clean channels can also demonstrate Luttinger liquid behaviour17 where electron and spin transport can be independent30, 31. The high, metallic doping levels in the present nanowires provide too much scattering to expect these types of 1D transport signatures and diffusive transport is to be expected from the spacing of the dopants and \(\ell \). Dirty 1D transport signatures with diffusive transport dominating include universal conductance scaling17, 19, Coulomb gaps32, Coulomb blockade33, 34, zero bias anomalies35 or for very dirty materials hopping conduction36.

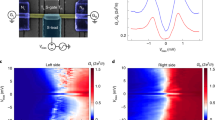

Universal conductance scaling

We will now discuss the universal conductance scaling observed in the 8 nm diameter nanowire transistors at low drain bias voltages, V D . Figure 3a demonstrates the source-drain current as a function of gate voltage measured at 300 K and at 14 K. We determine the threshold voltage V th ≈−0.75 V from the room temperature I − V g trace (see Supplementary Information) and V th ≈−0.25 V from the 14 K trace. At 14 K the sub-threshold transport is dominated by single-electron transport33, 37, resulting in distinct Coulomb blockade peaks in the low-temperature I − V g trace that are particularly pronounced below V g = −1 V (Fig. 3a). The Coulomb oscillations in the sub-threshold transport are due to the transistor channel breaking up into one or more charge islands that are tunnel coupled to the source and drain electrodes38. The formation of these islands may either be due to disorder within the channel, e.g. surface roughness or random dopant fluctuations, or due to strain or confinement induced tunnel barriers at the extremities of the transistor channel. Previous studies of PADOX-fabricated silicon single-electron transistors39 have shown that strain may lead to tunnel barriers of at least 150 meV. Similarly, additional confinement potentials in constrictions, resulting from parasitic overexposure in the corners of the channel and the source/drain leads during the electron-beam lithography process, may give rise to tunnel barriers.

Universal conductance scaling. (a) The drain current versus gate voltage measured in the high-temperature (T = 300 K) and low-temperature (T = 14 K) regimes. In the low-temperature regime Coulomb blockade oscillations can be observed below the threshold voltage V th ≈ − 0.25 V. (b) Room temperature current versus drain voltage (I − V b ) traces are measured as a function of gate voltage. The I − V D traces exhibit the typical transistor behaviour where the current I ∝ (V g − V th)V D − V D 2/2 in the linear region (V D < V g − V th) and weakly dependent on V D in the saturation region (V D ≥ V g − V th). (c) The normalized conductance (to 300 K) versus drain voltage as a function of temperature. There is a temperature dependent suppression of the conductance around zero bias which is superimposed onto the voltage dependent conductance. Normalizing the conductance by dividing it by the room temperature conductance results in a symmetric conductance gap centred around zero drain bias. (d) The normalized conductance versus drain bias voltage as a function of gate voltage. With increasing gate voltage, and carrier density, the conductance gap around zero drain bias gets softer, indicating enhanced screening of the Coulomb interaction between localized electrons. (e) A universal scaling plot of the conductance data, using a T-renormalized energy scale qV D /k B T as described in Supplementary Information section I. All conductance traces for each gate voltage coincide, showing universal conductance scaling over a large gate range. The curves are scaled for each gate voltage and offset for clarity.

Above the threshold voltage, no Coulomb blockade oscillations are observed and the current at room temperature and 14 K approach the same value, indicating open-channel transport. It is in this open-channel transport regime that we will investigate universal conductance scaling. Figure 3b demonstrates I − V b traces measured as a function of the gate voltage at 300 K. The I − V b traces exhibit the characteristic linear behaviour for V D < V g − V th and saturation behaviour for V D ≥ V g − V th. In the linear regime the current I ∝ (V g − V th)V D − V D 2/2, and therefore the differential conductance G = dI/dV is proportional to −V D for low bias voltages. Since any suppression of the differential conductance will thus be superimposed onto a linear dependence on V D , we normalize the differential conductance by dividing it by the room temperature conductance \(\tilde{G}(V,T)=G(V,T)/G(V,T=300\,{\rm{K}})\). The normalized conductance as a function of drain bias voltage is presented in Fig. 3c for temperatures ranging from 14 K to 300 K, and in Fig. 3d for gate voltages ranging from −0.25 to 2 V. We estimate this approach to produce less than 10% uncertainty in the normalised conductance across the gap but larger uncertainty outside the gap.

At low temperatures there is a symmetric dip in the normalized conductance centred around zero drain bias, which reduces in depth and increases in width with increasing temperature (see Fig. 3c). Theoretical studies investigating the transition from ballistic to diffusive transport in quasi-1D conductors have attributed the occurrence of a zero-bias anomaly in these systems to electron-electron interactions which in dirty systems can lead to weak localization35, 40, 41 (we will demonstrate later that no weak localization is observed in the electron transport behaviour of the 8 nm diameter nanowires). These studies further predict that the characteristic energy of this Coulomb gap, determining both the width and the depth of the zero-bias dip, is inversely proportional to the number of channels N in the quantum wire. As we increase the gate voltage applied to our nanowire transistor (Fig. 3d), thereby increasing N, we observe a decrease in the conductance suppression around zero bias, in agreement with these predictions.

The universal conductance scaling is illustrated in Fig. 3e, which demonstrates the scaled normalized conductance traces \(\tilde{G}(V,T)/\tilde{G}(V\,\mathrm{=}\,0{\rm{V}},T)\) for each gate voltage plotted on a log-log scale as a function of the temperature-renormalized energy scale qV D /k B T. To demonstrate that all traces measured for a particular gate voltage coincide, the vertical axis of all traces measured at each gate voltage have been scaled and offset by the same value (see Supplementary Information). The log-log plots in Fig. 3e demonstrate two distinct regions: (i) for \(q{V}_{D}\ll {k}_{B}T\), where the conductance is constant; and (ii) for \(q{V}_{D}\gg {k}_{B}T\), where the conductance follows a power-law dependence as a function of the T-renormalized energy scale. Similar universal scaling behaviour as shown in Fig. 3e has previously been observed in quasi-1D conductors, including multi-walled carbon nanotubes17, Li0.9Mo6O17 18 and metallic nanowires19. From the slope of the log-log plots for \(q{V}_{D}\gg {k}_{B}T\) we estimate the exponent α = 2/g − 2, where the Luttinger g-parameter42 defines the type of transport in 1D systems. For non-interacting fermions g = 1 and electronic transport should give Ohmic conductance42, i.e. the current or conductance should be linear with the voltage. Figure 4 presents the voltage exponent and Luttinger g-parameter as a function of gate voltage. For positive gate voltages g approaches 1 as the conductor becomes metallic. For negative gate voltages, g decreases as the carrier density decreases. The Luttinger parameter is given by Kane and Fischer42 for a single channel as

with the Fermi energy

where m * is the effective mass for the conduction band of silicon (0.19 m 0 with m 0 the free electron mass for conduction parallel to the (100) planes43) and L e = n 1D −1 is the spacing between the electrons. At a gate voltage −0.25 V we find g ≈ 0.55, hence we can estimate the carrier concentration from the above equations to be n 1D ≈ 6.7 × 106 cm−1. If we use the V g = −0.25 data from Fig. 3b at V D = 1.5 V which was used to obtain g ≈ 0.55 with the low-field mobility, μ extracted from these channels23 of 107 cm2/Vs and consider the channel of radius R = 4 nm and length, L = 150 nm as a resistor then \({n}_{1D}={(\frac{{I}_{D}L}{q\mu \pi {R}^{2}{V}_{D}})}^{\frac{1}{3}}\). The extracted carrier density from this equation is 1.62 × 106 cm−1. This is 4.1 times smaller than the value obtained from the single channel approach of Kane and Fischer42 suggesting that the nanowire may be a multi-channel conductor. Indeed 4 is the combined spin and valley degeneracy for the conduction band of silicon and if these degeneracies are added to the electron spacing by replacing L e with g s g v L e in equation 1 then the extracted density from the Kane model agrees with the experimental density. When the nanowire transistor is switched on, the saturation current regime is clearly Ohmic from the results in Fig. 4 with \(g\sim 1\). As the transistor is switched off, the Luttinger parameters of g < 1 in the subthreshold region of Fig. 4 have been associated to 1D Luttinger liquid transport with long-range Coulomb interactions in carbon nanotubes17.

Temperature dependence

Finally, we investigate the temperature dependence of the zero-bias conductance measured for V g = 0 V. At this gate voltage, the high-bias current does not have a Richardson like \({T}^{2}\exp (-\frac{W}{{k}_{B}T})\) dependence where W is the energy of the thermionic barrier height, allowing us to exclude any thermionic contributions to the zero-bias temperature dependence. Figure 5 demonstrates the zero-bias conductance measured as a function of temperature.

The temperature dependence for 1D transport The measured conductance at zero bias voltage and zero gate voltage as a function of temperature. The ‘best’ fit to the data (solid red line) gives a value n = 0.6 ± 0.2. A plot of the multi-channel Luttinger theory with n = 0.5 is also presented. The extracted transition temperature T = 13 ± 6 K is just below our measurement range, and does therefore not allow us to observe the onset of a Thouless crossover into the strong localization regime at low temperature. The grey shaded area indicates the bounds from excitation to the mobility edge or nearest neighbour hopping (NNH)44 to 3D variable range hoping45.

To understand Fig. 5, we need to consider a number of the length scales of the electron transport in the nanowire. As previously shown, λ F ranges from 18.7 nm at 1.4 K to 20.4 nm at 300 K so the electron wavefunctions completely fill the whole of the nanowire providing 1D transport for the electrical current along the nanowire for all temperatures investigated. This therefore justifies using the diameter of the nanowire as the gate width when calculating the drain current per μm of gatewidth.

The length scale for electron-electron interactions is the thermal length which results from the randomisation of the phase of an electron around the Fermi distribution from thermal smearing which produces an energy uncertainty of k B T where k B is Boltzmann’s constant. The thermal length is defined as \({L}_{T}=\sqrt{\frac{D\hslash }{{k}_{B}T}}\) where D is the diffusion constant (\(=\frac{1}{2}{v}_{F}^{2}\tau \) with the Fermi velocity, v F and the momentum relaxation time, τ). For the 8 nm Si nanowires and using the mobility extracted from I D of 107 cm2/Vs and the extracted 1D density at V g = −0.25 V of 1.62 × 106 cm−1 ≡ 4.2 × 1018 cm−3, L T is 32.5 nm at 1.4 K and decreases to 1.8 nm at 300 K. The cross over point from 1D electron-electron interactions to 3D corresponds to 17 K when L T equals the nanowire diameter of 8 nm.

The best fit to the data in Fig. 5 produces

with a temperature exponent of n = 0.6 ± 0.2 and the extracted transition temperature, T 0 = 13 ± 6 K. There are no theories with n = 0.6 but there are a number of theories with n = 0.5 which is within the experimental uncertainty32, 35, 36, 46. Weak localisation due to the Altshuler and Aronov corrections46 produce a \({T}^{-\frac{1}{2}}\) temperature dependence in both 1D and 3D which clearly does not fit the data. In the variable range hopping transport regime, the exponent is \(n=\frac{1}{1+d}\) where d is the dimension. For 1D variable range hopping the exponent is therefore \(n=\frac{1}{2}\) but since the transition temperature is given by \({T}_{0}=\frac{4}{{a}_{B}^{\ast }{k}_{B}g({E}_{F})}\) where \({a}_{B}^{\ast }=2.3\,{\rm{nm}}\) is the effective Bohr radius and g(E F ) = 5.7 × 1028 is the density of states at the Fermi level, E F = 16.2 meV this produces T 0 = 2160 K and clearly does not fit the data. Since the zero-bias anomaly suggests a Coulomb gap in the density of states, variable range hopping with a Coulomb gap also has a temperature exponent of \({T}^{-\frac{1}{2}}\) universally for all dimensions32, 36. The theoretical value of \({T}_{0}=\frac{2.8{q}^{2}}{4\pi {\varepsilon }_{0}{\varepsilon }_{0}{a}_{B}^{\ast }{k}_{B}}\) = 1679 K, however, and so again this model36 does not fit the data either.

A clean, single channel Luttinger liquid is predicted to have a T α where α is related to the the many body interactions in the system17. Whilst this clean Luttinger liquid model does not fit the present nanowire data, Mischenko et al.35 have developed a multi-channel Luttinger liquid model for disordered nanowires which produces a temperature behaviour for the electrical conductivity identical to equation 3 with n = 0.5 temperature exponent and the model does fit the present data within experimental uncertainty and produces the number of channels to be 3.9 ± 0.9 so approximately 4. This model has been plotted in Fig. 5 as the n = 0.5 model and it is the only model that fits the data and produces fit parameters in agreement with the theoretical predictions of any of the tested models. As the conduction band of silicon has a spin degeneracy of 2 and a valley degeneracy of 2, it would suggest that the 4 channels in the silicon nanowire are just related to the spin and valley degeneracy. Whilst separation of spin and charge transport is the unique signature of Luttinger liquid behaviour in 1D nanowire systems30, 31, which is beyond our present experiments, the disordered multi-channel Luttinger liquid model provides the best fit to the present data. It has been suggested that silicon nanowires with widths around 3 nm will have the valley degeneracy lifted47. Therefore the scaling to smaller nanowire widths should result in changes to both g and α which would provide further proof of the Luttinger liquid behaviour but this is beyond the scope of the present work.

To conclude, clear 1D electron transport consistent with the experimentally determined Fermi wavelength, thermal length, zero-bias anomaly and a disordered multi-channel Luttinger liquid model behaviour are observed in the 8 nm diameter Si nanowires at low temperatures. Observation of universal scaling curves and an exponential temperature dependent electrical conductance with a \(n=\frac{1}{2}\) exponent also provide strong evidence for 1D behaviour up to room temperature. The Fermi wavelength indicates that the wavefunctions completely fill the diameter of the nanowire for all temperatures tested demonstrating quasi-1D transport even at room temperature and the electron-electron interactions in the nanowire are 1D for temperatures below 17 K. These results indicate that accurate modelling of such nanowires for future CMOS or quantum electronics will require 1D models which include many body interactions as the experimentally observed electron transport cannot be explained by the presently used 3D theories. This also opens up the possibility of deliberately using 1D effects to enhance transistor performance in future CMOS technologies.

Methods

Fabrication

The devices were fabricated from 55 nm SOI wafers from SOITEC with a 145 nm buried oxide which were implanted with P at 15 keV with a dose of 4 × 1014 cm−2 before being annealled at 950 °C for 90 seconds. The top Si was then etched to reduce the thickness for the smallest dimension nanowires before a Vistec VB6 electron beam lithography tool was used to pattern the nanowire using hydrogen silsesquioxane (HSQ) resist. A low damage SF6/C4F8 inductivity coupled plasma etch was undertaken48 before the resist was stripped and a thermal oxide was grown at 950 °C. Optical lithography was then used to define electrical contacts using 20 nm of Ni and 50 nm of Pt after the oxide had been stripped with HF. An anneal in forming gas at 380 °C for 15 minutes was used to alloy the contacts forming a NiSi Ohmic contact with a specific contact resistance of 0.8 Ω-mm. Finally, electron beam lithography was used with 400 nm of PMMA resist to lift-off the Al gate.

Measurement

The dc current-voltage characteristics for Fig. 2 were measured using an Agilent B1500 semiconductor parameter analyser at room temperature (293 K) with a Cascade Microtech probe station with a noise floor of ≈0.1 pA and V D = 1.5 V. The data for Figs 3, 4 and 5 were also obtained by dc techniques using the Agilent B1500 but with a Lakeshore CRX-6.5K Cryogenic Probe station with a higher noise floor of ≈1 pA. The original electrical dataset from the nanowires analysed in this paper are avalable at http://eprints.gla.ac.uk/140323/7/140323Suppl.xlsx.

TEM analysis

Samples were prepared for TEM analysis using standard ‘lift-out’ procedures on a FEI Nova Dualbeam Focused Ion Beam system. TEM and STEM were conducted on a JEOL ARM200cF instrument equipped with a cold field emission gun that was operated at 200 kV and a CEOS (probe) aberration corrector. EELS data were collected using a Gatan 965 Quantum ER spectrometer using the Dual EELS49 and Spectrum Imaging50 methodologies. Energy dispersive x-ray spectroscopy (EDS) was conducted simultaneously using a Bruker XFlash detector.

References

International Technology Roadmap for Semiconductors. http://www.itrs2.net/itrs-reports.html (2013).

Appenzeller, J. et al. Toward nanowire electronics. IEEE Trans. Elec. Dev. 55, 2827–2845 (2008).

Kuhn, K. J. Considerations for ultimate CMOS scaling. IEEE Trans. Elec. Dev. 59, 1813–1828 (2012).

Colinge, J.-P. et al. Nanowire transistors without junctions. Nature Nano. 5, 225–229 (2010).

Busche, C. et al. Design and fabrication of memory devices based on nanoscale polyoxometalate clusters. Nature 515, 545–549 (2014).

Tian, B. et al. Coaxial silicon nanowires as solar cells and nanoelectronic power sources. Nature 449, 885–889 (2007).

Boukai, A. I. et al. Silicon nanowires as efficient thermoelectric materials. Nature 451, 168–171 (2008).

Zheng, G., Patolsky, F., Cui, Y., Wang, W. U. & Lieber, C. M. Multiplexed electrical detection of cancer markers with nanowire sensor arrays. Nature Biotech. 23, 1294–1301 (2005).

Park, H. et al. Filter-free image sensor pixels comprising silicon nanowires with selective colour absorption. Nano Lett. 14, 1804–1809 (2014).

Nadj-Perge, S., Frolov, S. M., Bakkers, E. P. A. M. & Kouwenhoven, L. P. Spin-orbit qubit in a semiconductor nanowire. Nature 468, 1084–1087 (2010).

Das, K., Lehmann, T. & Dzurak, A. S. Sub-Nanoampere One-Shot Single Electron Transistor Readout Electrometry Below 10 Kelvin. IEEE Trans. Circuits Systems I 61, 2816–2824 (2014).

Asenov, A. Random dopant induced threshold voltage lowering and fluctuations in sub-0.1 μm MOSFETs: A 3-D atomistic simulation study. IEEE Trans. Elec. Dev. 45, 2505–2513 (1998).

Kuhn, K. J. et al. Process technology variation. IEEE Trans. Elec. Dev. 58, 2197–2208 (2011).

Lilienfield, J. E. Method and apparatus for controlling electrical current. Tech. rep., US patent (1925).

Giamarchi, G. Quantum Physics in One Dimension (OUP, 2003).

Edwards, P. P. & Sienko, M. J. Universality aspects of the metal-nonmetal transition in condensed media. Phys. Rev. B 17, 2575–2581 (1978).

Bockrath, M. et al. Luttinger-liquid behaviour in carbon nanotubes. Nature 397, 598–601 (1999).

Hager, J. et al. Non-Fermi-liquid behaviour in quasi-one-dimensional Li0.9Mo6O17. Phys. Rev. Lett. 95, 186402 (2005).

Yan, H. et al. Zero-bias anomaly in one-dimensional ultrathin metallic nanowires. AIP Advances 2 (2012).

Trevisoli, R. D. et al. Surface-potential-based drain current analytical model for triple-gate junctionless nanowire transistors. IEEE Trans. Elec. Dev. 59, 3510–3518 (2012).

Moon, D.-I., Choi, S.-J., Duarte, J. & Choi, Y.-K. Investigation of silicon nanowire gate-all-around junctionless transistors built on a bulk substrate. Electron Devices, IEEE Transactions on 60, 1355–1360 (2013).

Jhan, Y., Thirunavukkarasu, V., Wang, C. & Wu, Y. Performance evaluation of silicon and germanium ultrathin body (1 nm) junctionless field-effect transistor with ultrashort gate length (1 nm and 3 nm). IEEE Elec. Dev. Letts. 36, 654–656 (2015).

Georgiev, V. P. et al. Experimental and simulation study of 1D silicon nanowire transistors using heavily doped channels (2017). IEEE Trans. Nanotechnol. (Accepted for Publication).

Mirza, M. M. et al. Determining the electronic performance limitations in top-down-fabricated Si nanowires with mean widths down to 4 nm. Nano Lett. 14, 6056–6060 (2014).

Jan, C.-H. et al. A 22 nm SoC platform technology featuring 3-D tri-gate and high-k/metal gate, optimized for ultra low power, high performance and high density SoC applications. Proc. IEDM 12, 44–47 (2012).

Majumdar, A. et al. Room-temperature carrier transport in high-performance short-channel silicon nanowire MOSFETs. Proc. IEDM 12, 179–183 (2012).

Gu, J. J. et al. First experimental demonstration of gate-all-around III-V MOSFETs by top-down approach. Proc. IEDM 11, 769–773 (2011).

Wharam, D. A. et al. One-dimensional transport and the quantisation of the ballistic resistance. J. Physics C: Solid State Physics 21, L209 (1988).

van Wees, B. J. et al. Quantized conductance of point contacts in a two-dimensional electron gas. Phys. Rev. Lett. 60, 848–850 (1988).

Auslaender, O. M. et al. Spin-Charge separation and localization in one dimension. Science 308, 88–92 (2005).

Jompol, Y. et al. Probing spin-charge separation in a Tomonaga-Luttinger liquid. Science 325, 597–601 (2009).

Efros, A. L. & Shklovskii, B. I. Coulomb interaction in disordered systems with localised electronic states. In Electron-electron Interactions in Disordered Systems (eds Efros, A. L. & Pollak, M.), vol. 10 (North Holland, 1985).

Paul, D. J., Cleaver, J. R. A., Ahmed, H. & Whall, T. E. Coulomb blockade in silicon based structures at temperatures up to 50 K. Appl. Phys. Lett. 63, 631–632 (1993).

Paul, D. J., Cleaver, J. R. A., Ahmed, H. & Whall, T. E. Cotunneling of holes in silicon-based structures. Phys. Rev. B 49, 16514–16517 (1994).

Mishchenko, E. G., Andreev, A. V. & Glazman, L. I. Zero-Bias Anomaly in Disordered Wires. Phys. Rev. Lett. 87, 246801 (2001).

Efros, A. L., Lien, N. V. & Shklovskii, B. I. Variable range hopping in doped crystalline semiconductors. Solid State Comm. 32, 851–854 (1979).

Zwanenburg, F. A. et al. Silicon quantum electronics. Rev. Mod. Phys. 85, 961–1019 (2013).

Ali, D. & Ahmed, H. Coulomb blockade in a silicon tunnel junction device. Appl. Phys. Lett. 64, 2119–2120 (1994).

Takahashi, Y., Ono, Y., Fujiwara, A. & Inokawa, H. Silicon single-electron devices. NTT Technical Review 2, 21–27 (2004).

Egger, R. & Gogolin, A. O. Bulk and Boundary Zero-Bias Anomaly in Multiwall Carbon Nanotubes. Phys. Rev. Lett. 87, 066401 (2001).

Mora, C., Egger, R. & Altland, A. From Luttinger liquid to Altshuler-Aronov anomaly in multichannel quantum wires. Phys. Rev. B 75, 035310 (2007).

Kane, C. L. & Fisher, M. P. A. Transport in a one-channel Luttinger liquid. Phys. Rev. Lett. 68, 1220–1223 (1992).

Stern, F. & Howard, W. E. Properties of Semiconductor Surface Inversion Layers in the Electric Quantum Limit. Phys. Rev. 163, 816–835 (1967).

Mott, N. F. Metal-Insulator Transitions (Taylor and Francis, 1990), 2nd edn.

Mott, N. & Davis, E. A. Electronic Process in Non-Crystalline Materials (Clarendon Press, 1979).

Althsuler, B. L. & Aronov, A. G. Electron-electron interactions in disordered conductors. In Electron-electron Interactions in Disordered Systems (eds Efros, A. L. & Pollak, M.), vol. 10, chap. 1 (North Holland, 1985).

Neophytou, N., Paul, A., Lundstrom, M. S. & Klimeck, G. Bandstructure Effects in Silicon Nanowire Electron Transport. IEEE Transactions on Electron Devices 55, 1286–1297 (2008).

Mirza, M. M. et al. Nanofabrication of high aspect ratio (~50:1) sub-10 nm silicon nanowires using inductively coupled plasma etching. J. Vac. Sci. Technol. B 30, 06FF02–1–8 (2012).

Scott, J. et al. Near-simultaneous dual energy range EELS spectrum imaging. Ultramicroscopy 108, 1586–1594 (2008).

Hunt, J. & Williams, D. Electron energy-loss spectrum-imaging. Ultramicroscopy 38, 47–73 (1991).

Acknowledgements

The work was funded by the U.K. EPSRC (grants EP/H024107/1 and EP/N003225/1) and F.J.S. would like to thank DSTL for funding a studentship (contract 1415NatPhD-59). The authors would like to thank the staff of the James Watt Nanofabrication Centre for help and support in undertaking the research.

Author information

Authors and Affiliations

Contributions

M.M.M. fabricated the device and undertook the electrical measurements. F.J.S. and J.A.M. analyzed the data, wrote the paper and were supervised by G.A.D.B., D.A.M. undertook the TEM measurements and analysis. D.J.P. proposed the experiment, designed the device, designed the integrated process, undertook parts of the analysis and wrote the paper.

Corresponding author

Ethics declarations

Competing Interests

The authors declare that they have no competing interests.

Additional information

Publisher's note: Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Electronic supplementary material

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made. The images or other third party material in this article are included in the article’s Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Mirza, M.M., Schupp, F.J., Mol, J.A. et al. One dimensional transport in silicon nanowire junction-less field effect transistors. Sci Rep 7, 3004 (2017). https://doi.org/10.1038/s41598-017-03138-5

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41598-017-03138-5

This article is cited by

-

A Novel High-Performance CMOS VCRO Based on Electrically Doped Nanowire FETs in 10 nm Node

Silicon (2023)

-

Logic and memory functions of an inverter comprising reconfigurable double gated feedback field effect transistors

Scientific Reports (2022)

-

A controllable fabrication improved silicon nanowire array sensor on (111) SOI for accurate bio-analysis application

Nano Research (2022)

-

Noise and charge discreteness as ultimate limit for the THz operation of ultra-small electronic devices

Scientific Reports (2020)

-

Electrothermal analysis of novel N-P-P FinFET with electrically doped drain: a dual material gate device for reliable nanoscale applications

Applied Physics A (2020)

Comments

By submitting a comment you agree to abide by our Terms and Community Guidelines. If you find something abusive or that does not comply with our terms or guidelines please flag it as inappropriate.