Abstract

High-quality two-dimensional atomic layered p–n heterostructures are essential for high-performance integrated optoelectronics. The studies to date have been largely limited to exfoliated and restacked flakes, and the controlled growth of such heterostructures remains a significant challenge. Here we report the direct van der Waals epitaxial growth of large-scale WSe2/SnS2 vertical bilayer p–n junctions on SiO2/Si substrates, with the lateral sizes reaching up to millimeter scale. Multi-electrode field-effect transistors have been integrated on a single heterostructure bilayer. Electrical transport measurements indicate that the field-effect transistors of the junction show an ultra-low off-state leakage current of 10−14 A and a highest on–off ratio of up to 107. Optoelectronic characterizations show prominent photoresponse, with a fast response time of 500 μs, faster than all the directly grown vertical 2D heterostructures. The direct growth of high-quality van der Waals junctions marks an important step toward high-performance integrated optoelectronic devices and systems.

Similar content being viewed by others

Introduction

The emerging two-dimensional (2D)-layered semiconductors have shown considerable potential for designing next-generation integrated electronic and optoelectronic systems, due to their many unique physical and structural properties1,2,3,4,5,6,7,8,9,10,11,12,13,14. In particularly, diverse 2D-layered semiconductors can be flexibly combined to form diverse vertical van der Waals (vdWs) heterostructures15,16,17,18,19,20,21,22,23 with atomically sharp interfaces and tunable band alignment, opening up vast opportunities for fundamental investigation of novel electronic and optical properties at the limit of single atom thickness and potential applications in novel device concepts9, 17, 19, 21, 24,25,26,27,28,29,30. The current studies of 2D van der Waals heterostructures have been largely limited to the mechanically exfoliated and restacked flakes17, 20, 26, 31,32,33,34, which is arduous and clearly un-scalable for practical technologies. Some recent progresses have also shown that 2D vertical heterostructures can be produced by direct vapor phase growth35,36,37,38,39,40,41,42. Compared to the mechanical stacking approach, the direct growth strategy could offer unique advantages of easy size control, clean interface, and potential for practical industrial applications. However, direct vapor growth of large-scale high-quality 2D atomic layered vertical heterostructures, especially p–n junctions, remains a great challenge.

As an important p-type 2D semiconductor with excellent physical properties, layered tungsten diselenide (WSe2) has attracted great attention as a promising material for future scaled device applications43. Tin disulfide (SnS2), as a member of IV–VI A group, and being an important n-type layered semiconductor, has drawn considerable attention due to the advantages of low-cost, earth-abundant, nontoxic, and enviromentally friendly34, 44, 45. Recently, 2D heterostructures combining the p-type WSe2 and n-type SnS2 have aroused great interest. Wang et al.34 have reported the preparation of few-layer/few-layer stacked WSe2/SnS2 device through a mechanically exfoliated and restacked method, and investigated their anti-ambipolar behavior. Zhang et al.35 demonstrated the growth of few layers of WSe2 on the pre-prepared randomly oriented micaoplates of SnS2. Herein, we report a two-step vapor phase route to controlled growth of large-scale WSe2/SnS2 vertical bilayer p–n junctions on SiO2/Si. The as-grown junctions are highly crystallized, with their lateral sizes reaching up to millimeter scale, representing the largest size of atomic layered vertical heterostructures ever been achieved. Backgate field-effect transistors were fabricated with high on–off ratio, ultra-low leakage current, and show fast photoresponse speed comparing favorably to mechanically staked 2D vertical junctions. The direct growth of high-quality van der Waals junctions marks an important step toward high-performance integrated optoelectronic device and systems.

Results

Characteristics of WSe2/SnS2 heterostructure

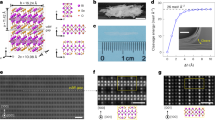

Figure 1a shows a top view of atomic structure illustration of the WSe2/SnS2 bilayer heterostructure, in which the bottom WSe2 monolayer and the top SnS2 monolayer are stacked by weak vdWs force. Figure 1b shows the relative band alignment of the bilayer WSe2/SnS2 heterostructure calculated by Vienna ab initio simulation package (VASP). The calculation details could be found in the Supplementary Figs 1 and 2. The valence band maximum of WSe2 is higher than that of the conduction band minimum of SnS2, forming a type-III broken-gap heterojunction17, 20. Both of the conduction band offset (∆E c, 1.69 eV) and the valence band offset (∆E v, 1.64 eV) of WSe2/SnS2 are larger than those of any other reported directly grown 2D heterostructures36, 37, 40, 41, 46, 47. The large band offset may cause efficient interlayer charge transfer between the bottom and the top layers, providing an ideal structural base for high-performance optical and electrical applications40, 48.

Synthesis of large-scale type-III WSe2/SnS2 heterostructure. a Schematic of vertically stacked WSe2/SnS2 vdW heterostructure. b Band alignment of type-III WSe2/SnS2 junction. c Schematic illustrating the two-step vapor expitaxy growth of WSe2/SnS2 heterostructure. d Typical optical image of as-grown large-scale monolayer WSe2 triangular flake achieved after step 1. e Optical image of as-grown vertically stacked WSe2/SnS2 heterostructure after step 2 by using the same flake in Fig. 1d. All the scale bars: 200 μm

The WSe2/SnS2 vertical bilayer heterostructures were grown via a two-step chemical vapor deposition (CVD) strategy. Large-scale WSe2 monolayers were first grown on the SiO2/Si substrate, through a controlled vapor deposition process. The pre-prepared large-scale WSe2 monolayers were then used as templates for subsequent van der Waals epitaxial growth of SnS2 monolayers in vapor phase to achieve the vertical bilayer heterostructures. The two-step vapor growth process is shown schematically in Fig. 1c, and the detailed descriptions about the growth are included in Method section.

For further understanding the two-step growth process, we have closely characterized the same WSe2 monolayer domain before and after the second step growth of SnS2 monolayer. Figure 1d gives the optical image of a typical as-grown large-scale WSe2 triangle flake, with the size measured to be 835 μm, and Fig. 1e is the corresponding WSe2/SnS2 vertical heterostructure obtained after the second step growth. The pre-grown WSe2 triangular domain is partially covered by the SnS2 domain, which can be distinguished from the optical contrast in the image. The size of the vertical junction can be well controlled by the growth time of both the bottom WSe2 and the top SnS2 layers, with the maximum lateral size reaching up to millimeter scale, which is about one order of magnitude larger than both the staked or synthetic vertical bilayer heterostructures reported previously36, 37, 40,41,42, 49. More detailed morphology information can be found in Supplementary Fig. 3.

Transmission electron microscope (TEM) measurements were conducted to further investigate the crystal quality and structure of the as-grown WSe2/SnS2 heterostructures. Figure 2a shows the optical image of a typical WSe2/SnS2 heterostructure for TEM characterization and Fig. 2b shows its corresponding TEM image at the marked interface region of the sample after transferred onto a copper grid (see method), with the inset showing the local high-magnification image of the interface. Fig. 2c shows the elemental energy dispersive X-ray spectroscopy (EDS) collected from both the monolayer (green, point 1 in Fig. 2b) and bilayer (red, point 2 in Fig. 2b) regions, respectively. Except the Cu signal from the grid, only elements W and Se were collected from the monolayer region, while apart from W and Se, elements Sn and S were also detected at the bilayer region, indicating the formation of WSe2/SnS2 heterostructure, which can also be well demonstrated by the element line scans across the interface region (Fig. 2d). The high resolution transmission electron microscope (HRTEM) image and the selected electron diffraction pattern (SAED) (Fig. 2e) show the bottom region is well crystallized with the measured lattice spacing of 0.28 nm, well consistent with the value of (100) plane spacing of WSe2. The bilayer heterostructure region shows obvious Moiré patterns (Fig. 2f), caused by the overlapping lattices between SnS2 and WSe2. The smallest periodic repeated cell is demarcated by the red dashed rhombus, with a lattice constant of 2.24 nm. The corresponding SAED shows two different sets of hexagonally arranged diffraction patterns (Fig. 2g), with the calculated lattice spacings consistent with the SnS2 (0.32 nm) and WSe2 (0.28 nm), respectively44. The large lattice misfit (14.3%) indicates that the SnS2 domain is stacked on the WSe2 through vdW epitaxy36, 37, 40,41,42. Figure 2h and i gives the top and side views of the theoretical atomic structure model of the WSe2/SnS2 heterostructure with Moiré patterns, consistent with the experimental observation shown in Fig. 2f, with the periodic repeated cell marked by the red dashed rhombus, corresponding to 7 × 7 SnS2 stacked on 8 × 8 WSe2 41.

Atomic structure of the vertically stacked WSe2/SnS2 heterostructure. a A typical optical image of the heterostructure with three interfaces at the corners of the triangle flake. Scale bar, 30 μm. b Low-resolution TEM image of the interface from the black rectangle region in a. Scale bar, 5 μm. Inset is the enlarged interface image highlighted in the yellow rectangle. Scale bar, 100 nm. c EDS results of point 1 and point 2 in b, marked by green and red colors, respectively. d Line scans of S, Sn, W, Se elements distribution across the red arrow in the inset of b. e HRTEM image taken on the green point 1 region in b. Scale bar, 2 nm. Inset is the SAED pattern of the bare WSe2. f HRTEM image taken on the red point 2 region in b, indicating the vertical stacked WSe2/SnS2 vdW heterostructure with Moiré pattern. Scale bar, 2 nm. g The SAED pattern collected from point 2 region shows two sets of electron diffraction patterns, corresponding to WSe2 and SnS2, respectively. h, i Top view and side view of the atomic model of the WSe2/SnS2 vdW heterostructure, respectively. The supercell is highlighted by red dashed lines

The thickness of the as-grown heterostructures was further confirmed by atomic force microscope (AFM) measurements. Figure 3b and c is the AFM images detected at the selected stack region (red dashed rectangle) and the interface region across from SnS2 to WSe2 (blue dashed rectangle), respectively, as marked in Fig. 3a. The insets of the AFM images show the corresponding line scan height profile, indicating that the thickness of both the bottom and the top layer are 0.8 nm, with a total thickness at the stack region of 1.5 nm, well demonstrating the achieved bilayer heterostructures (1 L WSe2 + 1 L SnS2).

AFM and PL characterization of the vertically stacked WSe2/SnS2 heterostructure. a Optical micrograph of a large-scale 1 L SnS2/1 L WSe2 stacked triangular flake grown on SiO2/Si. Scale bar, 100 μm. b AFM image of the blue rectangle region in a. Inset is height profile along blue arrow, indicating the thickness of bottom layer and top layer is 0.8 and 0.8 nm, respectively. Corresponding to 1 L SnS2 on 1 L WSe2. c AFM image of the red rectangle region in a. Inset is the height profile across the red arrow, indicating the thickness of the heterostructure is 1.5 nm (1 L WSe2 + 1 L SnS2). d PL intensity mapping (720–780 nm). Scale bar, 60 μm. Inset image is the optical image of the sample used for PL characterization. Scale bar, 100 μm. e PL spectra observed from bare WSe2 region (black curve) and WSe2/SnS2 vdW heterostructure region (red curve). f Schematic diagram of WSe2/SnS2 heterostructure band structure and photoexcitation, interlayer relaxation process in WSe2/SnS2 heterojunction

Room temperature photoluminescence (PL) mapping (720 nm - 780 nm) and their corresponding local spectra obtained from a typical heterostructure domain with most of its surface being bilayer stacked (Fig. 3d, e). The results indicate that the bottom uncovered WSe2 monolayer exhibits strong PL emission with a dominant emission peak locating at 766 nm, corresponding to the recombination of excitons50, 51, whereas the bilayer WSe2/SnS2 region shows apparent PL quenching, with essentially no detectable PL (Fig. 3e). The PL quenching in the stack region indicates the interaction induced energy (charged carrier) transfer between the WSe2 and the SnS2 48. According to the band alignment of WSe2/SnS2 as shown in Fig. 1b, the conduction band minimum of SnS2 is about 1.78 eV lower than that of WSe2, whereas the valence band maximum of SnS2 is about 1.67 eV lower than that of WSe2. Thus, the photo-excited electrons and holes in WSe2 prefer to transfer to low-energy states in SnS2, rather than forming excitons in WSe2, However, being a typical indirect semiconductor, SnS2 is normally inradiative44, 52. The charge transfer from WSe2 to SnS2 will consequently lead to the significant PL quenching of the heterostructures (Fig. 3e), as schematically exhibited in Fig. 3f 37, 40, 41, 46, 48, 53, 54.

Electrical transport properties of WSe2/SnS2 heterostructure

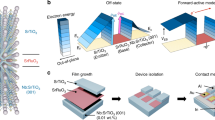

To further investigate the electrical charge transport properties and optoelectronic performance of the resulted WSe2/SnS2 vdW heterostructures, multi-electrode backgate field-effect transistors (FETs) were designed and fabricated based on a partially covered heterostructure domain grown at a (P++) Si/SiO2 substrate, with Ti/Au thin film as the source-drain electrodes and the silicon substrate as the backgate contact electrode, as shown schematically in Fig. 4a. This device structure is suitable for systematically investigating the performance of different devices integrated on the same nanostructure. All the device measurements were conducted under vacuum at room temperature.

Electrical characterization of the vertically stacked WSe2/SnS2 heterostructure. a Schematic diagram of the multi-electrode WSe2/SnS2 vdW heterostructure backgate device. b Front view of the WSe2/SnS2 vdW heterostructure. c An optical image of fabricated WSe2/SnS2 vdW heterostructure device. Scale bar, 60 μm. d I ds − V bg curves of the pristine WSe2 measured using electrodes 1 and 2, demonstrating p-type behavior. e I ds − V ds output characteristics of pristine WSe2 FET at various backgate voltages. f I ds − V bg curves of the parallel-mode vdW heterostructure measured using electrodes 5 and 6, demonstrating ambipolar behavior. g I ds − V ds output characteristics of the parallel-mode vdW heterostructure at various backgate voltages from −60 V to 10 V and from 20 V to 60 V. h I ds − V bg curves across the p (WSe2) − n (SnS2) heterojunction, named parallel-series mode, demonstrating p-type behavior (measured using electrodes 3 and 4). i I ds − V ds output characteristics across the p–n junction at different backgate voltages

Figure 4b gives schematically the front view of the heterostructure, with electron dominating the charge transfer process in the n-type SnS2 layer and hole dominating transfer in the p-type WSe2 layer, as reported in the literatures44, 55,56,57. The optical image of a typical WSe2/SnS2 vdW heterostructure after device fabrication is shown in Fig. 4c. Electrodes 1, 2, and 3 were deposited on top of the pristine WSe2 region, whereas electrodes 4, 5, and 6 were deposited on the top of the stack WSe2/SnS2 region. As a result, three kinds of device channels were formed, (1) pristine WSe2 channel (electrodes 1 and 2, yellow), (2) parallel-mode channel (electrodes 5 and 6, green, bilayer stacked region) and (3) parallel-series mode channel (electrodes 3 and 4, red, heterojunction region), respectively. The transport characteristic of pristine WSe2 shows typical p-type behavior, indicating that holes dominate charge transport process, with an on–off ratio of 105 and a threshold voltage of −2 V (Fig. 4d). The corresponding output characteristic in Fig. 4e shows that the I ds decreases with the V g varying from −60 to 0 V, and the I ds − V ds curves shows an inflection point at near V ds = 0 V, indicating the existence of a Schottky barrier at the WSe2 contacting with Ti/Au. The field-effect charge carrier mobility is calculated to be 0.02 cm2 V−1 s−1 (L = 5.2 μm, W = 36.5 μm, V ds = 1 V). In addition, the transport characteristic of the parallel-mode device shows ambipolar behavior (Fig. 4f), which is attributed to the p-type WSe2 and the n-type SnS2 41. The corresponding output characteristic show that the I ds − V ds have very good linear relation at negative V g values, and I ds decreases as the back voltage varies from −60 to 10 V, following an increase as V g varies from 10 to 60 V (Fig. 4g). The hole mobility is calculated to be 10.1 cm2 V−1 s−1 (L = 4.25 μm, W = 51 μm, V ds = 1 V), which is three orders higher than that of the pristine WSe2. Moreover, the device shows an on–off ratio of 104 with a saturation current reaching up to 10 μA (V ds = 1 V). The electric transport properties of the parallel-series mode device were measured using electrodes 3 and 4. The transport characteristic is p-type dominant, indicating that holes in the bottom WSe2 dominate the charge transport across this junction. The hole mobility is calculated to be 0.149 cm2 V−1 s−1 (Fig. 4h) (L = 9.35 μm, W = 21.2 μm, V ds = 1 V), one order higher than that of the pristine WSe2 device. Importantly, benefit from the existence of the barrier near the vertical junction, leading to a very low leak current (10−14 A), and an ultrahigh on–off ratio to 107, two orders higher than that of the pristine WSe2 device (105) and three orders higher than that of the parallel-mode device (104). Gate-tunable output curves show obvious current rectification behavior (Fig. 4i), indicating a p–n diode is formed across the heterojunction.

It is well reported that vapor grown TMDs monolayers usually have very low mobility, mainly caused from the carrier scattering by the inevitable lattice defects induced during the vapor synthesis and device fabrication processes58, 59, which is also demonstrated in the pristine WSe2 monolayer device. The mobility can be greatly improved from the heterostructured channels, i.e., the parallel-mode and the parallel-series mode devices, which can be attributed to several reasons. Firstly, the electrons and holes can be efficiently separated with less interactive scattering and faster transfer in the type-III band alignment heterostructures40. Secondly, the van der Waals force in the interface will also help to suppress the extrinsic interfacial impurities to increase the mobility60, 61. Thirdly, comparing to a single layer of WSe2, the increased carrier density in the heterostructure will enhance the screening of the interfacial Coulomb potential, which will also help to improve the mobility61.

Photovoltaic and photoresponse properties of WSe2/SnS2 heterostructure

The photovoltaic and photoresponse properties of the WSe2/SnS2 p–n heterojunction (parallel-series mode) were investigated using electrodes 3 and 4 (see Fig. 4c). All the measurements were conducted by applying a drain voltage V ds on WSe2 (p-type, terminal “d”), with SnS2 (n-type, terminal “s”) being grounded (Fig. 5a).

Optoelectronic characterization of the parallel-series mode WSe2/SnS2 heterojunction. a A cartoon schematic of the parallel-series mode WSe2/SnS2 vdW heterojunction photodetector. Inset is an optical image of the heterojunction device. (measured using electrodes 3 and 4, see Fig. 4c). b I ds − V ds curves across the p–n junction under 520 nm laser illumination at different incident power. c I ds − V ds curves at various backgate voltages from −60 V to 0 V under 520 nm laser illumination at fixed 101 mW cm−2 power intensity. d I ds − V ds curves across the p–n junction under 520 nm laser illumination at different incident power. V ds range from −1 V to 1 V. e Dependence of photocurrent on illumination power intensities. f Photoresponsivity and detectivity of the photodetector at various illumination power intensities. g Photocurrent response of the device, the laser light is turned on/off by a chopper worked at 1 Hz (520 nm, 101 mW cm−2, V ds = 1 V). h, i Time-resolved photoresponse of the device, namely the rise and fall times of the photocurrent measured at V ds = 1 V

Furthermore, obvious photovoltaic effect was observed in the direct grown WSe2/SnS2 p–n heterojunction when the junction was under 520 nm laser illumination, which further demonstrate the formation of the atomic junction. As shown in Fig. 5b, with increasing the laser power, more photoinduced electro-hole pairs will separate and contribute to a higher I sc. Meanwhile, more electrons and holes excited by the laser illumination aggregate in the interface region and enhance the band bending, which will further increase the absolute value of V oc. In addition, as shown in Fig. 5c, when the backgate voltage varies from 0 to −60 V, the absolute value of V oc shows a decrease, with I sc changed slightly. The Fermi level of WSe2 moved down under negative gate voltages, leading to a less band bending and decrease the built-in potential difference, result in a smaller V oc. At the same time, both negative backgate voltage and the laser illumination will trigger an excess carrier concentration, which will reduce the lifetime of carrier and simultaneously increase the recombination. As a result, the I sc changes slightly17, 41.

Photoconductive properties of the parallel-series mode device under different laser power were also examined, as shown in Fig. 5d. I ph is the photocurrent which is defined as I ph = I light- I dark, and the obtained data under different laser power are shown in Fig. 5e, fitted with an equation of I ph = aP α. In our experiments, the fitted parameters of a and α are 8.86 × 10−10 and 0.39, respectively. The responsivity (R) is calculated by the equation of R = I ph/PA, where I ph is the photocurrent, P is the incident light power density, and A is the effective area of the device channel. The responsivity of the device can reach up to 108.7 mA W−1 (P = 13.63 nW, V ds = 5 V, device area of 198.2 μm2), which is a lot higher than the ever repoted 2D vapor epitaxy grown p–n junction41. Detectivity (D*) is used to characterize the sensitivity of a photodetector. Assuming that shot noise from the dark current is the major factor limiting the D*, which can be estimated by D* = RA 1/2/(2e I dark)1/2, where R is responsivity, A is the effective area of the device channel, e is the electronic charge, and I dark represents the dark current62, 63. The maximum estimated D* value of 4.71 × 1010 Jones can be obtained based on this expression (Fig. 5f). To further investigate the response speed of the WSe2/SnS2 p–n heterojunction photodetector, time-resolved photoresponse measurements were performed by turning on and off the laser light (520 nm, 100 mW cm−2) with a chopper worked at 1 Hz. A high-speed oscilloscope was used to monitor the fast-varying signal. As shown in Fig. 5g, the photodetector exhibits the excellent stability and reliability with the on/off photoswitching behavior at V ds = 1 V without additional gate voltage. The rise time (τ r) and the fall time (τ f) is 500 μs and 600 μs, respectively, as shown in Fig. 5h, i. Importantly, as far as we known, the response speed of the WSe2/SnS2 heterojunction photodetector is faster than all the CVD directly grown vertical stacked 2D heterostructures37, 40,41,42, 64, even two orders of magnitude faster than most mechanical exfoliated and restacked vertical 2D heterostructures65,66,67, and nearly four orders of magnitude faster than the response time of the reported pristine WSe2 detector68, 69.

To further systematically understand the high-performance of the junction (parallel-series mode) detector, the photodetectors of the pristine WSe2 monolayer and the parallel-mode vertical stacked structure based on the same flake were also fabricated and comparatively investigated, as shown in Supplementary Figs. 4 and 5. From the results, the performances of the heterostructured devices (parallel-mode and parallel-series mode) are overall a lot higher than those of the pristine device. For the parallel-series mode devices, the photoinduced electron-hole pairs can be efficiently separated due to the large band offset (Fig. 1b). Meanwhile, benefit from the higher mobility comparing to pristine WSe2, the electrons and holes can be transported faster to the opposite terminals after separation. Both these two factors help increasing the R value and the response speed. However, having a large dark current (10−8 A), the photodetectivity is greatly limited for the parallel-mode device, and this disadvantages can be greatly improved in the parallel-series mode device, which possesses the advantages of both efficiently separation, fast charge transfer and also maintain low dark current (10−12 A at V ds = 1 V). As a result, the achieved 2D large-scale WSe2/SnS2 heterojunction photodetectors show great potential for high-speed and weak signal detection applications in integrated optoelectronic applications.

Discussion

We have demonstrated direct van der Waals epitaxial growth of vertical bilayer WSe2/SnS2 p–n junction. The as-grown junctions are highly crystallized, with their lateral sizes reaching up to millimeter scale, representing the largest size of atomic layered vertical heterostructures ever been achieved. TEM results have shown obvious periodic Moiré patterns, indicating a large lattice mismatch (14.3%), further demonstrating the SnS2 domain is stacked on the WSe2 through vdW epitaxy. Strong PL quenching in the bilayer region of WSe2/SnS2 heterostructure was observed, coming from the efficient interlayer charge transfer between the bottom and the top layers. Multi-electrodes backgate FETs were constructed, result in three different kinds of devices integrated on one typical heterostructure flake. Their perfomance of FETs and photodetectors were systematically investigated, indicating the parallel-series mode WSe2/SnS2 p–n junction exhibits an ultra-low leak-off current (10−14 A), and a highest on–off ratio (107). Devices based on the parallel-series mode WSe2/SnS2 p–n junction exhibit an obvious positive promotion in photoresponsvity (108.7 mA W−1), photodetectivity (4.71 × 1010 Jones) and photoresponse speed (500 μs), comparing to the pristine WSe2, with all the values improved than all the ever reported direct grown 2D vertical p–n junctions. This study of WSe2/SnS2 van der Waals heterostructures marks a important step toward high-performance integrated optoelectronic devices and systems.

Methods

Materials synthesis

For the first growth of WSe2 monolayer, tungsten diselenide powder was placed at the center of furnace, and a piece of SiO2/Si substrate was placed at the downstream of the quartz tube. At the beginning, 400 SCCM Ar was flowed into the tube for 15 min to ensure a stable chemical reaction environment. Then the flow rate of Ar was controlled at 50 SCCM and the center temperature of the furnace was heated to 1100 °C, keeping at this temperature for ten minutes. For the second growth, three quartz boats loaded with S powder, SnO2 powder, and a piece of SiO2/Si substrate with as-grown WSe2 monolayers were placed at the upstrem, center and downstrem of the quartz tube, respectively. After the air inside the tube had been purged by Ar flow, the furnace was heated to 600 °C and kept for 8 min. During the growth process, the Ar flow was 50 SCCM and the pressure inside was 8 Torr. After grwoth, the furnace was cooled down to room temperature naturelly.

Characterizations of as-grown WSe2/SnS2 heterostructures

The morphologies of WSe2/SnS2 heterostructures were characterized using optical microscopy (Zeiss Axio Scope A1), AFM (Bruker Multimode 8). PL measurements were conducted by using a confocal microscope (WITec, alpha-300) with an objective focused 488 nm laser. For the TEM characterization of the sample, the nanosheets were transfered onto grid of copper using a PMMA-assisted positioning transfer method. SiO2/Si wafer accompanied with WSe2/SnS2 heterostructures was coated with PMMA (950 K, A3) by spin-coating at a speed of 2000 RPM for 1 min, then baked the wafer at 180 °C for 2 h. After that, the target WSe2/SnS2 heterostructure flake was located by using the coordinates with an optical microscope. Then the edge of the baked wafer was round up with scotch tape, and subsequently immersed into the KOH (15 M) solution for 12 h. Then the PMMA film was taken out from the KOH solution and swilled fully with DI water. The cleaned PMMA film was removed onto a grid of copper and leaved the grid in the atmosphere of acetone vapor at 40 °C. Finally, the PMMA film was taken away by acetone vapor, leaving the target WSe2/SnS2 heterostructure on the grid of copper.

Fabrication and measurement of the as-grown WSe2/SnS2 devices

First, a layer of MMA copolymer (EL6, Microchem Company) was spin-coated on the SiO2 (300 nm)/Si substrate with WSe2/SnS2 heterostructures, followed by a 1 min bake at 160 °C on the hot plate. After this, another layer of PMMA (495 K, A4, Microchem Company) was spin-coated on the substrate followed by a 5 min bake at 160 °C. Electron beam lithography (Raith 150 two) was employed to define the drain and source electrodes. After conventional development process, Ti/Au metal layer (Ti: 5 nm, Au: 50 nm) was deposited to form the source-drain electrodes by electron beam evaporation, and finally followed by lift-off process with acetone. The electrical and optoelectronic properties of the heterostructures were measured in vacuum (10−6 torr) with the Lake Shore Probe Station and Keithley 4200 semiconductor analyzer at room temperature. The time response of the device was measured by switching the laser on and off with an internal square-wave trigger source and recorded by a digital oscilloscope.

Data availability

The authors declare that all of the data supporting the findings of this study are available within the article and its Supplementary Information file.

References

Novoselov, K. S. et al. Two-dimensional atomic crystals. Proc. Natl. Acad. Sci. USA 102, 10451–10453 (2005).

Zhang, Y., Tan, Y. W., Stormer, H. L. & Kim, P. Experimental observation of the quantum Hall effect and Berry’s phase in graphene. Nature 438, 201–204 (2005).

Liao, L. et al. High-speed graphene transistors with a self-aligned nanowire gate. Nature 467, 305–308 (2010).

Mak, K. F., Lee, C., Hone, J., Shan, J. & Heinz, T. F. Atomically thin MoS2: a new direct-gap semiconductor. Phys. Rev. Lett. 105, 136805 (2010).

Splendiani, A. et al. Emerging photoluminescence in monolayer MoS2. Nano Lett. 10, 1271–1275 (2010).

Radisavljevic, B., Radenovic, A., Brivio, J., Giacometti, V. & Kis, A. Single-layer MoS2 transistors. Nat. Nanotechnol. 6, 147–150 (2011).

Zeng, H., Dai, J., Yao, W., Xiao, D. & Cui, X. Valley polarization in MoS2 monolayers by optical pumping. Nat. Nanotechnol. 7, 490–493 (2012).

Lopez-Sanchez, O., Lembke, D., Kayci, M., Radenovic, A. & Kis, A. Ultrasensitive photodetectors based on monolayer MoS2. Nat. Nanotechnol. 8, 497–501 (2013).

Cheng, R. et al. Electroluminescence and photocurrent generation from atomically sharp WSe2/MoS2 heterojunction p–n diodes. Nano Lett. 14, 5590–5597 (2014).

Duan, X. et al. Lateral epitaxial growth of two-dimensional layered semiconductor heterojunctions. Nat. Nanotechnol. 9, 1024–1030 (2014).

Wu, S. et al. Monolayer semiconductor nanocavity lasers with ultra-low thresholds. Nature 520, 69–72 (2015).

Duan, X. et al. Synthesis of WS2xSe2-2x alloy nanosheets with composition-tunable electronic properties. Nano Lett. 16, 264–269 (2016).

Fan, X. et al. Broken symmetry induced strong nonlinear optical effects in spiral WS2 nanosheets. ACS Nano 11, 4892–4898 (2017).

Li, H. et al. Composition-modulated two-dimensional semiconductor lateral heterostructures via layer-selected atomic substitution. ACS Nano 11, 961–967 (2017).

Kang, J., Tongay, S., Zhou, J., Li, J. & Wu, J. Band offsets and heterostructures of two-dimensional semiconductors. Appl. Phys. Lett. 102, 012111 (2013).

Chiu, M. H. et al. Determination of band alignment in the single-layer MoS2/WSe2 heterojunction. Nat. Commun. 6, 7666 (2015).

Yan, R. et al. Esaki diodes in van der Waals heterojunctions with broken-gap energy band alignment. Nano Lett. 15, 5791–5798 (2015).

Chiu, M. H. et al. Band alignment of 2D transition metal dichalcogenide heterojunctions. Adv. Funct. Mater. 27, 1603756 (2017).

Nourbakhsh, A., Zubair, A., Dresselhaus, M. S. & Palacios, T. Transport properties of a MoS2/WSe2 heterojunction transistor and its potential for application. Nano Lett. 16, 1359–1366 (2016).

Shim, J. et al. Phosphorene/rhenium disulfide heterojunction-based negative differential resistance device for multi-valued logic. Nat. Commun. 7, 13413 (2016).

Zhang, K. et al. Interlayer transition and infrared photodetection in atomically thin type-II MoTe2/MoS2 van der Waals heterostructures. ACS Nano 10, 3852–3858 (2016).

Xiao, D., Liu, G. B., Feng, W., Xu, X. & Yao, W. Coupled spin and valley physics in monolayers of MoS2 and other group-VI dichalcogenides. Phys. Rev. Lett. 108, 196802 (2012).

Lee, B. et al. Fano resonance and spectrally modified photoluminescence enhancement in monolayer MoS2 integrated with plasmonic nanoantenna array. Nano Lett. 15, 3646–3653 (2015).

Roy, T. et al. Dual-gated MoS2/WSe2 van der Waals tunnel diodes and transistors. ACS Nano 9, 2071–2079 (2015).

Yu, W. J. et al. Highly efficient gate-tunable photocurrent generation in vertical heterostructures of layered materials. Nat. Nanotechnol. 8, 952–958 (2013).

Massicotte, M. et al. Picosecond photoresponse in van der Waals heterostructures. Nat. Nanotechnol. 11, 42–46 (2016).

Zhang, C. et al. Interlayer couplings, Moiré patterns, and 2D electronic superlattices in MoS2/WSe2 hetero-bilayers. Sci. Adv. 3, e1601459 (2017).

Wang, X., Cheng, Z., Xu, K., Tsang, H. K. & Xu, J.-B. High-responsivity graphene/silicon-heterostructure waveguide photodetectors. Nat. Photon. 7, 888–891 (2013).

Zhang, E. et al. Tunable positive to negative magnetoresistance in atomically thin WTe2. Nano Lett. 17, 878–885 (2017).

Wu, B. et al. Precise, self-limited epitaxy of ultrathin organic semiconductors and heterojunctions tailored by van der Waals interactions. Nano Lett. 16, 3754–3759 (2016).

Roy, K. et al. Graphene-MoS2 hybrid structures for multifunctional photoresponsive memory devices. Nat. Nanotechnol. 8, 826–830 (2013).

Yu, W. J. et al. Vertically stacked multi-heterostructures of layered materials for logic transistors and complementary inverters. Nat. Mater. 12, 246–252 (2013).

Ross, J. S. et al. Interlayer exciton optoelectronics in a 2D heterostructure p–n junction. Nano Lett. 17, 638–643 (2017).

Wang, Y. et al. Light induced double ‘on’ state anti-ambipolar behavior and self-driven photoswitching in p-WSe2/n-SnS2 heterostructures. 2D Mater. 4, 025097 (2017).

Zhang, X. et al. Vertical heterostructures of layered metal chalcogenides by van der Waals epitaxy. Nano Lett. 14, 3047–3054 (2014).

Gong, Y. et al. Vertical and in-plane heterostructures from WS2/MoS2 monolayers. Nat. Mater. 13, 1135–1142 (2014).

Gong, Y. et al. Two-step growth of two-dimensional WSe2/MoSe2 heterostructures. Nano Lett. 15, 6135–6141 (2015).

Lin, Y. C. et al. Atomically thin resonant tunnel diodes built from synthetic van der Waals heterostructures. Nat. Commun. 6, 7311 (2015).

He, Y. et al. Strain-induced electronic structure changes in stacked van der Waals heterostructures. Nano Lett. 16, 3314–3320 (2016).

Li, B. et al. Direct vapor phase growth and optoelectronic application of large band offset SnS2/MoS2 vertical bilayer heterostructures with high lattice mismatch. Adv. Elec. Mater. 2, 1600298 (2016).

Li, X. et al. Two-dimensional GaSe/MoSe2 misfit bilayer heterojunctions by van der Waals epitaxy. Sci. Adv. 2, e1501882 (2016).

Zhou, X. et al. Vertical heterostructures based on SnSe2/MoS2 for high performance photodetectors. 2D Mater. 4, 025048 (2017).

Huang, J. et al. Large-area synthesis of highly crystalline WSe2 monolayers and device applications. ACS Nano 8, 923–930 (2014).

Zhou, X., Zhang, Q., Gan, L., Li, H. & Zhai, T. Large-size growth of ultrathin SnS2 nanosheets and high performance for phototransistors. Adv. Funct. Mater. 26, 4405–4413 (2016).

Wang, Y., Huang, L. & Wei, Z. Photoresponsive field-effect transistors based on multilayer SnS2 nanosheets. J. Semicond. 38, 034001 (2017).

Tongay, S. et al. Tuning interlayer coupling in large-area heterostructures with CVD-grown MoS2 and WS2 monolayers. Nano Lett. 14, 3185–3190 (2014).

Shi, J. et al. Temperature-mediated selective growth of MoS2/WS2 and WS2/MoS2 vertical stacks on Au foils for direct photocatalytic applications. Adv. Mater. 28, 10664–10672 (2016).

Yu, Y. et al. Equally efficient interlayer exciton relaxation and improved absorption in epitaxial and nonepitaxial MoS2/WS2 heterostructures. Nano Lett. 15, 486–491 (2015).

Fu, L. et al. Direct growth of MoS2/h-BN heterostructures via a sulfide-resistant alloy. ACS Nano 10, 2063–2070 (2016).

You, Y. et al. Observation of biexcitons in monolayer WSe2. Nat. Phys. 11, 477–481 (2015).

Tonndorf, P. et al. Photoluminescence emission and Raman response of monolayer MoS2, MoSe2, and WSe2. Opt. Express. 21, 4908–4916 (2013).

Gonzalez, J. M. & Oleynik, I. I. Layer-dependent properties of SnS2 and SnSe2 two-dimensional materials. Phys. Rev. B. 94, 125443 (2016).

Hong, X. et al. Ultrafast charge transfer in atomically thin MoS2/WS2 heterostructures. Nat. Nanotechnol. 9, 682–686 (2014).

Furchi, M. M., Pospischil, A., Libisch, F., Burgdorfer, J. & Mueller, T. Photovoltaic effect in an electrically tunable van der Waals heterojunction. Nano Lett. 14, 4785–4791 (2014).

Burton, L. A. et al. Electronic and optical properties of single crystal SnS2: an earth-abundant disulfide photocatalyst. J. Mater. Chem. A. 4, 1312–1318 (2016).

Liu, J., Xia, C., Li, H. & Pan, A. High on/off ratio photosensitive field effect transistors based on few layer SnS2. Nanotechnology 27, 34LT01 (2016).

Zhou, H. et al. Large area growth and electrical properties of p-type WSe2 atomic layers. Nano Lett. 15, 709–713 (2015).

Lee, Y. H. et al. Synthesis and transfer of single-layer transition metal disulfides on diverse surfaces. Nano Lett. 13, 1852–1857 (2013).

Zhang, Y. et al. Controlled growth of high-quality monolayer WS2 layers on sapphire and imaging its grain boundary. ACS Nano 7, 8963–8971 (2013).

Zhang, W., Wang, Q., Chen, Y., Wang, Z. & Wee, A. T. S. Van der Waals stacked 2D layered materials for optoelectronics. 2D Mater. 3, 022001 (2016).

Cui, X. et al. Multi-terminal transport measurements of MoS2 using a van der Waals heterostructure device platform. Nat. Nanotechnol. 10, 534–540 (2015).

Fang, H. et al. Visible light-assisted high-performance mid-infrared photodetectors based on single InAs nanowire. Nano Lett. 16, 6416–6424 (2016).

Wang, P. et al. Arrayed van der Waals broadband detectors for dual-band detection. Adv. Mater. 29, 1604439 (2017).

Xue, Y. et al. Scalable production of a few-layer MoS2/WS2 vertical heterojunction array and its application for photodetectors. ACS Nano 10, 573–580 (2016).

Huo, N. et al. Tunable polarity behavior and self-driven photoswitching in p-WSe2/n-WS2 heterojunctions. Small 11, 5430–5438 (2015).

Pezeshki, A., Shokouh, S. H., Nazari, T., Oh, K. & Im, S. Electric and photovoltaic behavior of a few-layer alpha-MoTe2/MoS2 dichalcogenide heterojunction. Adv. Mater. 28, 3216–3222 (2016).

Yang, S. et al. Self-driven photodetector and ambipolar transistor in atomically thin GaTe-MoS2 p–n vdW heterostructure. ACS Appl. Mater. Inter. 8, 2533–2539 (2016).

Chen, J. et al. Chemical vapor deposition of large-sized hexagonal WSe2 crystals on dielectric substrates. Adv. Mater. 27, 6722–6727 (2015).

Zhang, W. et al. Role of metal contacts in high-performance phototransistors based on WSe2 monolayers. ACS Nano 8, 8653–8661 (2014).

Acknowledgements

This work was supported by the NSF of China (Nos. 51525202, 21521063, 61574054, 61505051, 61625402, 61474040, 61725505, and 11734016), the Hunan province science and technology plan (Nos. 2014FJ2001 and 2014TT1004), National Key Basic Research Program of China 2015CB921600, the Aid program for Science and Technology Innovative Research Team in Higher Educational Institutions of Hunan Province and the Fundamental Research Funds for the Central Universities.

Author information

Authors and Affiliations

Contributions

A.P., T.Y. and B.Z. conceived and designed the experiments. B.Z. synthesized the heterostructures. Y.F. and J.Z. performed the band structure calculation. T.Y., B.Z. carried out AFM and photoluminescence measurements. B.Z., T.Y., T.X. and L.S. carried out TEM measurements. T.Y., Z.W. and C.P. carried out the device fabrication and measurements. A.P., T.Y. and B.Z. wrote the paper with significant inputs from X.Z., Z.Q., H.L., W.H., F.M. and X.D. And A.P. supervised the research. All the authors participated in the analysis of the data and discussed the results. All the authors have read and approved the manuscript.

Corresponding authors

Ethics declarations

Competing interests

The authors declare no competing financial interests.

Additional information

Publisher's note: Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Electronic supplementary material

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made. The images or other third party material in this article are included in the article’s Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Yang, T., Zheng, B., Wang, Z. et al. Van der Waals epitaxial growth and optoelectronics of large-scale WSe2/SnS2 vertical bilayer p–n junctions. Nat Commun 8, 1906 (2017). https://doi.org/10.1038/s41467-017-02093-z

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41467-017-02093-z

Comments

By submitting a comment you agree to abide by our Terms and Community Guidelines. If you find something abusive or that does not comply with our terms or guidelines please flag it as inappropriate.