## ARTICLE

### **Open Access**

# Charge carrier modulation in graphene on ferroelectric single-crystal substrates

Nahee Park<sup>1</sup>, Hyunkyung Lee<sup>2</sup>, Jeongmin Park<sup>1</sup>, Tuan Khanh Chau<sup>1</sup>, Hojin Kang<sup>1</sup>, Haeyong Kang<sup>6</sup> and Dongseok Suh<sup>6</sup>

### Abstract

Charge carrier modulation of graphene using the ferroelectricity of a nearby dielectric can be useful for controlling the electronic properties of graphene. However, when graphene is located on ferroelectric oxides, their electrical coupling frequently shows abnormal behaviors, such as anti-hysteresis, in field-effect transistor operation. From the systematic examination of graphene on a ferroelectric oxide single-crystal [Pb(Mg<sub>1/3</sub>Nb<sub>2/3</sub>)O<sub>3</sub>]<sub>1-x</sub>–[PbTiO<sub>3</sub>]<sub>x</sub> (PMNPT) substrate, we observed that the ferroelectric modulation of graphene was significantly influenced by the ambipolar nature of graphene and ferroelectric-assisted charge trapping with carrier-type dependency. For graphene/hexagonal-BN on the PMNPT, the Coulomb interaction between charges in interfacial traps and ferroelectric polarization seems to decouple the graphene conductance from the polarization field and induce only the charge trap effect on device performance. Consequently, the asymmetric surface charge compensation of ferroelectric oxide by the ambipolar graphene channel determines the detailed coupling process between the charge carrier of graphene and ferroelectric polarization, resulting in direct ferroelectric coupling or indirect anti-hysteretic coupling.

### Introduction

Ferroelectricity is one of the most basic phenomena frequently observed in functional dielectric materials. The broken crystal inversion symmetry induces a permanent electric dipole moment inside a material, and this spontaneous polarization is an extensively studied topic in solid-state physics<sup>1–3</sup>. The polarization state can be manipulated using an external electric field, and its hysteresis is shown in the electric-field-dependent polarization curve. Ferroelectric materials can be used in fieldeffect transistors, where a ferroelectric layer functions as a gate dielectric insulator. The charge carrier modulation of the conducting channel is performed using the ferroelectric polarization field. From its nonvolatility, the information can be stored in the form of the polarization

Correspondence: Haeyong Kang (haeyong.kang@pusan.ac.kr) or

Dongseok Suh (energy.suh@skku.edu)

<sup>1</sup>Department of Energy Science, Sungkyunkwan University, Suwon 16419, Republic of Korea direction. This can be monitored using the magnitude change in the source-drain current that flows through the channel of the semiconducting material in contact with the ferroelectric gate dielectric layer<sup>4,5</sup>. There have been several combinations of ferroelectric and semiconducting materials, such as Pb(Zr,Ti)O<sub>3</sub> on silicon and polyvinylidene-fluoride/organic-semiconductors, which have been successfully operated as ferroelectric-gated field-effect transistors<sup>6–16</sup>.

Unlike traditional semiconductors, atomically thin twodimensional (2D) materials such as graphene have been employed as a conducting channel owing to their metallic charge carrier modulation capability<sup>17–45</sup>. Especially for graphene, a Dirac-cone-shaped band structure enables easy control of the chemical potential by the permanent electric dipole moment of a ferroelectric layer. As expected, the conductance of graphene in contact with ferroelectric polymers has been reported to show direct coupling between the charge carriers of graphene and ferroelectric polarization<sup>17–23</sup>. Interestingly, however, many researchers have also reported anti-hysteresis

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons license, and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/.

<sup>&</sup>lt;sup>2</sup>Department of Physics, Pusan National University, Busan 46241, Republic of Korea

<sup>©</sup> The Author(s) 2022

behavior, whose hysteresis direction is opposite to that of the normal ferroelectric hysteresis curve, especially when a ferroelectric oxide material is used as a back-gate dielectric for graphene transistors<sup>24–35</sup>. In addition, in some reports, the shape of conductance hysteresis varies as a function of temperature or applied electric field<sup>27,30,33,36–38</sup>. Such diversity in the shape of hysteresis curves in graphene/ ferroelectric systems indicates that the interface between the two materials is critical to determining the coupling of charges between graphene and the ferroelectric layer. Nonetheless, this behavior is not completely understood despite the simplicity of the device structure.

When mechanical contact between a ferroelectric oxide and graphene is considered, the van der Waals interaction is the only driving force for their contact. Therefore, the adhesion and/or spacing between the ferroelectric oxide and graphene is critically important. At first glance, the pure ferroelectric polarization field is expected to induce charges inside graphene and/or interfacial charge traps that act as extrinsic doping sources. From this aspect, an emphasis has been placed on the role of interfacial molecules that are trapped between graphene and ferroelectric oxide, as the characteristics of these molecules seem to determine the type of interaction between graphene and ferroelectrics. However, these molecules are still insufficient to explain the variety of charge trapping phenomena associated with ferroelectrics 46-52. In this study, we report the systematic analysis of graphene-ferroelectric devices, in which  $[Pb(Mg_{1/3}Nb_{2/3})O_3]_{1-x}$ - $[PbTiO_3]_x$  (PMNPT) is used as the ferroelectric oxide layer. Due to the singlecrystalline feature of the PMNPT, we can sharply define the motion of polarization switching. Furthermore, the ambipolar charge conduction behavior of graphene in response to the applied electric field can be sensitively monitored by tracing the movement of the charge neutrality point (CNP). Using field-effect devices consisting of graphene and PMNPT, the unconventional charge coupling phenomena between graphene and ferroelectric oxide are carefully analyzed.

### Methods

### Experimental design and device fabrication

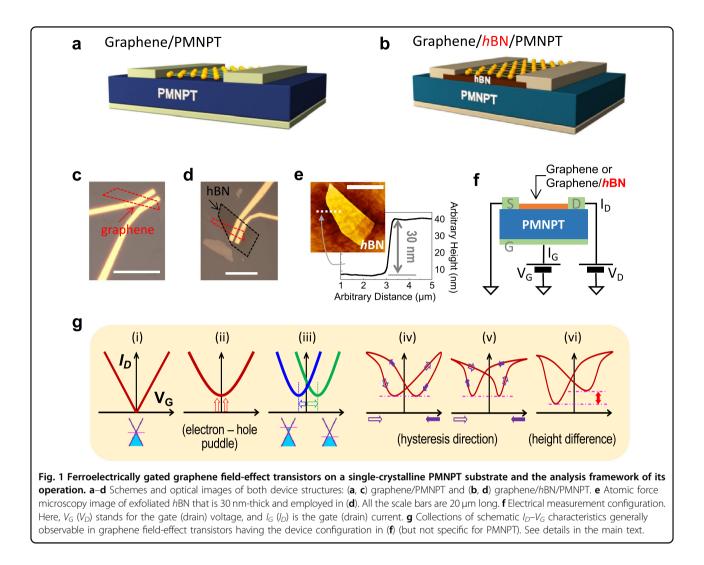

We designed and investigated two types of graphene devices in the configuration of a back-gated transistor, where a 100- $\mu$ m-thick ferroelectric single-crystal PMNPT oriented along the (001) direction substrate (IBULE Photonics, Republic of Korea) was employed as a back-gate dielectric layer. For one type, there was direct contact between graphene and PMNPT, while the other type included a hexagonal boron nitride (*h*BN) layer between graphene and PMNPT, which provides an atomically flat surface for graphene. The illustrations of the basic devices are depicted in Fig. 1a, b.

After mechanically exfoliating the graphene layer on a polymethyl methacrylate (PMMA)-coated silicon substrate and the *h*BN layer (HQ Graphene, Netherlands) on a PMNPT substrate, the graphene was transferred onto the flat surface area of PMNPT (see details in Figs. S1, S2 in the Supplementary Information (SI)) or onto *h*BN/ PMNPT by using the dry-transfer method. Standard e-beam lithography was used to form the source and drain electrodes with Au/Cr bimetal layers.

### Fabricated device inspection

The top-view optical images of both fabricated devices are depicted in Fig. 1c, d. The layer numbers of exfoliated graphene samples were estimated from the Raman spectra (Renishaw Raman, UK), which confirmed that all the graphene flakes were monolayers (Fig. S3 in SI). The thickness of the *h*BN layer was approximately 30 nm, as depicted in Fig. 1e, which was measured by the tapping mode of the atomic force microscope (AFM) instrument (Hitachi Hightech, Japan). The surface topography and ferroelectric domain of PMNPT were obtained simultaneously using the AFM instrument NX10 (Park systems, Republic of Korea).

### **Electrical characterization**

The electrical transport was measured inside the Physical Property Measurement System (PPMS, Quantum Design Inc., USA) using an Agilent B1500A (Keysight, USA). The standard electrical measurement setup for three-terminal back-gated field-effect transistors was configured, as shown in Fig. 1f. The standard procedures for the device operation are described as follows. For  $V_G$ sweeps within a specific range,  $V_G$  starts from 0 V and increases to a positive maximum. Then,  $V_G$  decreases from that positive maximum to the negative maximum. Finally,  $V_G$  moves again from that negative maximum to 0 V. During the sweep,  $V_G$  varies continuously without breaking. More specifically, in Fig. 2, the right arrow in the legend box corresponds to an increasing  $V_G$  from the negative maximum to 0 V and from 0 V to the positive maximum, while the left arrow corresponds to the movement of  $V_G$  from positive to negative.

# Analysis framework for hysteretic charge conduction in graphene devices

Various hysteresis curves, frequently observed in many electrical transport experiments of graphene field-effect transistors, can be understood systematically in the framework introduced in Fig. 1g. If an insulator such as SiO<sub>2</sub> was employed as a gate dielectric, (in other words, when PMNPT was replaced with SiO<sub>2</sub> in Fig. 1f), then the drain current ( $I_D$ ) versus the gate voltage ( $V_G$ ), *i.e.*, the  $I_D-V_G$ plot, depicts a typical V-shaped curve, as shown in Fig. 1g (i), where zero conductance at zero gate voltage was expected owing to graphene's intrinsic Dirac-cone band

structure, in an ideal case. However, electron-hole puddles are inevitably formed in real samples with spatial inhomogeneity<sup>53</sup>. Therefore, the minimum conductance is generally not zero, but a finite value exists at the charge neutrality point (CNP), as shown in Fig. 1g (ii). In addition, imperfections such as defects, impurities, or unintentional doping during device fabrication processes can also move CNPs to the left (electron doping) or to the right (hole doping), depending on the chemical potential shift in Fig. 1g (iii).

When  $I_D-V_G$  data curves are experimentally obtained during  $V_G$  sweeps, various hysteretic conductances can appear, as shown in Fig. 1g (iv–vi), with different hysteresis directions and mixtures of many complicated behaviors. For a clear understanding, careful analysis between charge trap phenomena and the characteristics of gate dielectrics is needed. In this work, a ferroelectric singlecrystal PMNPT was used as a gate dielectric, and the effect of ferroelectricity on the charge conduction of graphene was intensively studied.

### **Results and discussion**

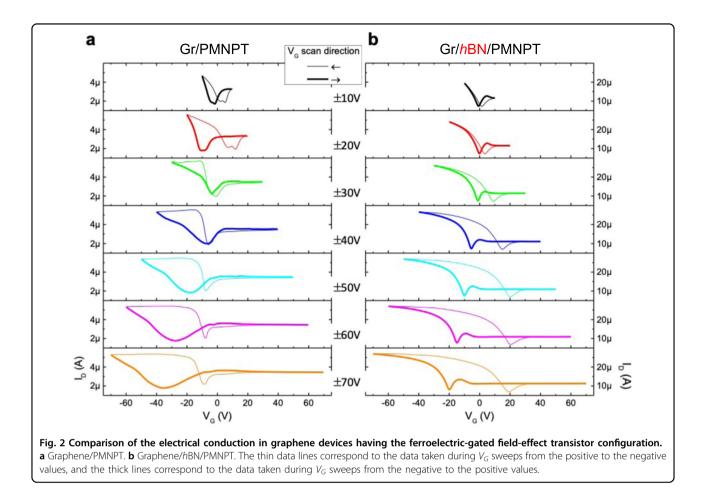

Figure 2 presents the  $I_D - V_G$  curves for grapheneferroelectric transistors with a graphene/PMNPT structure and that of graphene/hBN/PMNPT at different  $V_G$  sweep ranges from ±10 to ±70 V with a 10-V interval. For the graphene/PMNPT sample in Fig. 2a, the  $I_D-V_G$  curves in the small  $V_G$  sweep range depend on the initial polarization states of the PMNPT substrate, which were not well identified. However, as the  $V_G$  sweep range increases to cover the coercive voltage of the PMNPT substrate, clear hysteretic  $I_D - V_G$  curves appear with ferroelectric switching, and considerably asymmetric shapes of  $I_D - V_G$  curves are obtained for this graphene/PMNPT sample<sup>54</sup>. In detail, the  $V_G$  sweep from a positive maximum to a negative maximum gives a sharp transition from *n*- to *p*-type carrier conversion in the narrow  $V_G$  range (approximately between -10 V and 0 V) near the CNP located in the negative  $V_G$  region. However, a  $V_G$  sweep in the opposite direction, *i.e.*, from a negative maximum to a positive maximum, gives the  $I_D$  variation in a much broader  $V_G$  range.

On the other hand, in Fig. 2b, the  $I_D - V_G$  curves of the graphene/hBN/PMNPT sample show a hysteretic V-shaped conductance variation with respect to  $V_G$ . Two clearly separated CNPs, each of which corresponds to the opposite  $V_G$  sweep directions, indicate that the effect of ferroelectric switching in PMNPT significantly affects the charge conduction through graphene. However, it is intriguing to note that the hysteresis direction is not the same as what is expected in the conventional ferroelectric field-effect transistor, but it seems to be related to conventional charge trap memory behavior (as in Fig. 1g (iv, v))<sup>55,56</sup>. One additional consideration is that the  $I_D - V_G$  curves in a positive  $V_G$ region with electron majority carriers do not show a continuous  $I_D$  increase with increasing  $V_G$  but anomalously exhibit complete saturation in both the graphene/PMNPT and graphene/hBN/PMNPT cases.

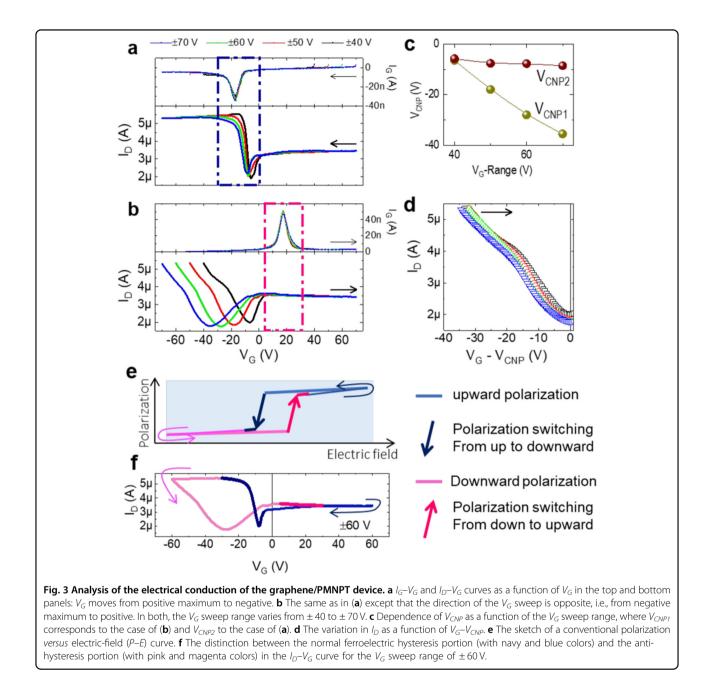

The  $I_D-V_G$  curves for the graphene/PMNPT sample in Fig. 2a are analyzed in Fig. 3. From the device structure of the ferroelectric field-effect transistor, the gate current  $(I_G)$  passing through the ferroelectric substrate shows a peak when ferroelectric switching occurs during the  $V_G$ sweep<sup>29,33</sup>. Fig. 3a shows the collection of  $I_G-V_G$  curves and that of the corresponding  $I_D-V_G$  curves taken from Fig. 2a for the  $V_G$  scans from positive to negative. In the top panel, the  $I_G$  peak positions are almost the same for all different  $V_G$  sweeps, representing the ferroelectric switching of the PMNPT substrate<sup>29,33</sup>. This clearly implies that when  $V_G$  moves from positive to negative values, normal ferroelectric switching occurs irrespective of the  $V_G$  sweep range. Additionally, in the bottom panel, the sudden increase in  $I_D$  after passing CNP indicates that the majority carriers rapidly change from electrons to holes in the graphene channel (which is schematically illustrated in Figure S4 in SI).

However, for the  $V_G$  sweep from negative maximum to positive, as depicted in Fig. 3b, the  $I_D$  decreases immediately after the  $V_G$  sweep direction changes. This observation deviates from the expectation that the strong ferroelectric polarization field would freeze the carrier density in graphene. Another noticeable feature is that the  $I_D$  shows a complete saturation behavior when  $V_G$ passes the ferroelectric switching region, as shown in Fig. 2b. It is remarkable that  $I_D$  does not move at all inside the dash-dotted square box in Fig. 3b, where the  $I_G$  peaks appear clearly. This surely indicates that the ferroelectricity in PMNPT is decoupled from charge conduction in graphene during the  $V_G$  sweep from negative maximum to positive.

Figure 3c shows the CNP movement as a function of the  $V_G$  sweep range. It is noticeable that the position of CNP1 (*i.e.*,  $V_{CNP1}$  defined as the CNP during the  $V_G$  sweep from a negative maximum to a positive maximum corresponding to Fig. 3b) changes considerably, but that of CNP2 (*i.e.*,  $V_{CNP2}$  in the opposite  $V_G$  sweep direction corresponding to Fig. 3a) does not change substantially. Because ferroelectric switching is independent of the  $V_G$  sweep range only if  $V_G$  is larger than the coercive voltage, CNP2 and the results in Fig. 3a can be closely related to the result of direct ferroelectric coupling between graphene and PMNPT. However, the sensitivity of CNP1 to

variations in the  $V_G$  sweep range may not be primarily governed by ferroelectricity, but other mechanisms, such as charge trapping, play an important role.

In addition, parts of the data curves in the hole majority (*p*-type) region in Fig. 3b are taken and plotted as a function of  $V_G - V_{CNP1}$  in Fig. 3d. These parts are considerably similar to each other, indicating that the conductance variation in the hole-majority region is almost the same, irrespective of the  $V_G$  sweep range. However, the position of CNP1 only shifts linearly according to the negative maximum  $V_G$  values, as shown in Fig. 3c. Such results suggest the plausibility of the trapped holes, which

significantly affect the performance of the graphene/ PMNPT device. Therefore, the number of trapped holes seems to be proportional to the difference between the coercive voltage and the negative maximum  $V_G$ , and trapped charges eventually compensate for the ferroelectric polarization field. Such phenomena can be alternatively interpreted in terms of ferroelectric-polarizationassisted charge trapping, which is to be discussed later.

To help intuitively understand this conductance hysteresis of graphene/PMNPT, we sketch a simplified polarization versus electric field (P-E) curve in Fig. 3e and compare it with the real data in Fig. 3f. From the viewpoint of the ferroelectric polarization state, the *P*–*E* curve in Fig. 3e can be divided into two parts: one for the polarizationup state and the other for the polarization-down state (which are drawn with the solid, blue-colored line and pink-colored line, respectively). In Fig. 3f, the  $I_D - V_G$  curve with a  $V_G$  sweep range of  $\pm 60$  V is plotted again as an example among many  $I_D - V_G$  curves in Fig. 2a, where the data line colors are chosen to match those in Fig. 3e. From a comparison between Fig. 3e, f, for the polarization-up state (*i.e.*, the navy and blue colors half-cycle in Fig. 3e),  $I_D$ does not change much while the polarization-up state is maintained, and  $I_D$  varies drastically when ferroelectric switching occurs. This result apparently indicates that the ferroelectricity directly affects the graphene charge carrier<sup>17,18,20–23</sup>. Notably, the majority charge carrier in this half-cycle is an electron, and it changes to a hole when ferroelectric switching occurs.

On the other hand, the polarization-down state (i.e., the pink and magenta colors half-cycle in Fig. 3e) gives two different  $I_D$  values in the negative  $V_G$  region depending on the  $V_G$  sweep direction, and  $I_D$  is almost constant in the  $V_G$ region of ferroelectric switching. These behaviors indicate that the graphene's electrical conduction does not seem to be directly coupled with the ferroelectricity of the PMNPT. Therefore, the origin of the overall asymmetric shape in the  $I_D - V_G$  curve can be ascribed to carrier-type-dependent interfacial charge trapping at the graphene/PMNPT interface. In other words, the interfacial trap sites are carrier dependent; at these sites, only holes are strongly trapped at the interface because of the negative  $V_G$  in combination with ferroelectric polarization<sup>28</sup>. The detrapping processes of hole carriers occur by performing ferroelectric switching in the opposite direction with no interfacial charge trapping phenomena in the largely positive  $V_G$  regions.

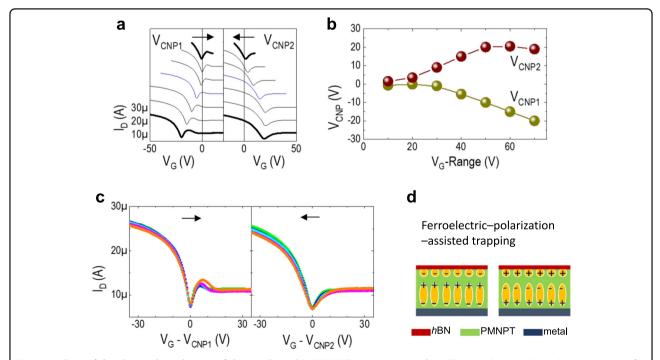

In Fig. 4, we depict the detailed analysis for the graphene/*h*BN/PMNPT system illustrated in Fig. 2b. The positions of  $V_{CNP1}$  and  $V_{CNP2}$  move in the opposite direction as the  $V_G$  sweep range increases, as depicted in Fig. 4a, and their dependencies on the  $V_G$  sweep range are plotted in Fig. 4b. It is evident that the hysteresis becomes larger as the  $V_G$  scans wider. However, their tendency is different for the  $V_G$  sweep ranges wider than ±50 V,

**Fig. 4 Analysis of the electrical conduction of the graphene**/*h***BN/PMNPT transistor sample. a** The scan-direction-dependent  $I_D-V_G$  curves for the  $V_G$  sweep from negative to positive (left panel) and from positive to negative (right panel). **b** Dependence of  $V_{CNP}$  as a function of the  $V_G$  range in each  $V_G$  sweep direction. **c** The replot of the data in Fig. 4a as a function of  $V_G-V_{CNP}$  along each  $V_G$  sweep direction. **d** Ferroelectric-polarization-assisted charge trapping phenomena. Here,  $V_{CNP1}$  ( $V_{CNP2}$ ) is defined as the voltage at the CNP for the  $V_G$  scan from negative (positive) to positive (negative).

showing an increasing behavior for  $V_{CNP1}$  and saturation for  $V_{CNP2}$ . Specifically, when the curves along the same sweep direction are collected as a function of  $V_G$  relative to the voltage at CNP, i.e.,  $V_G - V_{CNP1}$  and  $V_G - V_{CNP2}$  in Fig. 4c, they are almost identical irrespective of the  $V_G$ sweep range. All the results indicate that the electrical transport of graphene in the graphene/*h*BN/PMNPT system is not directly affected by ferroelectric switching but indirectly influenced by the ferroelectric-assisted charge trapping phenomena (which is depicted in Fig. 4d), thereby resulting in a shift of the  $V_{CNP}$  without any changes in the overall conductance behavior<sup>24–26,29,30,33,36,37,40</sup>.

Notably, the  $I_D-V_G$  curves for both graphene/PMNPT and graphene/*h*BN/PMNPT samples show a similar  $I_D$  saturation in the large positive  $V_G$  regions. The most intuitive explanation for such a clear  $I_D$  saturation is the effect of saturated ferroelectric polarization<sup>26,37</sup>. In the case of graphene/PMNPT, direct ferroelectricity-controlled charge carrier modulation can be used to explain the saturating behavior, as depicted in Fig. 3. However, for graphene/*h*BN/

PMNPT, the ferroelectric-assisted charge trapping model introduced in the abovementioned paragraph in Fig. 4d can be used to explain the result. The model includes the deeper charge trap energy due to the Coulomb interaction of ferroelectric polarization, as depicted in Fig. 4d. Compared with the conventional charge trapping in normal dielectrics<sup>56–61</sup>, the interfacial charge trapping between the normal dielectric and ferroelectric layers might be considerably stronger. It can also deepen the energy level of shallow trap sites, consequently increasing the number of trap sites<sup>55,56</sup>. In addition, the screening of ferroelectric polarization switching can hinder the appearance of variations in the  $I_D-V_G$  curves during ferroelectric switching. Therefore, the interaction between the trapped charges at the surface of the ferroelectric layer and the ferroelectrically polarized electric dipoles is critical to explain the data observed in Fig. 4.

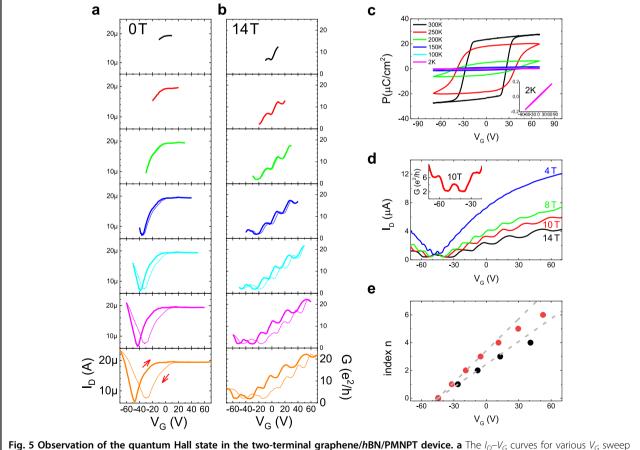

From Fig. 5, the quality of our device with graphene/ *h*BN/PMNPT can be verified by observing the quantum Hall phenomena. At a low temperature of 2 K, the  $V_G$ scan demonstrates a nonhysteretic  $I_D$ – $V_G$  behavior at

Fig. 5 Observation of the quantum Hall state in the two-terminal graphene/hBN/PMNPT device. a The  $I_D-V_G$  curves for various  $V_G$  sweep ranges at 2 K without a magnetic field. **b** The two-terminal quantum Hall conductance at 2 K and 14 Tesla. **c** The P-E curve as a function of temperature. **d** The  $I_D-V_G$  curves at 2 K under various magnetic fields. The inset shows the enlarged quantum Hall conductance data at 10 Tesla. **e** The peak positions of the derivatives of the  $I_D-V_G$  curves for 10 (red circles) and 14 Tesla (black circles) in (**d**), showing a delay in the gate voltage in the development of the next quantum Hall states above 0 V.

narrow  $V_G$  sweep ranges, but it becomes hysteretic as the  $V_G$  sweep range exceeds approximately  $\pm 40$  V, as depicted in Fig. 5a. Such a hysteresis tendency is identical to that in the case in which guantum Hall conductance is observed at 14 Tesla, as depicted in Fig. 5b. Because ferroelectric switching does not occur with frozen polarization at low temperatures, as exhibited in Fig. 5c, the hysteresis in Fig. 5a, b can be attributed to the effect of charge trapping at the interfaces inside the device. From the two-terminal quantum Hall conductance, it is reasonable to assume that charge trapping occurs at the interface between hBN and PMNPT but not at the interface between hBN and graphene<sup>61</sup>. In addition, the  $V_{CNP}$  at 2 K significantly shifts in the negative  $V_G$  region, which corresponds to the intrinsic electron-doping effect of graphene at low temperatures. The origin of this phenomenon can be considered together with the enhanced saturation current in the high  $V_G$  region, where the saturation current is approximately 20 µA at 2 K but approximately 10 µA at 300 K. This means that the effective electric field applied to the graphene is higher at 2 K than that at 300 K.

In Fig. 5d, we depict the emergence of quantum Hall phenomena in graphene under high magnetic fields, confirming the well-defined states, especially for the filling

factor v = 2 and 6, as presented in the inset. Only a few previous reports have shown the quantum Hall state of graphene on a ferroelectric substrate<sup>26,62</sup>. It seems that the 30 nm-thick hBN layer, which functions as an atomically flat thin substrate for graphene<sup>63</sup>, facilitates the decoupling of the ferroelectric field and graphene. In addition, the trapped charges at the interface between hBN and PMNPT do not hinder the formation of the quantum Hall state because the graphene channel is separate from those traps. On closer examination, the onset  $V_G$  of successive quantum Hall states depicted in Fig. 5e becomes delayed as the index becomes higher. This implies that the number of induced charge carriers decreases owing to charge trapping<sup>64</sup>, and it partially contributes to the  $I_D$  saturation behavior in the large positive  $V_G$  region at a zero magnetic field.

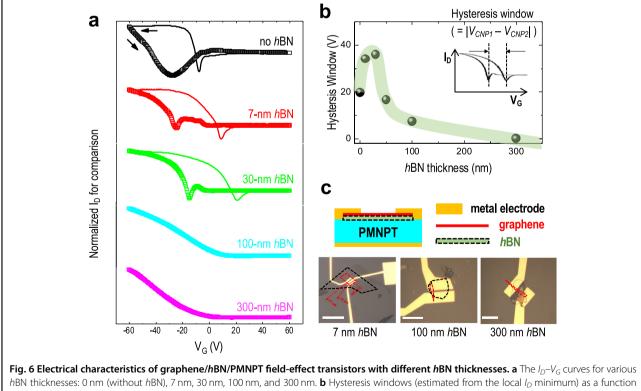

To support the proposed mechanism with more experimental evidence, we collected the results of systematic fabrications and measurements for graphene/hBN/PMNPT devices while varying hBN thicknesses from 0 nm (i.e., without hBN) to 300 nm, as presented in Fig. 6. The thickness variation in hBN flakes enables the qualitative assessment of ferroelectric-assisted charge trapping by controlling the effect of the ferroelectric substrate on the charge conduction of graphene. In Fig. 6a, we plotted

*h*BN thicknesses: 0 nm (without *h*BN), 7 nm, 30 nm, 100 nm, and 300 nm. **b** Hysteresis windows (estimated from the local  $I_D$  minimum) as a function of *h*BN thicknesse. **c** Schematic illustration of the device structure and optical images of three fabricated samples with *h*BN thicknesses of 7 nm, 100 nm, and 300 nm. Red and black lines indicate graphene and *h*BN flakes, respectively. All the scale bars in (**c**) are 20 µm long, and the notation of  $V_{CNP2}$  (and  $V_{CNP2}$ ) in (**b**) is identical to that defined in Fig. 4.

the  $I_D-V_G$  curves of graphene/*h*BN/PMNPT field-effect transistors (with a device structure identical to that in Fig. 1b, f) with *h*BN thicknesses of approximately 0, 7, 30, 100, and 300 nm. Here, the curves of 0- and 30 nm-thick *h*BN samples are the same as those in Fig. 2. For *h*BN flakes 300 nm and 100 nm-thick, the effect of ferroelectricity from the PMNPT substrate was so weak that there was little hysteresis in the  $I_D-V_G$  curves. However, in the cases of 30 nm-thick and 7 nm-thick *h*BN flakes, the hysteretic  $I_D-V_G$  curves clearly appeared due to the significant effect of ferroelectricity from the PMNPT substrate.

In addition, Fig. 6b shows the hysteresis window defined as the  $V_G$  gap between  $V_{CNP1}$  and  $V_{CNP2}$  (with the same notation in Fig. 4) for each sample in Fig. 6a. Here, the data value for a 50 nm-thick hBN sample was estimated from our former work<sup>29,33</sup>. The general trend is that hysteresis is very weak in thick *h*BN samples but becomes clear and becomes larger in thinner hBN samples with anti-hysteresis characteristics. Therefore, we can conclude that the hysteresis occurring in graphene/hBN/PMNPT devices is substantially related to the ferroelectricity in PMNPT in combination with interfacial charge trapping between hBN and PMNPT, which is interpreted as ferroelectric polarization-assisted charge trapping. However, it is noteworthy that the 'no hBN' case (i.e., direct contact between graphene and PMNPT, as shown in Fig. 1a) deviates from that trend, which can be ascribed to the results of direct ferroelectric coupling between graphene and PMNPT, at least in the case of electron-majority charge carriers in graphene. Figure 6c is given for a simple side-view illustration of the graphene/hBN/PMNPT device under test and the top-view optical images of the fabricated devices having hBN thicknesses of 7, 100 and 300 nm. The experimental data of hBN's thicknesses are included in Fig. S5 in SI.

### Conclusions

The charge transport of graphene in terms of grapheneferroelectric interactions is studied using graphene transistor devices with ferroelectric single-crystal PMNPT gate dielectrics. By comparing two device configurations, i.e., graphene/PMNPT and graphene/hBN/PMNPT, the direct control of the graphene conductance via ferroelectric polarization switching and the indirect control via polarization-assisted charge trapping at the interface between hBN and PMNPT could be identified. The observed quantum Hall conductance in the graphene/ *h*BN/PMNPT sample confirms the high device quality and the decoupling of the ferroelectric polarization field from the intrinsic charge conduction of graphene. All these results confirm that charge carriers in graphene can be modulated using the ferroelectricity of the contacting PMNPT substrate. However, such coupling can be hindered because of carrier-dependent interfacial charge trapping or ferroelectricity-assisted charge trapping phenomena, in which charges are trapped at the interface of the ferroelectric oxide and 2D materials.

### Acknowledgements

This work was supported by the National Research Foundation (NRF-2021R1A2C2005281, NRF-2018K1A4A3A01064272, and NRF-2021R1A2C2013289) funded by the Ministry of Science and ICT, Republic of Korea. This work was also supported in part by the Advanced Facility Center for Quantum Technology.

### Author contributions

N.P. developed all devices; J.P. and T.K.C. prepared the experimental setups, and N.P., H-Y.K, and D.S. conducted transport measurements. N.P., H-J.K., and D.S. wrote the initial draft, and H.L., H-Y.K., and D.S. analyzed the results in detail and finalized the manuscript. H-Y.K and D.S. designed and supervised the project.

### **Competing interests**

The authors declare no competing interests.

### Publisher's note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

**Supplementary information** The online version contains supplementary material available at https://doi.org/10.1038/s41427-022-00404-5.

Received: 8 December 2021 Revised: 18 April 2022 Accepted: 18 May 2022. Published online: 15 July 2022

#### References

- 1. Devonshire, A. F. Theory of ferroelectrics. Adv. Phys. 3, 85-130 (1954).

- 2. Webb, J. F. On the physics of ferroelectrics. Sci. Prog. 86, 203-234 (2003).

- Chandra, P. & Littlewood, P. B. in *Physics of Ferroelectrics: A Modern* Perspective (eds Rabe, Ahn, & Triscone) Ch. 3, 69–116 (Springer Berlin Heidelberg, 2007).

- Shu-Yau, W. A new ferroelectric memory device, metal-ferroelectricsemiconductor transistor. *IEEE Trans. Electron Devices* 21, 499–504 (1974).

- Kaneko, Y., Tanaka, H., Ueda, M., Kato, Y. & Fujii, E. A dual-channel ferroelectricgate field-effect transistor enabling nand-type memory characteristics. *IEEE Trans. Electron Devices* 58, 1311–1318 (2011).

- Mathews, S., Ramesh, R., Venkatesan, T. & Benedetto, J. Ferroelectric field effect transistor based on epitaxial perovskite heterostructures. *Science* 276, 238 (1997).

- Tokumitsu, E., Nakamura, R. & Ishiwara, H. Nonvolatile memory operations of metal-ferroelectric-insulator-semiconductor (MFIS) FETs using PLZT/STO/ Si(100) structures. *IEEE Electron Device Lett.* 18, 160–162 (1997).

- Zhao, T. et al. Colossal magnetoresistive manganite-based ferroelectric fieldeffect transistor on Si. Appl. Phys. Lett. 84, 750–752 (2004).

- Nakao, Y., Nakamura, T., Kamisawa, A. & Takasu, H. Study on ferroelectric thin films for application to NDRO non-volatile memories. *Integr. Ferroelectr.* 6, 23–34 (2006).

- Naber, R. C. G. et al. High-performance solution-processed polymer ferroelectric field-effect transistors. *Nat. Mater.* 4, 243–248 (2005).

- Stadlober, B. et al. Transparent pyroelectric sensors and organic field-effect transistors with fluorinated polymers: Steps towards organic infrared detectors. *IEEE Trans. Dielectr. Electr. Insul.* 13, 1087–1092 (2006).

- Chang, J. et al. Polymeric gate dielectric interlayer of cross-linkable poly(styrene-r-methylmethacrylate) copolymer for ferroelectric PVDF-TrFE field effect transistor memory. *Org. Electron.* **10**, 849–856 (2009).

- Kang, S. J. et al. Printable ferroelectric PVDF/PMMA blend films with ultralow roughness for low voltage non-volatile polymer memory. *Adv. Funct. Mater.* 19, 2812–2818 (2009).

- Georgakopoulos, S., del Pozo, F. G. & Mas-Torrent, M. Flexible organic transistors based on a solution-sheared PVDF insulator. J. Mater. Chem. C. 3, 12199–12202 (2015).

- Thuau, D. et al. Mechanical strain induced changes in electrical characteristics of flexible, non-volatile ferroelectric OFET based memory. *Org. Electron.* 40, 30–35 (2017).

- Anwar, S. et al. Polymer field-effect transistor memory based on a ferroelectric nylon gate insulator. J. Mater. Chem. C. 8, 5535–5540 (2020).

- Zheng, Y. et al. Gate-controlled nonvolatile graphene-ferroelectric memory. *Appl. Phys. Lett.* 94, 163505 (2009).

- Kim, K. L. et al. Epitaxial growth of thin ferroelectric polymer films on graphene layer for fully transparent and flexible nonvolatile memory. *Nano Lett.* 16, 334–340 (2016).

- Sun, Y.-L. et al. Tunable transport characteristics of double-gated graphene field-effect transistors using P(VDF-TrFE) ferroelectric gating. *Carbon* 96, 695–700 (2016).

- Wang, X. et al. Flexible graphene field effect transistor with ferroelectric polymer gate. Opt. Quantum Electron. 48, 345 (2016).

- Heidler, J., Yang, S., Feng, X., Müllen, K. & Asadi, K. Ferroelectric field-effect transistors based on solution-processed electrochemically exfoliated graphene. *Solid State Electron* 144, 90–94 (2018).

- Wang, X. et al. Graphene Dirac point tuned by ferroelectric polarization field. Nanotechnology 29, 134002 (2018).

- Figueroa, K. S. et al. Controlled doping of graphene by impurity charge compensation via a polarized ferroelectric polymer. J. Appl. Phys. 127, 125503 (2020).

- Hong, X. et al. Unusual resistance hysteresis in n-layer graphene field effect transistors fabricated on ferroelectric Pb(Zr<sub>0.2</sub>Ti<sub>0.8</sub>)O<sub>3</sub>. *Appl. Phys. Lett.* 97, 033114 (2010).

- Song, E. B. et al. Robust bi-stable memory operation in single-layer graphene ferroelectric memory. *Appl. Phys. Lett.* **99**, 042109 (2011).

- Rajapitamahuni, A., Hoffman, J., Ahn, C. H. & Hong, X. Examining graphene field effect sensors for ferroelectric thin film studies. *Nano Lett.* **13**, 4374–4379 (2013).

- Yusuf, M. H., Nielsen, B., Dawber, M. & Du, X. Extrinsic and intrinsic charge trapping at the graphene/ferroelectric interface. *Nano Lett.* 14, 5437–5444 (2014).

- Ma, C. et al. Detangling extrinsic and intrinsic hysteresis for detecting dynamic switch of electric dipoles using graphene field-effect transistors on ferroelectric gates. *Nanoscale* 7, 18489–18497 (2015).

- Park, N. et al. Ferroelectric single-crystal gated graphene/hexagonal-BN/ferroelectric field-effect transistor. ACS Nano. 9, 10729–10736 (2015).

- Zhang, X.-W. et al. Temperature-dependent electrical transport properties in graphene/Pb(Zr<sub>04</sub>Ti<sub>0.6</sub>)O<sub>3</sub> field effect transistors. *Carbon* **93**, 384–392 (2015).

- Hinnefeld, J. H. et al. Single gate p-n junctions in graphene-ferroelectric devices. *Appl. Phys. Lett.* **108**, 203109 (2016).

- Kurchak, A. I., Morozovska, A. N. & Strikha, M. V. Hysteretic phenomena in GFET: Comprehensive theory and experiment. J. Appl. Phys. 122, 044504 (2017).

- Lipatov, A. et al. Polarization-dependent electronic transport in graphene/ Pb(Zr,Ti)O<sub>3</sub> ferroelectric field-effect transistors. *Adv. Electron. Mater.* 3, 1700020 (2017).

- Ma, C. et al. Detecting electric dipoles interaction at the interface of ferroelectric and electrolyte using graphene field effect transistors. ACS Appl. Mater. Interfaces 9, 4244–4252 (2017).

- 35. Lee, S. & Lee, Y. Graphene/lead-zirconate-titanate ferroelectric memory devices with tenacious retention characteristics. *Carbon* **126**, 176–182 (2018).

- Lipatov, A., Sharma, P., Gruverman, A. & Sinitskii, A. Optoelectrical molybdenum disulfide (MoS<sub>2</sub>)—ferroelectric memories. ACS Nano. 9, 8089–8098 (2015).

- Lu, Z. et al. Nonvolatile MoS<sub>2</sub> field effect transistors directly gated by single crystalline epitaxial ferroelectric. *Appl. Phys. Lett.* **111**, 023104 (2017).

- Jie, W. & Hao, J. Time-dependent transport characteristics of graphene tuned by ferroelectric polarization and interface charge trapping. *Nanoscale* 10, 328–335 (2018).

- Huang, H. et al. Ferroelectric polymer tuned two dimensional layered MoTe<sub>2</sub> photodetector. *RSC Adv.* 6, 87416–87421 (2016).

- 40. Sun, Y. et al. Temperature-dependent transport and hysteretic behaviors induced by interfacial states in MoS<sub>2</sub> field-effect transistors with lead-zirconate-titanate ferroelectric gating. *Nanotechnology* **28**, 045204 (2017).

- Wang, X. et al. Two-dimensional negative capacitance transistor with polyvinylidene fluoride-based ferroelectric polymer gating. *npj 2D Mater. Appl.* 1, 38 (2017).

- Wang, X. et al. Ferroelectric FET for nonvolatile memory application with twodimensional MoSe<sub>2</sub> channels. 2d Mater. 4, 025036 (2017).

- 43. Yin, L. et al. Ferroelectric-induced carrier modulation for ambipolar transition metal dichalcogenide transistors. *Appl. Phys. Lett.* **110**, 123106 (2017).

- Zhou, C. & Chai, Y. Ferroelectric-gated two-dimensional-material-based electron devices. Adv. Electron. Mater. 3, 1600400 (2017).

- Yin, C. et al. A ferroelectric relaxor polymer-enhanced p-type WSe<sub>2</sub> transistor. Nanoscale 10, 1727–1734 (2018).

- 46. Lu, H. et al. Nanodomain engineering in ferroelectric capacitors with graphene electrodes. *Nano Lett.* **16**, 6460–6466 (2016).

- Rogers, S. P., Xu, R., Pandya, S., Martin, L. W. & Shim, M. Slow conductance relaxation in graphene–ferroelectric field-effect transistors. *J. Phys. Chem. C.* 121, 7542–7548 (2017).

- Ding, J., Wen, L.-W., Li, H.-D., Kang, X.-B. & Zhang, J.-M. First-principles investigation of graphene on the ferroelectric LiNbO<sub>3</sub> (001) surface. *EPL* **104**, 17009 (2013).

- 49. Lu, H. et al. Ferroelectric tunnel junctions with graphene electrodes. *Nat. Commun.* **5**, 5518 (2014).

- Baeumer, C. et al. Ferroelectrically driven spatial carrier density modulation in graphene. Nat. Commun. 6, 6136 (2015).

- Yuan, S. et al. Ferroelectric-driven performance enhancement of graphene field-effect transistors based on vertical tunneling heterostructures. *Adv. Mater.* 28, 10048–10054 (2016).

- Dai, J.-Q., Cao, T.-F. & Wang, X.-W. Effect of surface termination on charge doping in graphene/BiFeO<sub>3</sub>(0001) hybrid structure. *J. Phys. Chem. C.* **122**, 17250–17260 (2018).

- Martin, J. et al. Observation of electron-hole puddles in graphene using a scanning single-electron transistor. *Nat. Phys.* 4, 144–148 (2008).

- Firsov, K. S. N. et al. Electric field effect in atomically thin carbon films. *Science* 306, 666–669 (2004).

- 55. Hong, A. J. et al. Graphene flash memory. ACS Nano. 5, 7812–7817 (2011).

- Lee, S., Lee, Y., Kim, S. M. & Song, E. B. Fully-transparent graphene charge-trap memory device with large memory window and long-term retention. *Carbon* 127, 70–76 (2018).

- 57. Liao, Z. M., Han, B. H., Zhou, Y. B. & Yu, D. P. Hysteresis reversion in graphene field-effect transistors. J. Chem. Phys. **133**, 044703 (2010).

- Wang, H., Wu, Y., Cong, C., Shang, J. & Yu, T. Hysteresis of electronic transport in graphene transistors. ACS Nano. 4, 7221–7228 (2010).

- Lee, Y. G. et al. Fast transient charging at the graphene/SiO<sub>2</sub> interface causing hysteretic device characteristics. *Appl. Phys. Lett.* 98, 183508 (2011).

- 60. Kang, C. G. et al. Mechanism of the effects of low temperature  $Al_2O_3$  passivation on graphene field effect transistors. *Carbon* **53**, 182–187 (2013).

- 61. Kang, H. et al. Quantum Hall conductance of graphene combined with charge-trap memory operation. *Nanotechnology* **26**, 345202 (2015).

- Zheng, Y. et al. Wafer-scale graphene/ferroelectric hybrid devices for lowvoltage electronics. *EPL* 93, 17002 (2011).

- Dean, C. R. et al. Boron nitride substrates for high-quality graphene electronics. Nat. Nanotechnol. 5, 722–726 (2010).

- Chau, T. K., Suh, D. & Kang, H. Detection of hidden localized states by the quantum Hall effect in graphene. *Curr. Appl. Phys.* 23, 26–29 (2021).