# PERSPECTIVE

# Open Access

# Next-generation ferroelectric domain-wall memories: principle and architecture

An Quan Jiang<sup>1</sup> and Yan Zhang<sup>1</sup>

## Abstract

The downscaling of commercial one-transistor-one capacitor ferroelectric memory cells is limited by the available signal window for the use of a charge integration readout technique. However, the erasable conducting charged walls that occur in insulating ferroelectrics can be used to read the bipolar domain states. Both out-of-plane and in-plane cell configurations are compared for the next sub-10-nm integration of ferroelectric domain wall memories with high reliability. It is highlighted that a nonvolatile read strategy of domain information within mesa-like cells under the application of a strong in-plane read field can enable a massive crossbar connection to reduce mobile charge accumulation at the walls and crosstalk currents from neighboring cells. The memory has extended application in analog data processing and neural networks.

## Introduction

Ferroelectric memories, which use bipolar domain orientations to store nonvolatile "0" and "1" data, have the advantages of ns-to-ps-scale programming times, almost unlimited cycle endurance, and low-energy consumption.<sup>1,2</sup> The domain size in these memories can be as small as a few nanometers,<sup>3</sup> which is ideal terabit-density storage. Unfortunately, the stored information is read out destructively through a charge integration process using commercial one-transistor–one capacitor (1T1C) or 2T2C architectures, where the signal is reduced with the downscaling of the cell.<sup>1</sup>

Alternative piezoelectric mechanical probes can be used to extract small domain information, but these probes are incompatible with current complementary metaloxide–semiconductor (CMOS) technology.<sup>4</sup> The channel current can be used to sense the bipolar domain orientations in the gate stack of a ferroelectric field-effect transistor, but this device unfortunately suffers from short retention times (ranging from a few days to months).<sup>5</sup> Another candidate structure for ferroelectric tunnel junction devices has also emerged based on the insertion

© The Author(s) 2019

of an ultrathin ferroelectric film (1–3 nm) between two metal electrodes, in which the quantum-mechanical tunneling current varies with the bipolar domain orientation.<sup>6</sup> However, the integration of monolithic ultrathin films that are free from misfits and defects on large-area silicon wafers in single domain patterns remains challenging. Ferroelectric diode memories, in which the polarity of a unidirectional diode's current can be reversed upon polarization flipping, can use comparatively thicker semiconducting thin films. However, the polarization fatigue and leakage currents become dominant after 10<sup>5</sup> write cycles.<sup>7</sup> These structures are far from the stage of reaching device-level integration.

## Out-of-plane domain wall memory

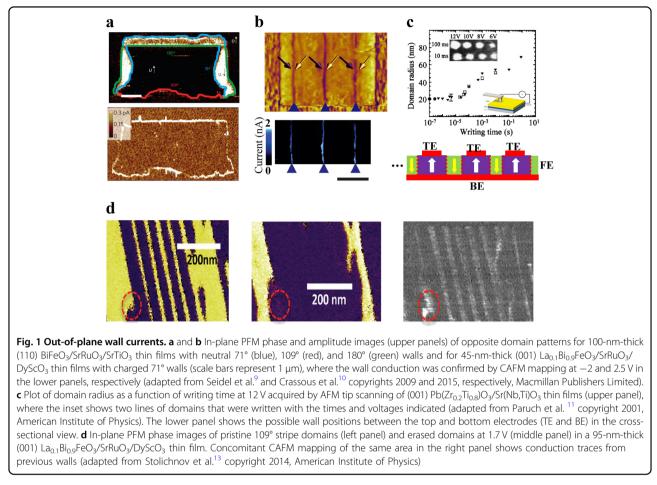

Ferroelectric domain wall memory can function using a "pure ionic" switching mechanism: the charged domain walls that occur in ferroelectric single crystals displayed giant metallic-like conductivity,<sup>8</sup> and the pA-scale currents of the neutral 109° and 180° domain walls in (110) BiFeO<sub>3</sub> thin films (indexed as pseudocubic) were observed during piezoresponse force microscopy (PFM) and conductive atomic force microscopy (CAFM) mapping of these films,<sup>9</sup> as shown in Fig. 1a and b, respectively. The

Correspondence: An Quan Jiang (aqjiang@fudan.edu.cn)

<sup>&</sup>lt;sup>1</sup>State Key Laboratory of ASIC & System, School of Microelectronics, Fudan University, 200433 Shanghai, China

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/.

conducting walls in insulating ferroelectrics can thus be used to read the polarization states.

The weak currents through the neutral walls can be enhanced through the creation of charged walls to accelerate the read speed of the memory. It has been found that the "trailing field" present in the tri-axial control of a scanning PFM probe tip over (001) La<sub>0.1</sub>Bi<sub>0.9</sub>FeO<sub>3</sub> thin films can create in-plane head-to-head and tail-to-tail polarization components that form ferroelastic charged domain walls, as shown in Fig. 1b (upper panel). The CAFM current map (shown in the lower panel) shows head-to-head wall currents that are as high as  $\sim 1.7$  nA.<sup>10</sup> Unfortunately, this current decays over time and drops to 0.2 nA after 10 h, which is far from the current required to drive fast-read circuits. Next, the sideways domain motion could lead to a misfit in the wall position outside the top electrode area (causing read failure) in a real memory device (lower panel, Fig. 1c), as confirmed by plots of the growing domain radius as a function of the writing time and the voltage measured using AFM tips with a radius of  $\sim 20$  nm (as shown in the upper panel).<sup>11</sup> Furthermore, continuous growth of a monodomain over a large-area silicon wafer is challenging, whereas inverted nanodomains generally have poor retention.<sup>12</sup> Finally, long-term persistent domain walls could accumulate opposite mobile charges to compensate for the domain boundary charge that causes the decay in the wall current. Fig. 1d shows an in-plane PFM phase image (left panel) of pristine  $109^{\circ}$  stripe domains within (001) La<sub>0.1</sub>Bi<sub>0.9</sub>FeO<sub>3</sub> thin films.<sup>13</sup> The CAFM scans at 1.5 V show no domain wall conduction until the voltage reaches 1.7 V, when domain switching occurs, as confirmed by the in-plane PFM phase image shown in the middle panel; a concomitant current signal appears at the original location of the erased wall, as shown by the CAFM map in the right panel.

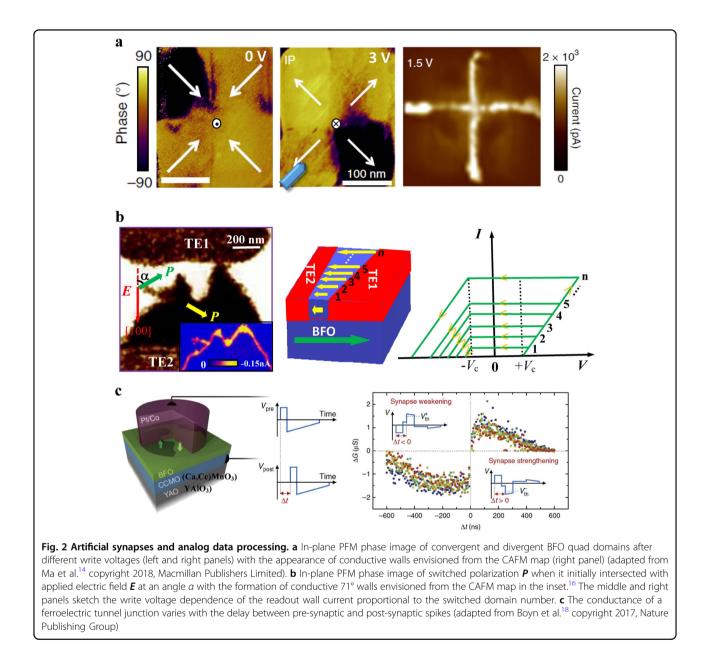

The wall currents can be stabilized over a period of several months in rhombohedral BFO nanoislands embedded within a tetragonal BFO thin-film matrix.<sup>14</sup> PFM and CAFM imaging showed that the pristine head-to-head walls formed by quad-domains within each island are centerconvergent and insulating, as shown in Fig. 2a. The walls become center-divergent and highly conductive once the tail-to-tail charged walls come into form after poling at +3 V, in contradiction to the highly conductive head-tohead walls observed in Fig. 1b. The confined cross-shaped walls have good contacts with the top and bottom electrodes, which open routes towards the mass manufacturing of out-of-plane domain-wall memory devices.

#### In-plane domain wall memory

Alternatively, information can be read from the tiny domain via the temporary generation of a high wall current near the film surface under the application of the in-plane read field (E) between the two top electrodes (TE1 and TE2).<sup>15,16</sup> Fig. 2b (left panel) shows an in-plane PFM phase image of two switched head-to-head 71° triangular domains in a (001) BiFeO<sub>3</sub> thin film,<sup>16</sup> where the in-plane polarization (P) intersects with E at an angle of  $\alpha$ .<sup>17</sup> The concomitant CAFM image presented in the inset shows the significantly higher electrical conductivity of the entire domain-wall region. The wall current increases nonlinearly with the reduction in the gap length to follow a space-charge-limited

conduction process with a thermal activation energy of 0.16 eV;<sup>16</sup> the current increases exponentially with the value of sin  $\alpha$  (0°  $\leq \alpha \leq 90$ °), and the wall current is more than 300 nA with  $\alpha = 90^{\circ}$ .<sup>17</sup> Once the switching pulse is removed, domain backswitching occurs and erases the walls within a time as short as 16 ns.<sup>16</sup> This temporary domain nature permits the nondestructive reading of nanodomain information while also avoiding long-term defect accumulation at the persistent walls.

The persistent wall current that is proportional to the switched domain number permits multilevel programming of analog data in a triangular geometrically shaped mesa-like cell,<sup>16</sup> as shown in the middle panel of Fig. 2b, where the coercive voltage increases linearly

with the distance between TE1 and TE2. The switched domain number and, thus, the wall current are proportional to the amplitude of a write voltage, as shown in the right panel, which highlights the superiority of the in-plane memory configuration over that of the out-of-plane memory in the storing of multilevel information.

Beyond analog data processing, domain wall memories can also be used in neural networks that require high speed, accurate, and repeatable programming of cells. The conductance based on ferroelectric tunnel junctions can mimic a nanosynapse in neuromorphic architecture that can be finely tuned by voltage pulses and set to evolve according to a biological learning rule called spike-timing-dependent plasticity (STDP),<sup>18</sup> as shown in Fig. 2c. Similarly, STDP can be harnessed from inhomogeneous polarization switching that occurs in both out-of-plane and in-plane domain wall memories.

### Read and write architecture

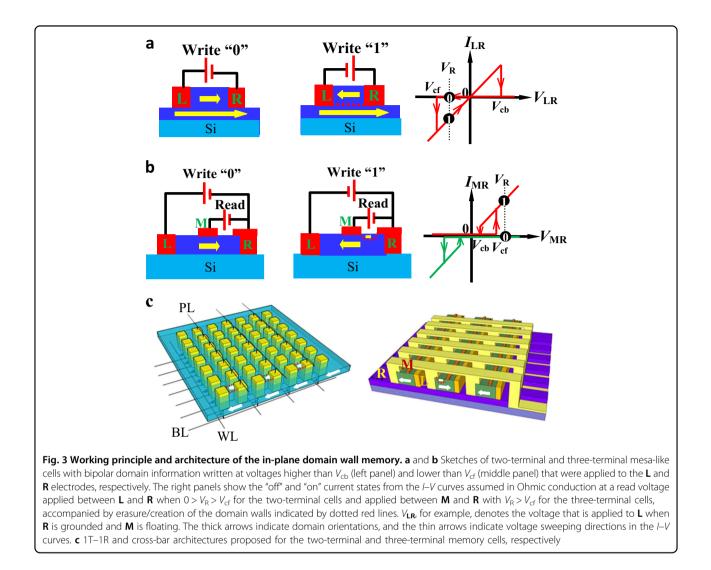

Figure 3a and b show two schemes for the in-plane domain wall memories in cross-sectional views, where each cell is etched into a mesa-like structure with left (L), middle (M), and right (R) electrodes. The L/cell/R structure forms a parallel-plate capacitor-like structure that provides efficient screening of polarization charge and stabilizes the written ferroelastic domains by eliminating stress-induced instability.<sup>12</sup> If the film has a monodomain structure with a large readout current at a small read voltage  $(V_R)$ , two-terminal cells etched into the partial film thickness are proposed, as shown in Fig. 3a; here, the written "0" and "1" domains are parallel/antiparallel to the unswitched bulk domain at the bottom (indicated by thick arrows in the horizontal projection) and accompany the erasure/creation of a persistent conductive wall (indicated by the dotted line) under application of a write voltage above the forward coercive voltage of  $V_{cb}$  or below the backward coercive voltage of  $V_{cf'}$  respectively. Later, the "off"/"on" currents can be read out when  $0 > V_R > V_{cb'}$  as shown in the right panel.

For thin films in multi-domain structures, threeterminal mesa-like cells that are etched into the entire film thickness are proposed, as shown in Fig. 3b, where the read field is concentrated between the two ends of **M** and **R** and **R** is partially extended over the cell surface. The outer **L** and **R** permit writing of the bipolar domains, which are both read out at  $V_{\rm R} > V_{\rm cf}$ . Because **E** is antiparallel to **P**, the partial domain switching that occurs near the film surface generates sufficiently high wall currents; after read termination, the switched domain back-switches to its previous orientation, thus avoiding long-term mobile charge accumulation at the wall regions.

In the two-terminal cells, the use of a onetransistor–one resistor (1T-1R) architecture leads to a dense cell occupation per unit area, as shown in Fig. 3c (left panel). Alternatively, a crossbar architecture is proposed for use in three-terminal cells for high reliability (right panel), where the wall elimination that occurs after the read operation can effectively minimize the crosstalk currents from neighboring cells.

During memory-device fabrication, the epitaxial growth of large-area ferroelectric thin films on Si substrates is required using the right buffer layers.<sup>19</sup> Otherwise, the wall currents decay quickly in the polycrystalline thin films due to insulating grain boundaries. Recently, a smart-cut technique has matured that can bond ferro-electric single-crystal thin films to Si circuits at room temperature,<sup>20</sup> which provides a great opportunity to develop the next-generation of domain wall memory.

#### Conclusions

Various readout techniques for high-density ferroelectric memories are compared; among these methods, the out-of-plane manipulation of conducting charged walls can allow read-out of the bipolar polarization states under a small applied voltage, but the long-term readout current is insufficient (0.2-2 nA) to drive the fast-read circuits required. In contrast, the in-plane manipulation of charged domains that occur on the surface of a memory cell permits the application of a strong read field to provide a significantly enhanced wall current (~300 nA). The domain back-switching (wall erasure) process after read termination can also avoid the accumulation of mobile defects at the walls and the crosstalk currents that occur in massive crossbar connections. Hopefully, ferroelectric single-crystal films bonded to the Si circuits will permit terabit-density integration of the ferroelectric domain wall memory using modern sub-10-nm-node CMOS technologies in the near future.

#### Acknowledgements

This work was supported by the Basic Research Project of Shanghai Science and Technology Innovation Action (grant number 17JC1400300), the National Natural Science Foundation of China (grant number 61674044), and the Program of Shanghai Subject Chief Scientist (grant number 17XD1400800). We thank David MacDonald, M.Sc., from Liwen Bianji, Edanz Editing China (www. liwenbianji.cn/ac), for editing the English text of a draft of this manuscript.

#### Conflict of interest

The authors declare that they have no conflict of interest.

#### Publisher's note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

# Received: 9 July 2018 Revised: 27 October 2018 Accepted: 13 November 2018.

Published online: 23 January 2019

#### References

- 1. Shimojo, Y. et al. High-density and high-speed 128 Mb chain FeRAM™ with SDRAM-compatible DDR2 interface. *Symp. VLSI Tech. Dig.* 218–219 (Japan Society of Applied Physics, 2009).

- Rana, D. S. et al. Understanding the nature of ultrafast polarization dynamics of ferroelectric memory in the multiferroic BiFeO<sub>3</sub>. *Adv. Mater.* **21**, 2881–5 (2009).

- Fong, D. D. et al. Ferroelectricity in ultrathin perovskite films. *Science* 304, 1650–3 (2004).

- Heck, J. et al. Ultra-high density MEMS probe memory device. *Microelectron.* Eng. 87, 1198–203 (2010).

- Li, T., Hsu, S. T., Ulrich, B. D., Evans, D. R. & Lee, J. J. One transistor ferroelectric memory with Pt/Pb<sub>3</sub>Ge<sub>3</sub>O<sub>11</sub>/Ir/Poly-Si/SiO<sub>2</sub>/Si gate stack. *IEEE Electr. Dev. Lett.* 23, 339–41 (2002).

- Garcia, V. et al. Giant tunnel electroresistance for non-destructive readout of ferroelectric states. *Nature* 460, 81–84 (2009).

- Jiang, A. Q. et al. A resistive memory in semiconducting BiFeO<sub>3</sub> thin-film capacitors. *Adv. Mater.* 23, 1277–81 (2011).

- Sluka, T., Tagantsev, A. K., Bednyakov, P. & Setter, N. Free-electron gas at charged domain walls in insulating BaTiO<sub>3</sub>. *Nat. Commun.* 4, 1808 (2013).

- Seidel, J. et al. Conduction at domain walls in oxide multiferroics. Nat. Mater. 8, 229–34 (2009).

- Crassous, A., Sluka, T., Tagantsev, A. K. & Setter, N. Polarization charge as a reconfigurable quasi-dopant in ferroelectric thin films. *Nat. Nanotech.* 10, 614–8 (2015).

- Paruch, P., Tybell, T. & Triscone, J.-M. Nanoscale control of ferroelectric polarization and domain size in epitaxial Pb.Zr<sub>0.2</sub>Ti<sub>0.8</sub>O<sub>3</sub> thin films. *Appl. Phys. Lett.* **79**, 530–2 (2001).

- Baek, S. H. et al. Ferroelastic switching for nanoscale non-volatile magnetoelectric devices. *Nat. Mater.* 17, 309–14 (2010).

- Stolichnov, I. et al. Persistent conductive footprints of 109° domain walls in bismuth ferrite films. *Appl. Phys. Lett.* **104**, 132902 (2014).

- Ma, J. et al. Controllable conductive readout in selfassembled, topologically confined ferroelectric domain walls. *Nat. Nanotech.* 13, 947–52 (2018).

- Sharma, P. et al. Nonvolatile ferroelectric domain wall memory. Sci. Adv. 3, e1700512 (2017).

- Jiang, J. et al. Temporary formation of highly conducting domain walls for non-destructive read-out of ferroelectric domain-wall resistance switching memories. *Nat. Mater.* 17, 49–55 (2018).

- Bai, Z. L. et al. Hierarchical domain structure and extremely large wall current in epitaxial BiFeO<sub>3</sub> thin films. *Adv. Funct. Mater.* 28, 1801725 (2018).

- Boyn, S. et al. Learning through ferroelectric domain dynamics in solid-state synapses. *Nat. Commun.* 8, 14736 (2017).

- Rao, S. S. et al. Interface magnetism in epitaxial BiFeO<sub>3</sub>-La<sub>0.7</sub>Sr<sub>0.3</sub>MnO<sub>3</sub> heterostructures integrated on Si (100). *Nano Lett.* **13**, 5814–5821 (2013).

- Wang, C. et al. Integrated lithium niobate electro-optic modulators operating at CMOS-compatible voltages. *Nature* 562, 101–4 (2018).