Abstract

The electromagnetic manipulation of isolated atoms has led to many advances in physics, from laser cooling1 and Bose–Einstein condensation of cold gases2 to the precise quantum control of individual atomic ions3. Work on miniaturizing electromagnetic traps to the micrometre scale promises even higher levels of control and reliability4. Compared with ‘chip traps’ for confining neutral atoms5,6,7, ion traps with similar dimensions and power dissipation offer much higher confinement forces and allow unparalleled control at the single-atom level. Moreover, ion microtraps are of great interest in the development of miniature mass-spectrometer arrays8, compact atomic clocks9 and, most notably, large-scale quantum information processors10,11. Here we report the operation of a micrometre-scale ion trap, fabricated on a monolithic chip using semiconductor micro-electromechanical systems (MEMS) technology. We confine, laser cool and measure heating of a single 111Cd+ ion in an integrated radiofrequency trap etched from a doped gallium-arsenide heterostructure.

Similar content being viewed by others

Main

Current ion-trap research is largely driven by the quest to build a quantum information processor12, where quantum bits (qubits) of information are stored in individual atomic ions and connected through a common interaction with a phonon3,13 or photon14,15 field. The fundamental experimental requirements for quantum processing have all been met with ion traps, including demonstrations of multi-qubit quantum gates and small algorithms16,17,18. Effort in this area is now focused on the scaling of ion traps to host much larger numbers of qubits, perhaps by shuttling individual atoms through a complex maze of ion-trap electrodes13,14. The natural host for such a scalable system is an integrated ion-trap chip. We confine single 111Cd+ qubit ions in a radiofrequency linear ion trap3,19 on a chip by applying a combination of static and oscillating electric potentials to integrated electrodes20. The electrodes are lithographically patterned from a monolithic semiconductor substrate, eliminating the need for manual assembly and alignment of individual electrodes. The scaling of this structure to hundreds or thousands of electrodes thus seems possible with existing semiconductor fabrication technology.

Candidate linear ion-trap geometries amenable to microfabrication include (i) symmetric high-aspect-ratio multilayer structures with electrodes surrounding the ions20, and (ii) asymmetric planar structures with the ions residing above a planar array of electrodes21. The symmetric geometry demonstrated here may be more difficult to fabricate than the asymmetric geometry, but it is deeper, has better optical access and is less sensitive to electric-field noise from correlated potentials on the electrodes (for example, applied voltage noise or radiofrequency thermal fields common to the electrodes8,9). A symmetric ion trap fabricated from silicon electrodes has been demonstrated22, requiring manual assembly and alignment of separated electrode sections. Here we report an integrated ion trap fashioned from a monolithic microchip that does not require assembly and is therefore suitable for miniaturization and scaling.

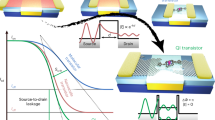

The trap is fabricated from four alternating layers of aluminium gallium arsenide (AlGaAs) and gallium arsenide (GaAs) epitaxially grown on a GaAs substrate, as described in the Methods section and illustrated in Figs 1 and 2. The two GaAs layers (thickness 2.3 μm) are highly doped (∼3×1018 electrons cm−3) and formed into cantilevered electrodes surrounding the free-space trap region. A through-hole is etched in the substrate allowing clear optical access. The electrodes are electrically isolated from each other and from the doped GaAs substrate by the interleaved AlGaAs layers (thickness h=4 μm). These insulating layers are undercut ∼15 μm from the tips of the GaAs cantilevers to shield the trapped ion from stray charge on the exposed insulator. The electrodes are segmented along the axis of the linear trap, as shown in Fig. 1d. Each of the four segments has an axial width of w=130 μm and is separated from adjacent segments by a 25 μm gap. The tip-to-tip separation between opposing cantilevers in the plane of the chip is s=60 μm. A radiofrequency potential is applied to all axial segments of the top GaAs cantilevers on one side of the trap and bottom cantilevers on the opposite side. Static potentials are applied to the other cantilevers, which are held near the radiofrequency ground with on-board filters. Ions can be trapped in one of two zones with appropriate static potentials applied to the four segments. Each of the local trap zones is primarily controlled by three adjacent segments: two end-cap segments surrounding a centre segment nearest to the ion. Mechanical resonances of the cantilevers are expected to occur in the 1–10 MHz range20, with quality factors expected to be of order 103.

a, The structure grown by molecular beam epitaxy consists of alternating GaAs/AlGaAs membrane layers on a GaAs substrate. b, The backside etch removes substrate material for clear optical access through the chip. c, The inductively coupled plasma etch through the membrane creates access to submerged GaAs layers, and gold/germanium bond pads are deposited for electrical contacts to the trap electrodes. d, A further inductively coupled plasma etch through the membrane defines and isolates the cantilevered electrodes, and a hydroflouric acid etch undercuts the AlGaAs insulator material between electrodes.

Top: Ion-trap chip with seven axial segments (28 electrodes) cantilevered over a rectangular through-hole (black). The 28 gold bonding pads are visible as bright squares, along with a single bond pad at the left connecting to the substrate beneath. In the experiment, we trap ions in a similar structure with four segments instead of seven. The tip-to-tip separation of electrodes across the gap is s=60 μm. Bottom: Closeup of a single ion-trap segment, clearly showing the upper and lower GaAs layers separated by h=4 μm. The microscope used was a JEOL 6500.

Ovens containing cadmium oxide are heated to produce a vapour of cadmium in the trapping region with an estimated partial pressure of ∼10−11 torr. We photoionize the cadmium atoms by directing laser pulses (∼100 fs pulse duration at 80 MHz repetition rate) into the trapping region that are tuned near the neutral cadmium 1S0→1P1 transition at 228.5 nm with about 1 mW of average power focused down to a ∼20 μm waist. We selectively load and Doppler laser cool 111Cd+ isotopes by adding a continuous-wave laser red-tuned within one natural linewidth of the 111Cd+ 2S1/2→2P3/2 transition near 214.5 nm (all other Cd+ isotopes are Doppler heated). The Doppler-cooling laser has up to 1 mW of power focused down to a ∼15 μm waist. With both beams aligned, a single 111Cd+ ion can be loaded after a few seconds, after which time the photoionization laser is blocked. The ion is imaged with a charge-coupled-device camera to a nearly diffraction-limited spot with f/2.1 optics, where f is the focal length, as displayed in Fig. 3. Storage lifetimes in excess of 1 h are observed, and a histogram of many loads shows an exponentially distributed confinement time with a mean lifetime of 10 min when the ion is continuously Doppler cooled.

The ion fluoresces from applied laser radiation directed through the chip at a 45∘ angle and nearly resonant with the Cd+ 2S1/2–2P3/2 electronic transition at a wavelength of 214.5 nm. The fluorescence is imaged onto a charge-coupled-device camera with an f/2.1 objective lens, resulting in a near-diffraction-limited spot with ∼1 μm resolution at the ion. The profile of the electrodes is also clearly visible as scattered radiation from a deliberately misaligned laser that strikes the trap electrodes. The vertical gap between the top and bottom set of electrodes is s=60 μm.

We directly measure the frequency of small oscillations of the trapped ion by applying a weak, variable frequency potential to one of the electrodes and observing changes in the ion fluorescence owing to the resonant force while it is continuously laser cooled23. For an applied radiofrequency potential amplitude of V0=8.0 V at a drive frequency of ΩT/2π=15.9 MHz (see Methods section), and static potentials of 1.00 V on the end-cap electrodes and −0.33 V on the centre electrodes, we measure the axial secular frequency to be ωz/2π=1.0 MHz. The measured transverse secular frequencies are ωx/2π=3.3 MHz and ωy/2π=4.3 MHz, indicating a radiofrequency trap stability factor19 of q=0.62. These measurements are consistent with a three-dimensional numerical simulation of the trapping potential, which further indicates that one of the transverse principal axes of the trap is rotated ∼40∘ out of the plane of the chip20.

Microscale ion traps are expected to be particularly sensitive to noisy potentials from the electrodes24,25. Uncontrolled static-offset electric fields from accumulated charge on insulating surfaces or contact potentials can give rise to radiofrequency micromotion22 and they can even destabilize the trap. We suppress micromotion along the direction of the Doppler-cooling beam by applying static offset potentials to electrodes that minimize both the broadening of the atomic fluorescence spectrum (half-width of ∼50 MHz, to be compared with the natural half-width of 30 MHz) and the time correlation of the atomic fluorescence with the radiofrequency trap drive frequency26. We measure heating of the secular motion of the trapped ion by performing optical stimulated Raman spectroscopy on the hyperfine qubit levels of the ion24,25. As described in the Methods section and shown in Fig. 4a, we extract a heating rate along the axial dimension of (1.0±0.5)×106 quanta s−1, at an axial trap frequency of 0.9 MHz. From this, we infer a resonant electric field noise level of about 2×10−8 V2 m−2 Hz−1 (ref. 24). This is in the range of what might be expected on the basis of previous Cd+ ion-trap structures25, assuming a 1/d4 scaling of the noise field with distance d between the ion and the nearest electrode24, and is roughly three orders of magnitude larger than the expected level of thermal electric-field noise from the resistive electrodes. The source of the observed heating is unknown, but may be related to fluctuating ‘patch’ potentials on the electrode surfaces24. The interaction between the ion and driven mechanical motion of the cantilevers may also play a role, and this interesting interface between atomic and solid-state systems will be investigated in the future27,28.

a, Measurement of the motion-sensitive stimulated Raman transition rate between hyperfine states in 111Cd+ versus the delay time τ=0, 0.5 and 1.0 ms before the Raman probe (overlapping data are separated slightly for clarity). The curve is an exponential fit to the data, with the decay constant related to the heating rate. Given the Lamb–Dicke parameter of 0.018 and the trap frequency of 0.9 MHz, this implies a heating rate of  , where

, where  is the average harmonic vibrational index. The error in the heating rate is dominated by systematic uncertainties in relating the Raman transition rate to the heating rate, in addition to the ±1σ error bars shown in the figure, which are due to the uncertainty in the fit of the initial Raman transition data. b, A histogram of the observed survival probability of a single ion in the trap after various times in the dark without Doppler cooling (500 events total). Errors are calculated based on the underlying Bernoulli sampling process. The clear knee in the data indicates that the ion is boiled out of the trap after about 0.1 s.

is the average harmonic vibrational index. The error in the heating rate is dominated by systematic uncertainties in relating the Raman transition rate to the heating rate, in addition to the ±1σ error bars shown in the figure, which are due to the uncertainty in the fit of the initial Raman transition data. b, A histogram of the observed survival probability of a single ion in the trap after various times in the dark without Doppler cooling (500 events total). Errors are calculated based on the underlying Bernoulli sampling process. The clear knee in the data indicates that the ion is boiled out of the trap after about 0.1 s.

To reliably load, store and shuttle ions, a microscale trap must have sufficient depth, defined as the amount of energy needed for an ion to escape. Numerical simulations indicate that the trap depth is approximately Δ∼0.08 eV for the above conditions, limited in a direction inclined by ∼37∘ out of the plane of the chip. This relatively shallow depth, of the order of the room temperature (0.025 eV), corroborates further observations of the chip trap behaviour: the mean storage time of 10 min is consistent with the expected time between elastic collisions27 with the room-temperature background gas (primarily Cd), and we were never able to load two ions in the trap simultaneously. Without continuous Doppler cooling, the ion is observed to boil out of the trap within the dark time, where the delay time τ=0.1 s (Fig. 4b), implying an average heating rate Δ/τ that is approximately 100 times higher than the heating rate measured near the bottom of the trap reported above29. All of these observations contrast sharply with the behaviour of larger (millimetre scale) Cd+ trap structures in our laboratory with depths greater than 1 eV and similar background pressures, where the storage lifetime is typically measured in days (even without laser cooling), and multiple ions are easily loaded.

The transverse depth of a linear radiofrequency ion trap scales as D=σ q e V0/8, where q is the stability factor, e is the charge of the ion and σ≤1 is a geometrical shape factor. If we assume that the radiofrequency potential amplitude is limited by V0∝Emaxl, with Emax the maximum electric field (given by electrical breakdown, field emission or other limits) and l the limiting dimension of the trap electrodes, then the trap depth scales as D∝l (ref. 19). In this scaling law, we assume q is fixed and all dimensions are scaled isotropically (σ=constant). However, in the symmetric high-aspect-ratio geometry, any reduction in size will primarily be in the plane of the chip (shrinking dimensions s and w in Fig. 1d, but not the layer separation h). In this case, the depth D≈σ(s)q e Emaxh/8 should actually improve as s becomes smaller through the geometrical shape factor σ(s)∝s−0.44 (for aspect ratios 1<s/h<20)20.

Another concern in the operation of ion microtraps is radiofrequency power dissipation, which limits the applied V0 and ΩT. In general, the power dissipated in a radiofrequency ion trap is given by PD=V02C ΩT/(2Q), where the quality factor Q describes the radiofrequency losses in the trap structure and is given by 1/Q=RSC ΩT+tanδ. Here, C is the net capacitance and RS the net series resistance of the radiofrequency electrodes, and tanδ is the loss tangent of the insulating layer. In the experiment, we measure Q∼55 from the radiofrequency resonance shape. This is consistent with a direct electrical measurement of the resistance between the base and the tip of a single cantilever of 20 Ω (corresponding to RS∼5 Ω), a measurement of C∼34 pF and a negligible loss tangent. For the radiofrequency amplitude and frequency listed above, the power dissipated in the trap is expected to be about 2 mW, or 0.5 mW per cantilever pair. As the geometry is scaled down in the chip plane (fixing h,q and V0 as above), we expect that the dissipated power per unit area of the radiofrequency electrode should grow as I0∝s−2.2 (for aspect ratios 1<s/h<20)20.

In addition to stable trapping of individual ions in each of the two trapping zones, ions are shuttled between zones30 by smoothly changing the voltages from trapping in one region to trapping in the adjacent region ∼150 μm away. This has been demonstrated starting in either trap zone with shuttle times as fast as 2.5 ms, with the speed limited by low-pass filters installed on the chip.

Given these promising results for the GaAs microtrap architecture, we intend to fabricate different structures that will feature larger trap depths and may show lower heating rates by altering the electrode dimensions in the plane of the chip and increasing the separation between layers. We will also explore the fabrication of ‘cross’ and ‘tee’ junctions in the GaAs architecture for more advanced shuttling experiments, perhaps requiring a three-layer geometry25. This symmetric high-aspect-ratio geometry could also accommodate other materials such as silicon, which may allow higher voltages to be applied with less radiofrequency dissipation. Ultimately, a hybrid geometry combining the symmetric high-aspect-ratio and asymmetric planar trap geometries might be considered. Here, the deeper symmetric cantilevered electrode zones might be used for loading and entangling zones where high trap strength and depth are required, and the planar trap zones might be used for complex shuttling operations.

Methods

Fabrication

The wafer (Fig. 1a) consists of a doped substrate on top of which are four layers grown by molecular beam epitaxy. Directly above the substrate is a 4 μm layer of Al0.7Ga0.3As, chosen for its insulating properties and selective etching versus GaAs. On top of it is a 2.3 μm layer of silicon-doped (3×1018 electrons cm−3) GaAs, 4 μm of Al0.7Ga0.3As and 2.3 μm of doped GaAs. As shown in Fig. 1, a series of dry and wet etch procedures define the cantilevered GaAs electrodes. The final step undercuts the Al0.7Ga0.3As from the edges of the GaAs cantilever by about 15 μm to shield the trapped ion from the exposed insulator. Figure 2 shows a scanning electron micrograph of the final structure.

We attach the GaAs ion-trap chip to a ceramic chip carrier and attach 25-μm-diameter gold wires from the bond pads on the trap to the chip carrier, with a single wire connecting radiofrequency electrodes and individual wires going from the static-electrode bond pads to the chip carrier electrodes. The static electrodes are shunted to ground through 1,000 pF surface mount capacitors attached to the chip carrier, and our measurements show that the induced radiofrequency potential on the static electrodes is reduced to less than 1% of the applied radiofrequency potential. The chip carrier is then plugged into an ultra-high-vacuum-compatible socket that is permanently connected in the vacuum chamber. This arrangement allows for fast turnaround time; replacing an ion trap does not involve changing any other components inside the vacuum chamber.

Radiofrequency delivery and breakdown

We apply radiofrequency potentials to the trap using a helical resonator of unloaded quality factor Q≈500 and self-resonant frequency 54.9 MHz. When a capacitive coupler is impedance matched to the resonator–trap system, the resonant frequency falls to 15.9 MHz, and the unloaded quality factor of the system drops to ∼50. Breakdown of the AlGaAs layer seems to limit the amount of radiofrequency voltage that can be applied to the trap. We have applied a static potential as high as ∼70 V between top and bottom cantilevers on a separate trap sample without breakdown, and a radiofrequency potential amplitude as high as V0=11 V at 14.75 MHz before breakdown. We also observe nonlinear current–voltage behaviour across the GaAs electrodes, where the measured current depends on the polarity of the applied voltage and even the level of room lights at particular voltages. However, none of these effects were measurable at applied potentials below ∼40 V and are thus not expected to play a role in the operation of the trap.

Measurement of heating using Raman spectroscopy

Heating of the secular harmonic motion of the trapped ion is measured by driving motion-sensitive stimulated Raman transitions between hyperfine ground states in the 111Cd+ ion. A pair of laser beams each detuned ∼70 GHz from the 2S1/2–2P3/2 transition are directed onto the ion, with an optical beat note near the 14.53 GHz atomic hyperfine splitting. The two Raman beams have a 7∘ angular separation, with the wavevector difference oriented 45∘ from the axis of the trap (axial Lamb–Dicke parameter of η≈0.018 for a trap frequency of 0.9 MHz). By adding varying delays τ after Doppler cooling but before the Raman probe, the increase of motional energy of the ion is reflected by the suppression of the Raman carrier transition rate through the Debye–Waller effect27. Assuming a thermal state of motion with average harmonic vibrational index  , the transition rate is proportional to

, the transition rate is proportional to  in the Lamb–Dicke limit where

in the Lamb–Dicke limit where  . Here we neglect the Debye–Waller factor from the more tightly confined transverse motion, expected to be negligible compared with that of axial motion. After the delay τ, the Raman transition rate is measured by interrogating the hyperfine level of the ion3 after a time t of exposure to the Raman probe, and fitting the initial development of the transition probability as a quadratic in time: P(t)=sin2(R t/2)∼(R t/2)2. We find that the Raman carrier transition rate R decreases by approximately 25% after a delay of τ=0.5 ms (with a negligible effect of heating on the rate during the 10 μs Raman probe), as shown in Fig. 4a. This corresponds to an axial heating rate of

. Here we neglect the Debye–Waller factor from the more tightly confined transverse motion, expected to be negligible compared with that of axial motion. After the delay τ, the Raman transition rate is measured by interrogating the hyperfine level of the ion3 after a time t of exposure to the Raman probe, and fitting the initial development of the transition probability as a quadratic in time: P(t)=sin2(R t/2)∼(R t/2)2. We find that the Raman carrier transition rate R decreases by approximately 25% after a delay of τ=0.5 ms (with a negligible effect of heating on the rate during the 10 μs Raman probe), as shown in Fig. 4a. This corresponds to an axial heating rate of  . The quoted error is dominated by the uncertainty in the absolute value of

. The quoted error is dominated by the uncertainty in the absolute value of  that relates the Raman transition rate to the heating rate, in addition to the statistical uncertainty in the data.

that relates the Raman transition rate to the heating rate, in addition to the statistical uncertainty in the data.

References

Metcalf, H. J. & van der Straten, P. Laser Cooling and Trapping (Springer, New York, 1999).

Leggett, A. J. Bose-Einstein condensation in the alkali gases: Some fundamental concepts. Rev. Mod. Phys. 73, 307–356 (2001).

Leibfried, D., Blatt, R., Monroe, C. & Wineland, D. J. Quantum dynamics of single trapped ions. Rev. Mod. Phys. 75, 281–324 (2003).

Fortagh, J. & Zimmerman, C. Towards atom chips. Science 307, 860–861 (2005).

Ott, H., Fortagh, J., Schlotterbeck, G., Grossmann, A. & Zimmermann, C. Bose-Einstein condensation in a surface microtrap. Phys. Rev. Lett. 87, 230401 (2001).

Hänsel, W., Hommelhoff, P., Hänsch, T. W. & Reichel, J. Bose-Einstein condensation in a microelectronic chip. Nature 413, 498–501 (2001).

Folman, R., Krueger, P., Schmiedmayer, J., Denschlag, J. & Henkel, C. Microscopic atom optics. Adv. At. Mol. Opt. Phys. 48, 263–356 (2002).

Orient, O. J., Chutjian, A. & Garkanian, V. Miniature, high-resolution, quadrupole mass-spectrometer. Rev. Sci. Instrum. 68, 1393–1397 (1997).

Knappe, S. et al. A microfabricated atomic clock. Appl. Phys. Lett. 85, 1460–1462 (2004).

Cirac, J. I. & Zoller, P. A scalable quantum computer with ions in an array of microtraps. Nature 404, 579–581 (2000).

Kielpinski, D., Monroe, C. & Wineland, D. J. Architecture for a large scale ion-trap quantum computer. Nature 417, 709–711 (2002).

Nielsen, M. A. & Chuang, I. L. Quantum Computation and Quantum Information (Cambridge Univ. Press, Cambridge, 2000).

Cirac, J. I. & Zoller, P. Quantum computations with cold trapped ions. Phys. Rev. Lett. 74, 4091–4094 (1995).

Pellizzari, T., Gardiner, S. A., Cirac, J. I. & Zoller, P. Decoherence, continuous observation, and quantum computing: A cavity QED model. Phys. Rev. Lett. 75, 3788–3791 (1995).

Duan, L.-M., Blinov, B. B., Moehring, D. L. & Monroe, C. Scalable trapped ion quantum computation with a probabilistic ion-photon mapping. Quantum Inf. Comput. 4, 165–173 (2004).

Riebe, M. et al. Deterministic quantum teleportation with atoms. Nature 429, 734–737 (2004).

Barrett, M. D. et al. Deterministic quantum teleportation of atomic qubits. Nature 429, 737–739 (2004).

Chiaverini, J. et al. Realization of quantum error correction. Nature 432, 602–605 (2004).

Dehmelt, H. G. Radiofrequency spectroscopy of stored ions I: Storage. Adv. At. Mol. Phys. 3, 53–73 (1967).

Madsen, M. J., Hensinger, W. K., Stick, D., Rabchuk, J. A. & Monroe, C. Planar ion trap geometry for microfabrication. Appl. Phys. B 78, 639–651 (2004).

Chiaverini, J. et al. Surface-electrode architecture for ion-trap quantum information processing. Quantum Inf. Comput. 5, 419–439 (2005).

Wineland, D. J. et al. Quantum control, quantum information processing, and quantum-limited metrology with trapped ions. Proc. ICOLS (in the press); preprint at < http://arxiv.org/abs/quant-ph/0508025> (2005).

Jefferts, S., Monroe, C., Bell, E. & Wineland, D. J. A coaxial-resonator driven rf (Paul) ion trap for strong confinement. Phys. Rev. A 51, 3112–3116 (1995).

Turchette, Q. A. et al. Heating of trapped ions from the quantum ground state. Phys. Rev. A 61, 063418 (2000).

Deslauriers, L. et al. Zero-point cooling and heating of trapped Cd+ ions. Phys. Rev. A 70, 043408 (2004).

Berkeland, D. J., Miller, J. D., Bergquist, J. C., Itano, W. M. & Wineland, D. J. Minimization of ion micromotion in a Paul trap. J. Appl. Phys. 83, 5025–5033 (1998).

Wineland, D. J. et al. Experimental issues in coherent quantum-state manipulation of trapped atomic ions. J. Res. Natl Inst. Stand. Technol. 103, 259–328 (1998).

Hensinger, W. K. et al. Ion trap transducers for quantum electromechanical oscillators. Phys. Rev. A 72, 041405(R) (2005).

Gehm, M. E., O’Hara, K. M., Savard, T. A. & Thomas, J. E. Dynamics of noise-induced heating in atom traps. Phys. Rev. A 58, 3914–3921 (1998).

Rowe, M. A. et al. Transport of quantum states and separation of ions in a dual rf ion trap. Quantum Inf. Comput. 2, 257–271 (2002).

Acknowledgements

We acknowledge useful discussions with J. A. Rabchuk, S. Horst, T. Olver, K. Eng, P. Lee, P. Haljan, K.-A. Brickman, L. Deslauriers and M. Acton. This work was supported by the US Advanced Research and Development Activity and National Security Agency under Army Research Office contract W911NF-04-1-0234, and the National Science Foundation Information Technology Research Program.

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

Competing interests

The authors declare no competing financial interests.

Rights and permissions

About this article

Cite this article

Stick, D., Hensinger, W., Olmschenk, S. et al. Ion trap in a semiconductor chip. Nature Phys 2, 36–39 (2006). https://doi.org/10.1038/nphys171

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1038/nphys171

This article is cited by

-

High-fidelity trapped-ion qubit operations with scalable photonic modulators

npj Quantum Information (2023)

-

Noisy intermediate-scale quantum computers

Frontiers of Physics (2023)

-

New material platform for superconducting transmon qubits with coherence times exceeding 0.3 milliseconds

Nature Communications (2021)

-

Engineering of microfabricated ion traps and integration of advanced on-chip features

Nature Reviews Physics (2020)

-

Grating chips for quantum technologies

Scientific Reports (2017)